## **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

#### DEPARTMENT OF MICROELECTRONICS

ÚSTAV MIKROELEKTRONIKY

## **CONTROL UNIT FOR CUBESAT**

ŘÍDICÍ JEDNOTKA PRO CUBESAT

#### **MASTER'S THESIS**

DIPLOMOVÁ PRÁCE

**AUTHOR** AUTOR PRÁCE Bc. Jan Horký

**SUPERVISOR**

Ing. Michal Kubíček, Ph.D.

**VEDOUCÍ PRÁCE**

**BRNO 2017**

## Diplomová práce

magisterský navazující studijní obor **Mikroelektronika** Ústav mikroelektroniky

Student: Bc. Jan Horký ID: 146830

Ročník: 2 Akademický rok: 2016/17

NÁZEV TÉMATU:

#### Řídicí jednotka pro CubeSat

#### POKYNY PRO VYPRACOVÁNÍ:

Ve spolupráci s firmou CSRC, s.r.o. navrhněte koncepci řídicí jednotky pro CubeSat s obvodem FPGA a vhodnými pamětmi. Jednotka bude umožňovat řídit CubeSat a zároveň zpracovávat uživatelská data. Jednotku vybavte základní sadou senzorů pro monitorování jejího stavu.

Ověřte funkčnost jednotky a vytvořte digitální design pro FPGA, který využije všechny její funkce.

#### DOPORUČENÁ LITERATURA:

[1] FUKÁTKO, Tomáš. Detekce a měření různých druhů záření. Praha: BEN - technická literatura, 2007. Senzory neelektrických veličin. ISBN 978-80-7300-193-3.

[2] ŠŤASTNÝ, Jakub. FPGA prakticky: realizace číslicových systémů pro programovatelná hradlová pole. Praha: BEN - technická literatura, 2010. ISBN 978-80-7300-261-9.

Termín zadání: 6.2.2017 Termín odevzdání: 25.5.2017

Vedoucí práce: Ing. Michal Kubíček, Ph.D.

Konzultant:

doc. Ing. Lukáš Fujcik, Ph.D. předseda oborové rady

#### UPOZORNĚNÍ:

Autor diplomové práce nesmí při vytváření diplomové práce porušit autorská práva třetích osob, zejména nesmí zasahovat nedovoleným způsobem do cizích autorských práv osobnostních a musí si být plně vědom následků porušení ustanovení § 11 a následujících autorského zákona č. 121/2000 Sb., včetně možných trestněprávních důsledků vyplývajících z ustanovení části druhé, hlavy VI. díl 4 Trestního zákoníku č.40/2009 Sb.

#### **Master's Thesis**

Master's study field **Microelectronics**Department of Microelectronics

Student: Bc. Jan Horký ID: 146830

Year of study:

Academic year: 2016/17

**TITLE OF THESIS:**

#### Control unit for CubeSat

#### INSTRUCTION:

Design an FPGA-based CubeSat control unit in cooperation with CSRC Company. The control unit will be equipped with a suitable set of memories and will enable both CubeSat control and user data processing. Equip the control unit with a set of basic sensors for monitoring of its status.

Verify the design functionality and prepare an FPGA configuration that will test all the functions of the unit.

The project will be done in cooperation with CSRC, spol. s r.o.

#### **RECOMMENDED LITERATURE:**

[1] FUKÁTKO, Tomáš. Detekce a měření různých druhů záření. Praha: BEN - technická literatura, 2007. Senzory neelektrických veličin. ISBN 978-80-7300-193-3.

[2] ŠŤASTNÝ, Jakub. FPGA prakticky: realizace číslicových systémů pro programovatelná hradlová pole. Praha: BEN - technická literatura, 2010. ISBN 978-80-7300-261-9.

Date of project specification:

Deadline for submission: 25.5.2017

Leader: Ing. Michal Kubíček, Ph.D.

Consultant:

doc. Ing. Lukáš Fujcik, Ph.D. Subject Council chairman

#### WARNING:

The author of the Master's Thesis claims that by creating this thesis he/she did not infringe the rights of third persons and the personal and/or property rights of third persons were not subjected to derogatory treatment. The author is fully aware of the legal consequences of an infringement of provisions as per Section 11 and following of Act No 121/2000 Coll. on copyright and rights related to copyright and on amendments to some other laws (the Copyright Act) in the wording of subsequent directives including the possible criminal consequences as resulting from provisions of Part 2, Chapter VI, Article 4 of Criminal Code 40/2009 Coll.

#### **ABSTRAKT**

Cílem práce je návrh univerzální řídicí jednotky pro CubeSat založené na obvodu FPGA Taková jednotka doposud nebyla komerčně dostupná a navržená jednotka má tak dobrý potenciál zaplnit příslušné místo na trhu komponent pro CubeSat. Celá jednotka je navržena z komerčně dostupných komponent. Návrh jednotky je proveden tak, aby umožnil její funkci ve vesmírném prostředí. Stav konfigurace FPGA je pravidelně kontrolován a v případě zjištěné chyby dochází automaticky k rekonfiguraci FPGA a návratu jednotky do výchozího stavu. Jednotka obsahuje sadu senzorů, které monitorují její stav a v případě potřeby je možné na základě jejich výstupů provést opatření z hlediska ochrany funkce jednotky. Dvě paměti MRAM umožňují uložení tovární a uživatelské konfigurace FPGA, mezi kterými dochází k automatickému přepnutí na základě korektnosti uživatelské konfigurace.

#### KLÍČOVÁ SLOVA

Vesmír, CubeSat, Řídicí jednotka, Radiace, FPGA

#### **ABSTRACT**

The aim of the thesis is a design of a CubeSat control unit. Similar unit could not be found on the market and proposed unit has a potential to fill the gap. The board is composed of commercial parts yet reliable in the space environment. Because of its benefits, an FPGA was selected as the core of the board. The FPGA is periodically checked for errors and reset to default state if an error is found. The unit has various sensors to monitor its condition and can do necessary measures. Two MRAMs allow store golden bitstream and upload new bitstream in flight which are switched based on proper operation.

#### **KEYWORDS**

Space, CubeSat, Control Unit, Radiation, FPGA

Faculty of Electrical Engineering and Communication Brno University of Technology Technicka 12, CZ-61600 Brno, Czechia http://www.six.feec.vutbr.cz

Experimentální část této diplomové práce byla podpořena výzkumnou infrastrukturou vybudovanou v rámci projektu CZ.1.05/2.1.00/03.0072

Centrum senzorických, informačních a komunikačních systémů (SIX)

operačního programu Výzkum a vývoj pro inovace.

#### **PROHLÁŠENÍ**

Prohlašuji, že svou diplomovou práci na téma Řídicí jednotka pro CubeSat jsem vypracoval samostatně pod vedením vedoucího diplomové práce a s použitím odborné literatury a dalších informačních zdrojů, které jsou všechny citovány v práci a uvedeny v seznamu literatury na konci práce.

Jako autor uvedené diplomové práce dále prohlašuji, že v souvislosti s vytvořením této diplomové práce jsem neporušil autorská práva třetích osob, zejména jsem nezasáhl nedovoleným způsobem do cizích autorských práv osobnostních a/nebo majetkových a jsem si plně vědom následků porušení ustanovení § 11 a následujících zákona č. 121/2000 Sb., o právu autorském, o právech souvisejících s právem autorským a o změně některých zákonů (autorský zákon), ve znění pozdějších předpisů, včetně možných trestněprávních důsledků vyplývajících z ustanovení části druhé, hlavy VI. díl 4 Trestního zákoníku č. 40/2009 Sb.

| V Brně dne |                 |

|------------|-----------------|

|            | (podpis autora) |

### PODĚKOVÁNÍ

Děkuji vedoucímu diplomové práce Ing. Michalu Kubíčkovi, Ph.D. za účinnou metodickou, pedagogickou a odbornou pomoc a další cenné rady nejen při zpracování mé diplomové práce.

Děkuji Ing. Martinu Adámkovi, Ph.D. za pomoc a rady ohledně osazení desky.

Děkuji Ing. Jiřímu Starému, Ph.D. za přístup do laboratoře a rady ohledně osazení desky.

## **Contents**

| Introdu    | ction                                         | 11 |

|------------|-----------------------------------------------|----|

| 1. Sp      | ace environment                               | 12 |

| 1.1.       | Neutral Atmosphere                            | 12 |

| 1.2.       | Electric and Magnetic Fields                  | 12 |

| 1.3.       | Ultraviolet Radiation                         | 12 |

| 1.4.       | Infrared                                      | 13 |

| 1.5.       | Solar Wind Plasma                             | 13 |

| 1.6.       | Ionospheric Plasma                            | 13 |

| 1.7.       | Aurora Plasma                                 | 14 |

| 1.8.       | Trapped Radiation                             | 14 |

| 1.9.       | Galactic Cosmic Rays                          | 15 |

| 1.10.      | Solar Proton Events                           | 15 |

| 1.11.      | Meteoroids and space debris                   | 15 |

| 1.12.      | Dust                                          | 15 |

| 1.13.      | Space Launchers - vibrations and acceleration | 16 |

| 1.14.      | Orbits                                        | 17 |

| 2. Ra      | diation effects on electronics                | 18 |

| 3. Cu      | ıbeSat                                        | 21 |

| 3.1.       | Requirements                                  | 23 |

| 4. De      | esign of the control unit                     | 24 |

| 4.1.       | Design options and requirements               | 24 |

| 4.1        | 1.1. Expected environmental conditions        | 24 |

| 4.1        | 1.2. Shielding                                | 27 |

| 4.1        | 1.3. Positioning and trajectory               | 27 |

| 4.1        | 1.4. Materials                                | 27 |

| 4.1        | 1.5. Electronic parts selection               | 27 |

| 4.1        | 1.6. Circuit design                           | 27 |

| <b>4</b> 1 | 7 PCB layout                                  | 27 |

| 4.2.   | Co    | ntrol unit selection        | . 28 |

|--------|-------|-----------------------------|------|

| 4.3.   | Xil   | inx FPGA selection          | . 31 |

| 4.3    | 3.1.  | Power consumption           | . 31 |

| 4.3    | 3.2.  | Memory                      | . 32 |

| 4.3    | 3.3.  | FPGA selection              | . 33 |

| 4.4.   | Enl   | nanced products             | . 33 |

| 4.5.   | Cir   | cuit design                 | . 34 |

| 4.5    | 5.1.  | FPGA configuration circuit  | . 36 |

| 4.5    | 5.2.  | Power supply                | . 39 |

| 4.5    | 5.3.  | Latch-up protection         | .41  |

| 4.5    | 5.4.  | Capacitors for supply rails | . 44 |

| 4.5    | 5.5.  | Clock generator             | . 44 |

| 4.5    | 5.6.  | Data storage                | . 44 |

| 4.5    | 5.7.  | AD converter                | . 45 |

| 5. PC  | B de  | esign                       | . 47 |

| 6. Pri | ce    |                             | . 48 |

| 7. Di  | gital | design                      | . 48 |

| 7.1.   | ТО    | P Module                    | . 48 |

| 7.2.   | MF    | RAM Controller              | . 48 |

| 7.3.   | AD    | C Controller                | . 50 |

| 7.3    | 3.1.  | Temperature calculation     | . 51 |

| 7.3    | 3.2.  | Current calculation         | . 52 |

| 7.3    | 3.3.  | Further improvements        | . 52 |

| 7.4.   | SD    | Card Controller             | . 52 |

| 7.4    | .1.   | Interface Controller        | . 53 |

| 7.5.   | UA    | RT Controller               | . 53 |

| 7.6.   | Des   | sign statistics             | . 54 |

| 7.7.   | Hig   | gh load design              | . 54 |

| 8. Me  | easur | ement results               | . 56 |

| 0 1    | Dox   | wer                         | . 56 |

| 8.1.1.        | Power consumption              | 56 |

|---------------|--------------------------------|----|

| 8.1.2.        | Power consumption at high load | 56 |

| 8.1.3.        | FPGA's power inputs            | 57 |

| 8.1.4.        | Conclusion                     | 59 |

| 8.2. Co       | onfiguration circuit           | 60 |

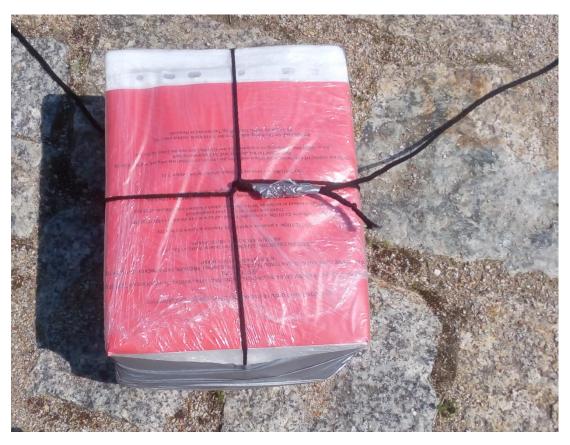

| 9. Strato     | spheric test flight            | 61 |

| 9.1. Pr       | reparations                    | 61 |

| 9.2. R        | esults                         | 62 |

| 10. Sum       | ımary                          | 63 |

| Bibliograph   | hy                             | 64 |

| List of acro  | onyms                          | 68 |

| List of figu  | res                            | 69 |

| List of table | es                             | 71 |

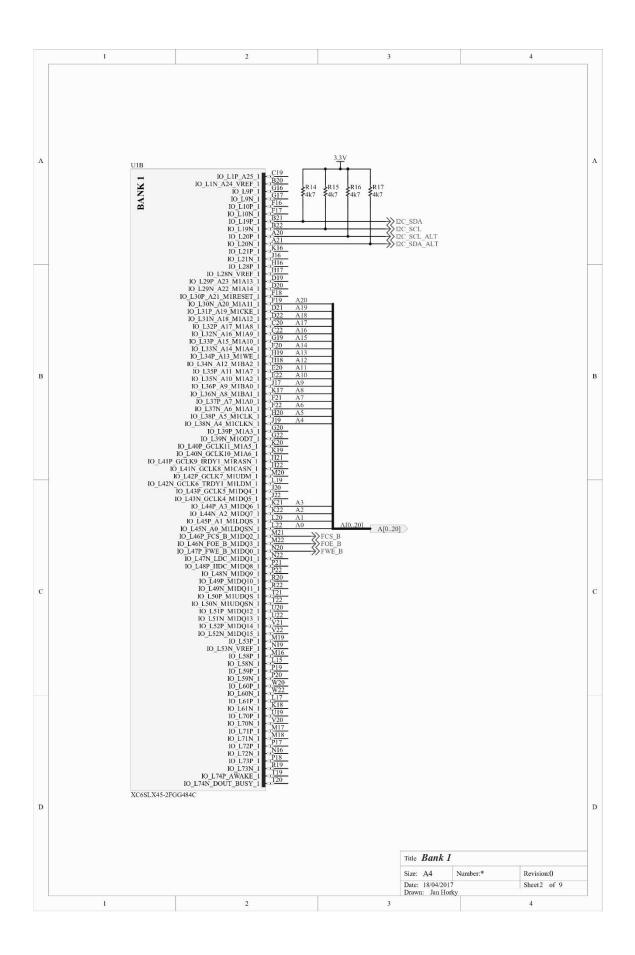

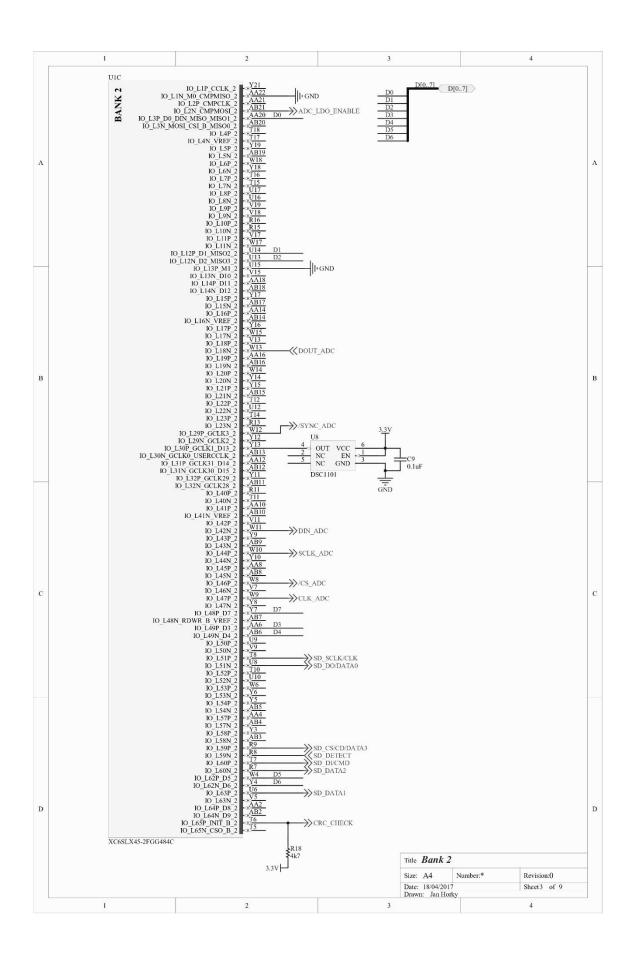

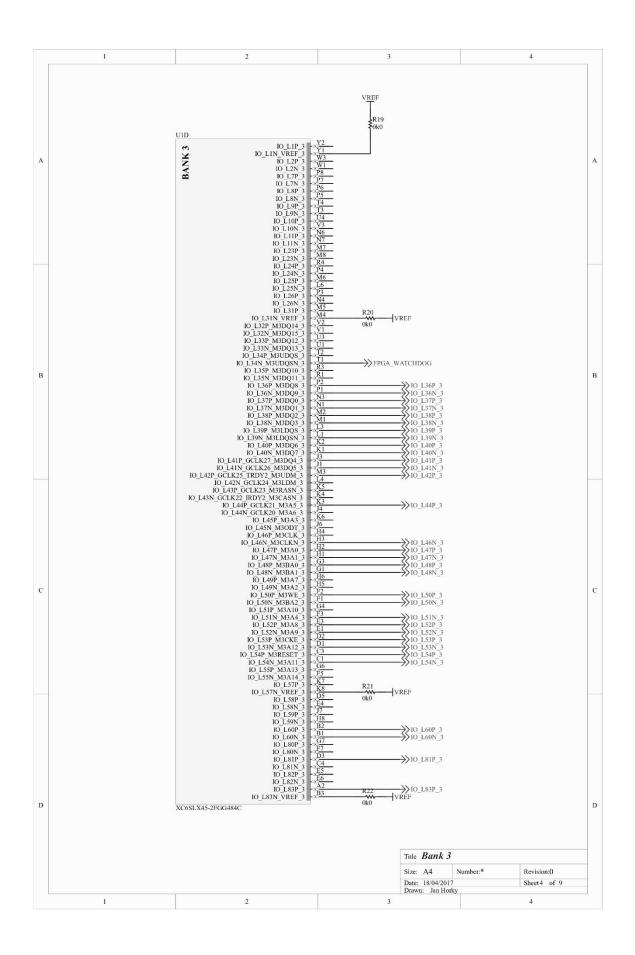

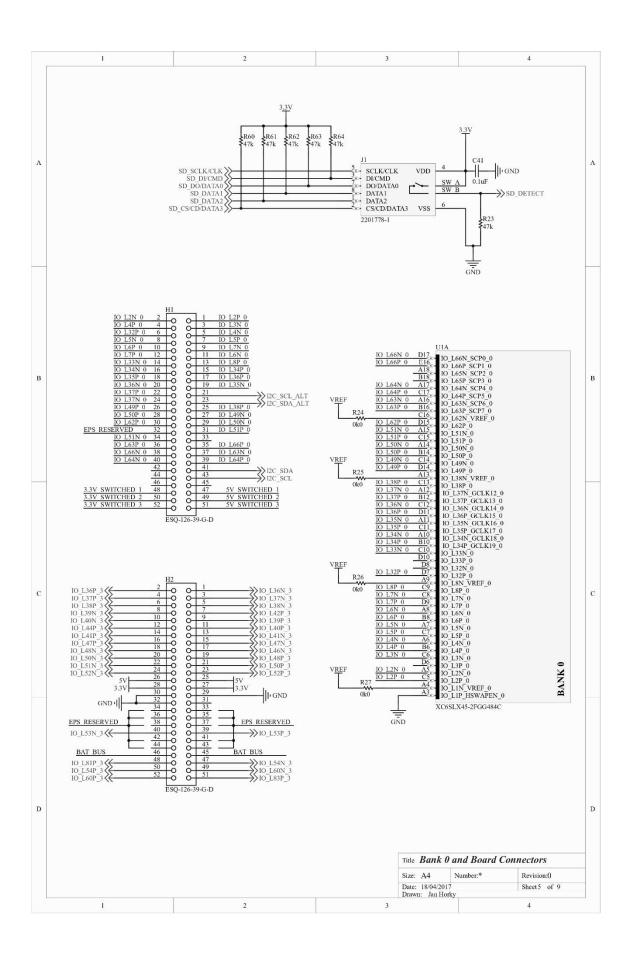

| Annex A.      | The control unit schematics    | 72 |

| Annex B. F    | PCB layout                     | 81 |

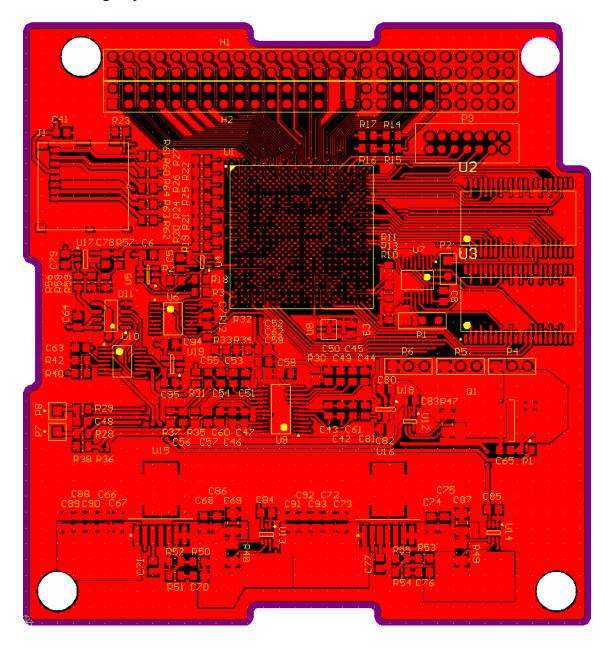

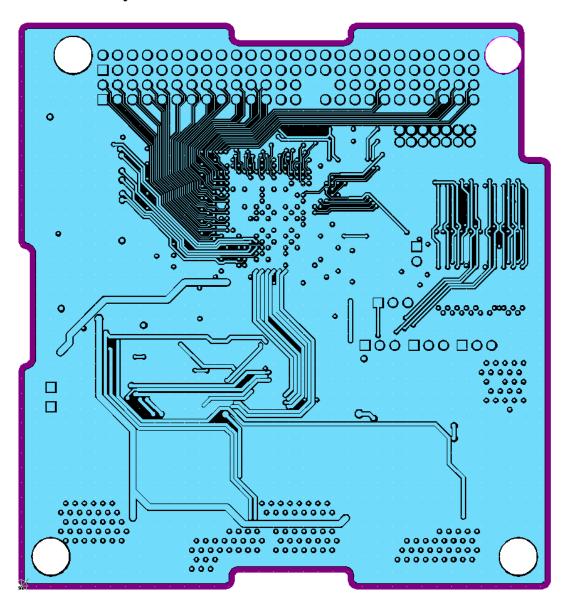

| В.1. Тор      | layer                          | 81 |

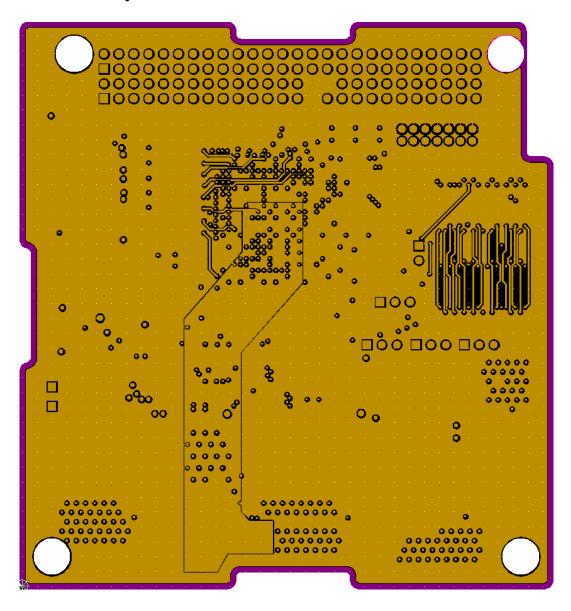

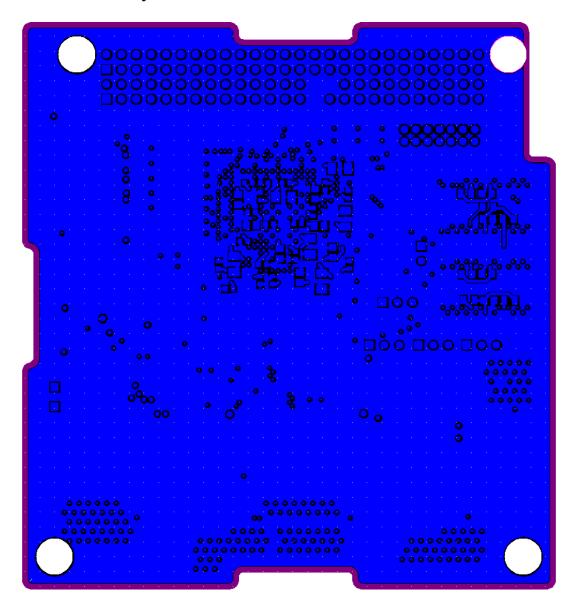

| B.2. Inne     | er layer 1                     | 82 |

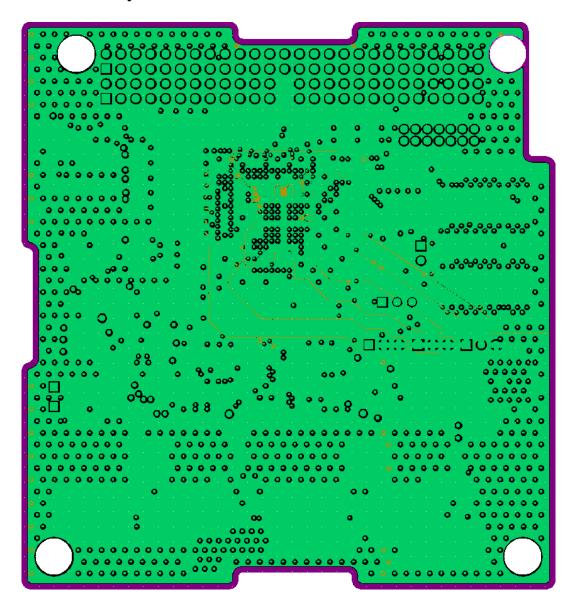

| B.3. Inne     | er layer 2                     | 83 |

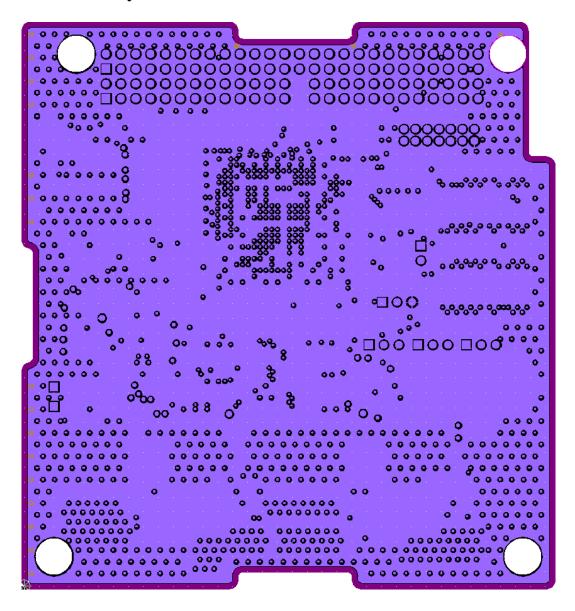

| B.4. Inne     | er layer 3                     | 84 |

| B.5. Inne     | er layer 4                     | 85 |

| B.6. Bot      | tom layer                      | 86 |

| Annex C. I    | Bill of materials              | 87 |

| Annex D. S    | Stratospheric flight           | 92 |

## Introduction

Since the beginning of the space exploration, space satellites had been objects of large volume and weight to be able to do all experiments and measurements. That made the cost of a satellite and its launch so expensive that only governmental space agencies could afford it.

Ongoing researches and new inventions in fields like electronics, mechatronics, and mechanics have been making devices smaller, cheaper and smarter. The computing power of processors, new types of algorithms and programming languages allowed to reduce the number of discrete parts and implement them as software. Due to the progress, satellites can be smaller, lighter and perform more tasks and experiments.

The idea of CubeSat was developed at the California Polytechnic State University together with Stanford University to teach students how to develop, design and manufacture space satellites. CubeSat were defined as U-class spacecraft with dimensions of 10x10x10 cm and weight up to 1.33 kg per unit. Since then, tens of universities have joined the international collaboration, and many private companies have been designing and manufacturing CubeSat or its parts. Specialized internet shops, selling parts for CubeSat were also founded.

Because of its small volume and weight, a CubeSat is significantly specialized, mostly for only one experiment. In most of the cases, there is not a need for high computing power. Therefore most of the control units use microcontrollers as CPU. If there is a need for faster signal processing, parallel processes or high computing power, a customer has to develop suitable board on his own as such types are not available on the market. That significantly increases overall cost and development time.

The aim of this thesis is to design and test control unit which can fill this gap on the market. The board is designed to be reliable in the harsh space environment and is designed according to European Space Agency's (ESA) and National Aeronautics and Space Administration's (NASA) standards. The board is compatible with boards of other manufacturers and CubeSat specification.

## 1. Space environment

As the complexity of space systems is continuously growing, an understanding of space environment is necessary to reduce failure possibility. The neutral atmosphere is responsible for drag, glow and oxygen erosion. Magnetic and electric fields are responsible for magnetic torques and electric fields. The UV/EUV radiation creates long-term changes in material surface properties. The IR environment is the main cause of thermal effects. Also, four charged-particle environments are discussed in the chapter: the interplanetary environment, the plasmasphere/ionosphere, the plasmasheet and the radiation belts. Synthetic space debris, meteoroids, and surface dust are also in this chapter [1].

#### 1.1. Neutral Atmosphere

This environment is present at low altitudes around most of the planets. The atmosphere creates atmospheric drag, which influences a spacecraft's trajectory. A spacecraft has to periodically adjust its orbit, otherwise, it eventually crashes or burns in the atmosphere [1].

Orbital velocities and interactions with neutral particles can induce chemical interactions such as oxygen erosion (a serious problem for Kapton, silver, osmium and other materials) [1].

#### 1.2. Electric and Magnetic Fields

Electric and magnetic fields exist around most bodies in space. Magnetic fields range from tenths of gauss near the Earth, about 4-8 gauss at Jupiter and few nanotesla in the solar wind. Electric fields range from 0.3 V/m close to the Earth to 60 V/m near Jupiter. Spacecraft surface charging potentials can reach 20 kV at the Earth. Arcing can occur between charged surfaces with potential differences as low as 200 V [1].

#### 1.3. Ultraviolet Radiation

Ultraviolet radiation is important for spacecraft as it can change the surface chemistry of materials and causes photoelectron emission. The ultraviolet radiation is the continuum and line spectrum between 10-4000~Å. The solar energy in this range is between  $10^7$  and  $10^{10}$  photons/cm<sup>2</sup>s below 1000~Å and rises exponentially to  $10^{16}$  protons/cm<sup>2</sup>s between 1000~and~10000~Å [1].

#### 1.4. Infrared

The infrared spectrum has wavelengths from 0.7 to  $7 \mu m$  and is produced by the Sun. Other sources can be atmospheric glow, radiation from other planets and reflected sunlight. This environment has major thermal effects on spacecraft [1].

#### 1.5. Solar Wind Plasma

The solar wind is a plasma, consisting of electrons, protons, and alpha particles, produced by the Sun. Densities and energies range from 50 particles/cm<sup>-3</sup> (40 eV for ions, 65 eV for electrons) near Mercury to 0.2 particles/cm<sup>-3</sup> (1 eV for ions, 10 eV for electrons) at Jupiter. The solar wind must be considered for missions near the Sun and for plasma sensors. This plasma can also induce surface potentials of 10 V, but potentials up to 100 V were also measured [1].

#### 1.6. Ionospheric Plasma

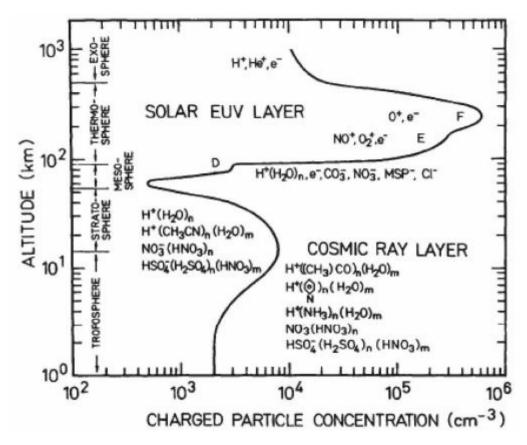

The ionosphere is a component of a planetary atmosphere. For the Earth, the composition varies from  $O^+$  dominated (density of about  $10^6 \, \mathrm{cm}^{-3}$ ) environment at altitudes from 200 to 500 km, to  $H^+$  dominated (density from  $10^5$  to  $10^3 \, \mathrm{cm}^{-3}$ ) for higher altitudes. The concentration is illustrated in Figure 1. A spacecraft's velocity relative to the plasma can create a charged wake structure around the spacecraft altering the currents and electromagnetic fields around it. Ionospheres affect mainly radio wave propagation and spacecraft communications [1].

Figure 1: Concentration of charged particles in the ionosphere [2]

#### 1.7. Aurora Plasma

Above the ionosphere, there is a plasma of lower density than in the ionosphere, but also of much higher energy. Charged particles can generate structures called auroras. Near the Earth's geostationary orbit, densities are on the order of about 1 cm<sup>-3</sup> and their energies are in order of tens keV. The plasma can rise surface potentials to 20 kV or more [1].

#### 1.8. Trapped Radiation

One of the effects of the Earth's magnetic field is to provide protection against charged particles. These particles are trapped in a barrier called Van Allen belts, discovered by first American satellite Explorer 1 [3]. The inner belt is formed in altitude from 1000 km to 6000 km, the outer belt in altitude from 13 000 km to 60 000 km. The altitudes and intensities of the belts vary based on which position on Earth they are measured from. The belts are most intense over the equator and almost absent above the poles [4].

The particles are mostly electrons and protons. Due to the high density of these particles, satellites and other man-made objects need a greater protection against radiation. On the other side, objects are less influenced by radiation below the inner belt.

In inclination, lower than 28 degrees and altitude lower than 500km, space satellites suffer from radiation dose 100-1000 rad(Si)/year. For higher inclinations and altitudes, the radiation dose increases to 1000-10000 rad(Si)/year [5].

#### 1.9. Galactic Cosmic Rays

The galactic cosmic ray environment consists of protons and heavy nuclei with energies from 1 MeV/nucleon to 100 GeV/nucleon. Electrons are also in cosmic rays, but their amount is significantly smaller [1].

#### 1.10.Solar Proton Events

The solar proton event generates hydrogen and heavy nuclei within energy range from 0.1 to 100 MeV/nucleon. Their intensities are usually several orders of magnitude large than of the galactic cosmic rays at these low energies. The galactic cosmic rays dominate the spectrum at energies above 100 MeV/nucleon. Solar proton events are one of the major radiation concern to spacecraft designers [1].

#### 1.11.Meteoroids and space debris

Every spacecraft is exposed to the risk of collision with micrometeoroids and space debris. The damage depends on the size, impacted structure, and speed and direction of the impacting particle. An impact can cause serious damage and lead to malfunctions or destruction of the spacecraft. Impact velocities range from 11 to 70km/s [1].

In 2008 only 7% of objects in Earth's orbit were operational spacecraft, 41% were spent upper stages and mission-related objects. About 52% were parts from collisions and explosions. These objects can be divided into trackable and non-trackable particles. More than 500,000 particles are tracked. These particles are of the size of marble or bigger. The danger of hitting tracked particle can be minimized by choosing suitable orbit or small track adjustments [6]. The danger increases for CubeSat as they mostly do not have an engine which could be used to change its position.

The bigger danger is from non-trackable particles as they are nearly impossible to detect and there are many millions of them in orbit [7].

#### 1.12.Dust

Dust can behave as a collection of charged particles. Comet dust environment can affect operations during flybys and/or landings. Significant dust environments are presented at the Moon, Mars, and comets [1].

#### 1.13. Space Launchers - vibrations and acceleration

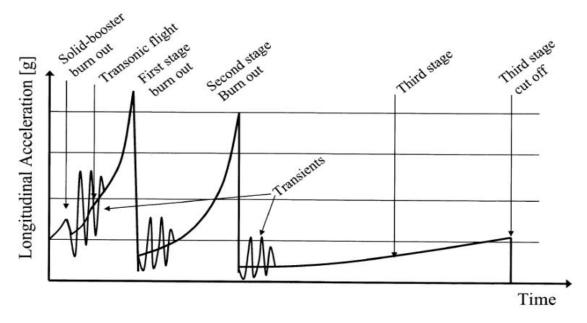

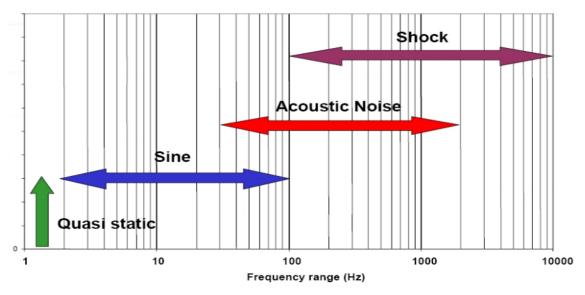

A satellite suffers from vibrations and acceleration from the lift-off of a rocket until cut off of the last engine (some satellites have their own engine to change their orbit), shown in Figure 2.

Figure 2: Steady-state and low-frequency accelerations during flight [8]

They are mostly caused by quasi-static loads, random vibrations, and shocks. They occur in different frequencies and amplitudes [8]. Figure 3 illustrates their distribution.

Figure 3: Typical frequencies of vibrations and shocks [8]

Quasi-static loads can be considered as static acceleration. They are a combination of acceleration of a rocket carrying the payload and low-frequency vibrations. They are mostly axial, with the highest value at stage burnout [9]. Random vibrations are mostly caused by engines of the rocket, structural responses to acoustic loads and aerodynamic

turbulences. The random means that all frequencies occur at the same time, but different amplitude. They are usually most stressing, as some frequencies can produce effective loads of tens g's [10]. Shocks are made by firing pyrotechnic mechanisms like stage separations, solar arrays deployment, and others.

#### **1.14.Orbits**

Spacecraft can orbit the Earth, Moon, and other objects (usually planets and moons). Most spacecraft have prograde orbits (they move from west to east), as it is the usual direction of rotation of objects [11].

#### **Low Earth Orbit**

Low Earth Orbit (LEO) is the lowest orbit which a spacecraft from Earth can reach. Most of spacecraft and satellites are deployed there as cost-to-orbit is the lowest. It lies in altitudes from 160 km to 2000 km [11]. Molecules in the atmosphere create a drag, which causes a decrease of spacecraft's orbit, therefore spacecraft need to periodically adjust their orbits. LEO is also the place where most of the space debris is located [12].

#### Geostationary and geosynchronous orbits

A geostationary or geosynchronous orbit is located at an altitude of 36,000 km. It takes the satellite 24 hours to orbit the Earth at this altitude, the satellite moves at the same speed as the Earth rotates. Geostationary satellites are orbiting above the equator in a circular orbit. Geosynchronous satellites are not positioned over the equator or have an elliptical orbit and so they appear to move across the sky. These types of satellites are typically communications or weather satellites [11].

#### Polar orbit

A polar orbit is any orbit in which the spacecraft passes over the rotation poles of the planet. In a polar orbit, the spacecraft can be made to follow any line of longitude. As the Earth rotates below the satellite, the satellite passes over a different region of the planet with each orbit. Polar orbits are used to map a planet or to observe specific effects relating to polar regions [11].

#### **Sun-synchronous orbit**

An orbit that passes over the same part of Earth at the same local time each day is called Sun-synchronous [11].

## 2. Radiation effects on electronics

The ionizing particles may generate failures in integrated circuits and semiconductor devices, as they can change a transistor state. These failures can be transient or permanent, depending on charge and location of the interaction.

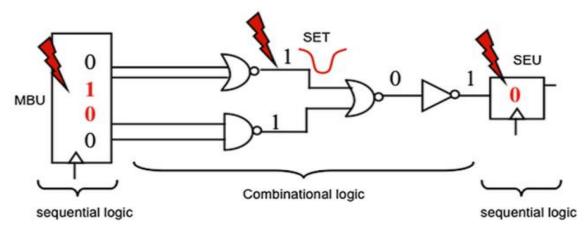

The most frequent are Single Event Effects (SEE). They are considered as Soft Errors, as their effect is only temporary. The SEE can be divided to Single Event Upset (SEU) and Single Event Transient (SET). The SEU causes a change of state of a memory cell. Information, saved in the memory, is corrupted but the logic cell works normally. When new information is written, the logic cell will contain the new information unless another SEU occurs. The SET happens when radiation causes a voltage spike on an output of a circuit. The effect is only temporary, but the output can be latched during the spike and lead to serious failures. The particle can also have enough energy to interact with multiple transistors, which can lead to Multiple Cell Upset (MCU). If the corrupted bits are in the same memory, the error is named as Multiple-Bit Upset (MBU) [13]. The SEE are shown in Figure 4.

Figure 4: SEU, MBU and SET in the sequential and combinational logic [13]

Faults can also be permanent. Single Event Latchup (SEL) is caused by the opening parasitic bipolar transistors. The SEL can produce a large current between  $V_{CC}$  and ground. The power dissipation significantly increases as well as the temperature of the chip. The current can also damage nets and/or semiconductors and other parts. That can lead to permanent destruction of the IC. After the SEL occurs, the damage of the IC can be prevented by turning off the power supply [14]. Parasitic bipolar transistors are illustrated in Figure 5.

Figure 5: Cross-section of PMOS and NMOS devices, showing parasitic transistors Q1 and Q2 [15]

Single Event Gate Rupture (SEGR) is an event when radiation damages gate oxide of MOSFET transistor. It can also create conducting path through the gate. The SEGR affects mostly power MOSFETs [16]. Power MOSFETs can also suffer from Single Event Burnout (SEB). Radiation can induce current flow which opens parasitic bipolar transistor below the source. The bipolar transistor conducts short-circuit current through the MOSFET which leads to its destruction.

The sum of particle interactions is called Total Ionizing Dose (TID). In the long term, it can change part's threshold voltages, current leakage, timing parameters and other characteristics [17]. For space applications, the TID is expressed in krad(Si).

As a charged particle interacts with a material (semiconductor), it passes its energy to the material. This energy is expressed as Linear Energy Transfer (LET). The LET is described as the amount of energy the particle passes per one unit of distance and density (mostly MeV-cm2/mg). For example, the [14] shows the number of SEU events based on the amount of LET.

Electronics can be divided, based on the radiation hardness, into three groups: Commercial, Rad Tolerant, and Rad Hard. Their comparison is shown in Table 1. The commercial electronics is mostly made without any protection against radiation. The design of Rad Tolerant electronics is made in a way to provide protection against radiation, but only up to few tens of krads(Si). Rad Hard electronics is designed and manufactured for particular hardness level. The radiation protection often affects the design of the chip and also the design of its package. The electronics is tested in the radiation chamber.

Table 1: Categories of components and their characteristics [18]

| Commercial                                         | Rad Tolerant                                            | Rad Hard                                                   |

|----------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------|

| Process and Design limit the radiation hardness    | Design assures rad<br>hardness up to a certain<br>level | Designed and processed<br>for particular hardness<br>level |

| No lot radiation controls                          | No lot radiation controls                               | Wafer lot radiation tested                                 |

| Hardness levels:                                   | Hardness levels:                                        | Hardness levels:                                           |

| Total Dose:                                        | Total Dose:                                             | Total Dose:                                                |

| 2 to 10 krad (typical)                             | 20 to 50 krad (typical)                                 | > 200 krad to >1 Mrad                                      |

| SEU Threshold LET:                                 | SEU Threshold LET:                                      | SEU Threshold LET:                                         |

| 5 Mev/mg/cm2                                       | 20 MeV/mg/cm2                                           | 80-150 MeV/mg/cm2                                          |

| SEU Error Rate:                                    | SEU Error Rate:                                         | SEU Error Rate:                                            |

| 10 <sup>-5</sup> errors/bit-day (typical)          | 10 <sup>-7</sup> - 10 <sup>-8</sup> errors/bit-day      | 10 <sup>-10</sup> to 10 <sup>-12</sup> errors/bit-day      |

| Customer performs rad testing and assumes all risk | Usually tested for functional fail only, risky          |                                                            |

| Customer evaluation and risk                       | Customer evaluation and risk                            |                                                            |

The radiation hardness also depends on the technology of the chip. Bipolar devices have significantly better hardness than unipolar (shown in Table 2). The hardness also differs for digital and analog circuits. Radiation degrades bipolar transistor's beta, which affects collector current and the operation of a circuit. It also affects transistor's input impedance, offset and gain [18].

Table 2: Radiation Hardness Comparison [18]

| Technology |             | Total Dose Hardness<br>[rad] |

|------------|-------------|------------------------------|

|            | TTL/STTL    | 1 · 10 <sup>6</sup>          |

| D' l       | ECL         | $1\cdot 10^7$                |

| Bipolar    | IIL         | $1\cdot 10^6$                |

|            | LINEAR      | 1 · 10 <sup>4</sup>          |

| MOS        | NMOS        | $7\cdot 10^2$                |

|            | CMOS (BULK) | $3\cdot 10^3$                |

|            | CMOS/RH     | $1\cdot 10^7$                |

|            | CMOS-SOS    | $1\cdot 10^6$                |

## 3. CubeSat

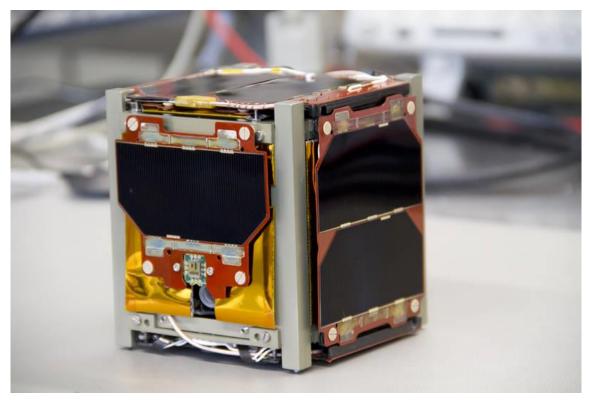

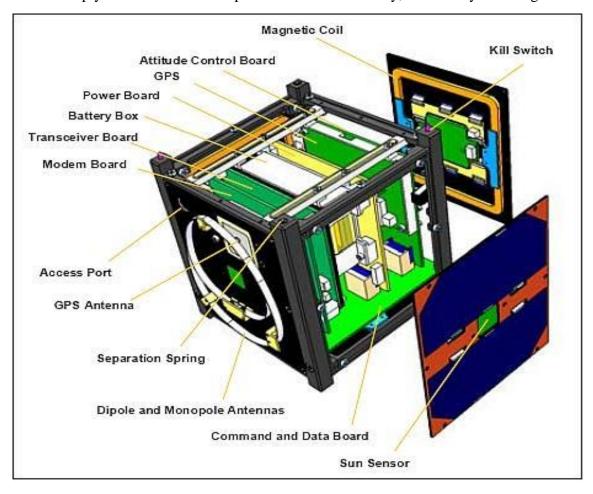

CubeSat are defined as U-class spacecraft with dimensions of 10x10x10 cm and weight up to 1.33 kg per unit. That is considered as one unit (U). Final CubeSat can consist of several units, mostly 1U, 3U, and 6U. An example of 1U CubeSat is shown in Figure 6. They are mostly composed of several boards; CubeSat COMPAS-1 is shown in Figure 7 as an example. Once in orbit, they are deployed from Poly-Picosatellite Orbital Deployer (PPOD) [19].

Figure 6: The First-MOVE CubeSat [20]

To reduce overall cost, CubeSat are mostly made by commercial parts. Also, they are often used to test new technologies before they are used in bigger satellites. As a disadvantage, they are usually not tested for radiation, and they are not suitable for space application outside of the Low Earth Orbit. To be suitable, every part has to go through series of tests, and their design has to be prepared for the space environment [21]. Most of CubeSat can survive only protected by Van Allen belts and even then, their lifetime is in order of moths.

CubeSat mostly use solar cells as a power source. As the surface area is small and limited, the power consumption has to be as low as possible. Some designs use bigger solar arrays which are deployed by spring or similar mechanism [22]. Solar cells are used to power electronics and often charge batteries. CubeSat use rechargeable Li-ion batteries to provide necessary power during the eclipse as well as during peak load times. Heaters are sometimes used to protect batteries against low temperatures [23].

For data handling and computing, CubeSat mostly use microcontrollers [22]. They provide sufficient computing power with low power requirements. On the other hand, they are not able to perform several tasks at the same time (sequential processing) therefore multiple of them have to be used. They also can react only to signals slower than few milliseconds [24]. As they are commercial parts, they are vulnerable to space radiation. Therefore they have to be protected by error detection and correction technique or/and redundancy.

To control an orientation of a CubeSat, different kinds of systems can be used. It can include reaction wheels, thrusters, Sun sensors, GPS receivers and others. They can be used to turn a CubeSat to face the Sun as much as possible, which increases the power generated by solar cells. Some CubeSat use a propulsion to change their position. That also helps to avoid collision with space debris. Tanks with cold gas are mostly used, but some experiments with electric propulsion and solar sails also have been made [23].

CubeSat use radio-communication systems in VHF, UHF, L-, S-, C- and X-band. Due to limited power supply, their power is usually limited up to 2W [25]. Every design has to comply radio standards and parameters of the country, where they are designed in.

Figure 7: Configuration of the COMPASS-1 CubeSat [26]

#### 3.1. Requirements

The CubeSat power system must be turned off while placed in PPOD. The power system consists of all batteries and solar cells. That prevents unwanted activation of any system. To achieve reliable off state, a mechanical deployment switch must be used. The switch is turned when the CubeSat is released from PPOD. If the switch is turned on and back, all circuits and timers must be reset.

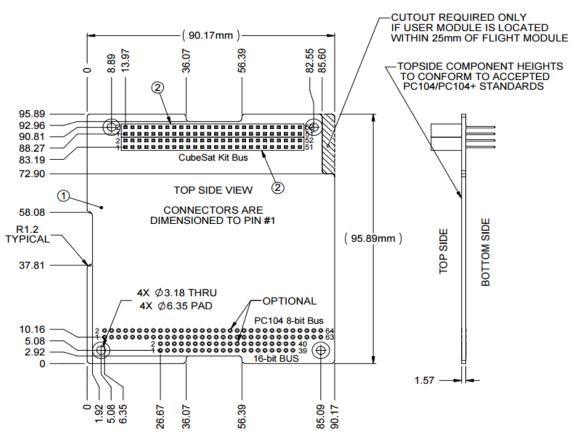

As the final board for this thesis is designed to fit into one unit, it must fulfill dimensional requirements, shown in Figure 8.

| ITEM | QTY | PART NUMBER    | DESCRIPTION        | MANUFACTURER |

|------|-----|----------------|--------------------|--------------|

| 1    | 1   | PC104 Spec PCB | User               | User         |

| 2    | 2   | ESQ-126-39-G-D | 2x26 Stack-Through | Samtec.com   |

Figure 8: Required board dimensions [27]

Every board must be equipped with Samtec 2x26 Stack-Through connector to connect to other boards.

## 4. Design of the control unit

#### 4.1. Design options and requirements

There are several ways to decrease the influence of the space environment. Examples range from shielding and blankets to careful component selection [1].

#### 4.1.1. Expected environmental conditions

For each mission, expected environmental conditions must be evaluated, and the design has to fulfill all requirements. As the final application is not known, the most common is used for the design. CubeSat are usually deployed in the Low Earth Orbit, often from the International Space Station (ISS). The orbit parameters of the ISS can be used to specify the environment. The ESA provides simulation tools which can simulate all characteristics [28], discussed in the first chapter.

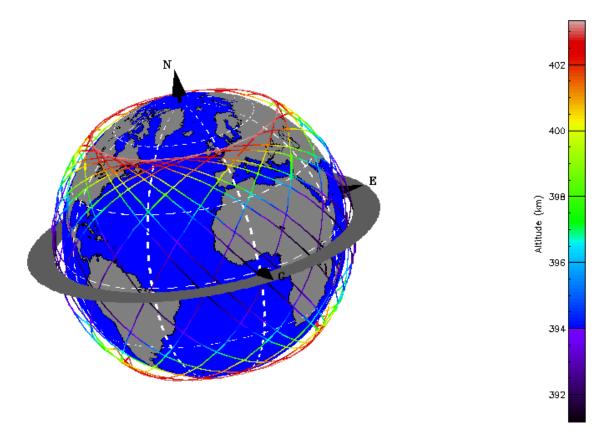

The CubeSat's orbit has Apogee 410 km, Perigee 402 km, orbit time 93 minutes and Inclination 52°. The simulation is shown in Figure 9. The mission duration is set to one year. The atmospheric drag slowly decreases the altitude.

Figure 9: Simulated orbit [28]

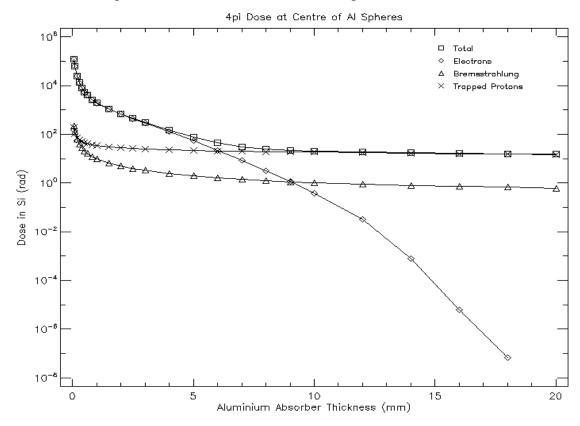

After the orbit is set, it is possible to simulate long-term radiation dose. Figure 10 shows simulated dose based on shielding thickness. For example, measurement for XC6SLX150 (Spartan 6) shows that an SEU error is produced for dose ~13 Rad [29].

Figure 10: Expected dose rate as a function of shielding thickness [28]

Table 3 shows expected number of SEU, experienced by MOS transistor 2164, for the whole mission duration. Even thin shielding can significantly decrease the number of SEUs. Also, the device is protected by radiation belts. In geostationary orbit, the total number of bits for whole mission is about 10<sup>6</sup> times higher [28].

Table 3: Simulated SEU rate [28]

| Table 3: Simulated SEO rate [28] |                            |                            |                     |                            |                            |                     |

|----------------------------------|----------------------------|----------------------------|---------------------|----------------------------|----------------------------|---------------------|

| Tipee 4                          | Shielding thickness 0.0 mm |                            |                     | Shielding thickness 0.5 mm |                            |                     |

| Effect                           | Bit                        | Bit/s                      | Bit/Day             | Bit                        | Bit/s                      | Bit/Day             |

| Direct ionization                | $4.8\cdot 10^{1}$          | $1.5 \cdot 10^{-6}$        | $1.3 \cdot 10^{-1}$ | $1.4 \cdot 10^{-3}$        | 4.4<br>· 10 <sup>-11</sup> | $3.8 \cdot 10^{-6}$ |

| Proton induced ionization        | $1.5 \cdot 10^{-3}$        | 4.8<br>· 10 <sup>-11</sup> | $4.1 \cdot 10^{-6}$ | $1.4 \cdot 10^{-3}$        | 4.3<br>· 10 <sup>-11</sup> | $3.7 \cdot 10^{-6}$ |

| Total                            | $4.8\cdot 10^1$            | $1.5 \cdot 10^{-6}$        | $1.3 \cdot 10^{-1}$ | $2.8 \cdot 10^{-3}$        | 8.7<br>· 10 <sup>-11</sup> | $7.5 \cdot 10^{-6}$ |

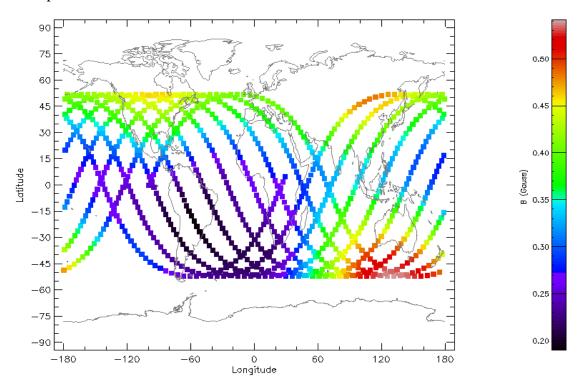

Figure 11 shows simulated magnetic field. The CubeSat can experience magnetic field up to  $0.6\ \mathrm{Gauss}$ .

Figure 11: Simulated magnetic field [28]

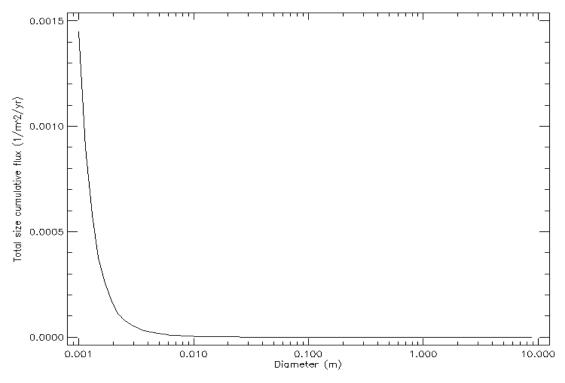

Figure 12 shows a number of particles going through one square meter per year. As the number is lower than  $2 \cdot 10^{-3} \ 1/m^2/year$ , the probability hitting the CubeSat is low and therefore an engine and/or special shielding should not be needed.

Figure 12: Simulated debris and meteoroid flux [28]

#### 4.1.2. Shielding

One of the best methods for environmental mitigation, especially for radiation<sup>1</sup> and hypervelocity impacts. The first step is usually to account for the intrinsic spacecraft body shielding. If necessary, radiation-sensitive parts can be protected by bulk shielding, for example placing them into a box of high-Z materials. A spot-shield can be used when mass is a concern. Also, shielding plates can be placed between assemblies. In the case of EMC and EMI, an electrically conductive Faraday cage can be used [1].

#### 4.1.3. Positioning and trajectory

Environmental effects are influenced by trajectory. It changes the amount of radiation, charging exposure and others. The placement or orientation of components or surfaces can minimize the effects of the environment. For example, the orientation of a surface to the velocity vector to minimize meteoroid fluence. Positioning can bring a reduction in specific fields yet has usually no impact on a system design [1].

#### 4.1.4. Materials

Proper material selection can significantly improve the lifetime and reliability. There can be complex trade-offs between conductivity, thermal paints, and radiation sensitivity. Steps for selecting proper material are listed in [1].

#### **4.1.5.** Electronic parts selection

Electronic parts selection is a critical part of a spacecraft design. An engineer must trade cost and availability versus the class of part (commercial, military, space) and its survivability [1]. The process is discussed in chapters 2, 4.2, 4.3 and 4.4.

#### 4.1.6. Circuit design

Circuit designs can limit radiation and thermal effects. It includes error detection and correction software, redundancy, proper layout and others. All spacecraft circuits should be tested for EMI and EMC [1].

#### 4.1.7. PCB layout

Space environment creates surface charging potentials, as discussed in chapter 1. These effects can be mitigated by the proper layout and especially grounding [30].

<sup>&</sup>lt;sup>1</sup> Figure 15 shows how the shielding affects the amount of radiation dose

#### 4.2. Control unit selection

CubeSat mostly use microcontrollers, as well as boards only with microcontrollers are available on the market [22]. They have their advantages, but they can be unsuitable for some applications, where parallel computing or/and faster response is necessary. FPGAs can accomplish these requirements. Some aspects are shown in Table 4.

Table 4: Properties of CPUs and FPGAs [24]

|                      | CPU                                                                               | FPGA                                                                                                       |

|----------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Computation          | Fixed arithmetic engines                                                          | User-configurable logic, DSP blocks, and data flow                                                         |

| Appropriate tasks    | Decision making Complex analysis Lower data rate computation Block-oriented tasks | Compute-intensive algorithms  Massively parallel operations  Higher data rate computation  Streaming tasks |

| I/O                  | Fixed, dedicated I/O ports                                                        | User-configurable I/O ports                                                                                |

| Programmability      | Program execution                                                                 | Registers determine modes<br>and define operating<br>parameters                                            |

| Ease of programming  | C programming simplifies development tasks                                        | HDL programming mandates hardware awareness                                                                |

| Maintenance/Upgrades | Less difficult                                                                    | More difficult                                                                                             |

FPGAs can react to signals in the order of nanoseconds, and they can do multiple operations at the same time. Also, their design can be uniquely made for every application. Their disadvantages are high power consumption (tens of milliamps in standby), higher price and bigger area on the board. One of the main cons is a need for separate memory for bitstream, which increases overall price and area.

Several manufacturers offer FPGAs suitable for space applications (Microsemi, Xilinx, Atmel). They are Rad-Hard, able to survive radiation up to 300 kRad(Si) without errors. On the other hand, their price can be higher than the price of the whole CubeSat, and as space grade devices, it is problematic to buy them due to ITAR regulations. Therefore, the different type has to be chosen. Commercial type offers the lowest price, but the smallest temperature range (usually 0°C to 85°C). The military type has a better temperature range (usually -55°C to 125°C) and its design is made to be as reliable as possible (sometimes as Rad-Tolerant). Its price is higher than commercial and automotive, but lower than space grade. ITAR regulation also applies.

Automotive type can be the best option. It has the same temperature range as military (-40°C to 125°C) and its design is focused on reliability. The price is only slightly higher than commercial. All parts in this design were chosen to be automotive or better.

To choose an FPGA, it is necessary to decide between antifuse and SRAM-based FPGAs. Antifuses are used to create a conductive path between logic cells and other parts. Before programming, the paths have a high resistance. After a voltage is applied, antifuses create a permanent conductive path and the FPGA is then non-volatile. On the other hand, as the programming is permanent, they cannot be reprogrammed. That brings an issue if a new design must be uploaded. Antifuse FPGAs are often used for space application, as radiation cannot change the digital circuit inside. Radiation-tolerant antifuse FPGAs are immune to SEUs and TID does not change their characteristics over time [31].

SRAM FPGAs are volatile; therefore, they have to be reprogrammed every time after its power is turned on. It brings a benefit of possibility to reconfigure them at any time. The FPGA can also be reprogrammed in orbit, therefore its bitstream can be updated or completely changed to perform different tasks. For this reason, SRAM-based FPGA is used for the board design.

SRAM FPGAs are vulnerable to radiation as it can change the FPGA's bitstream. Then the FPGA's function can change and it can lead to catastrophic failure. To prevent any faults, bitstream must be periodically checked for errors. SRAM FPGAs are also more vulnerable to SEUs than Antifuse FPGAs [31]. Table 5 shows the detailed comparison.

Table 5: Susceptibility to radiation of SRAM and antifuse PLD [32]

| Susceptibility to particle radiation effects |                                |           |  |

|----------------------------------------------|--------------------------------|-----------|--|

| Resource Antifuse/flash SRAM                 |                                |           |  |

| I/O                                          | None                           | Low       |  |

| Register                                     | Moderate                       | Low       |  |

| Block RAM                                    | Very high (Very low with EDAC) | Very high |  |

| Logic cells                                  | None                           | High      |  |

| Routing matrix                               | None                           | High      |  |

Additional memory has to be placed with the FPGA to store the bitstream. After the FPGA is powered on, it copies the bitstream from memory and programs itself. The memory increases required area and overall price. Protection against radiation is necessary to prevent undesirable code change.

Atmel offers Rad-Hard and industrial FPGAs. Industrial FPGAs have insufficient temperature range (-40°C to 85°C) and a smaller number of logic cells (2304 cells for the biggest FPGA-AT40K40AL) [33]. As industrial, their design can be less reliable than automotive. The advantage is the use of 3V or 5V power supply, which eliminates the need for DC/DC converter.

Atmel's Rad-Hard FPGAs have a larger number of logic cells (14400 cells for ATF280F), desired temperature range (-55°C to 125°C), and they are protected against radiation. On the other hand, they need separate voltage for its core (1.8 V), use low-speed clock (50 MHz) and as previously said, their price is high.

Microsemi offers product lines for commercial, automotive, military and space applications. Its FPGAs are designed to be used in different types of applications. Some FPGAs are made for high computing power (IGLOO2, RTG4), for low power (IGLOO), with ARM cores (ProASIC3) and for mixed signal applications (Fusion). Microsemi is also the biggest manufacturer of antifuse FPGAs (RTAX, RTSX-SU, and others).

Xilinx offers product lines for commercial, automotive, military and space applications. Its main products are Spartan 6, Virtex, Kintex and Artix product lines. Its FPGAs have high computing power (thousands of configurable logic blocks), block RAM blocks, memory controllers and others features. Its FPGAs mostly have larger current consumption than Microsemi's FPGAs.

It was decided to use Xilinx's FPGA for this design. The program for digital design (ISE) is considered as more reliable and debugged. Another benefit is that its FPGAs have bigger user group than Microsemi, with more examples, sources, and advice for designs.

#### 4.3. Xilinx FPGA selection

Xilinx offers Spartan 6 line (made in 45 nm), Artix (made in 28 nm), Virtex and Kintex (made in 28 nm, 20 nm, and 16 nm). Technologies with smaller size can suffer more from SEU but they are more resistant to radiation [34]. Main aspects of the decision were power consumption and bitstream size.

#### 4.3.1. Power consumption

Products with a similar number of slices and logic cells from all product lines were chosen to compare power consumption; they are shown in Table 6. The main parameter was supply current for the FPGA's core (I<sub>CCINTQ</sub>) as it is the biggest of all quiescent currents. As a CubeSat's power is limited, an FPGA's power consumption has to be as small as possible.

Table 6: Comparison of Xilinx's FPGAs [35]

|           | Two or comparison of finance of the feet |        |             |  |

|-----------|------------------------------------------|--------|-------------|--|

|           | Part number                              | Slices | Logic cells |  |

| Spartan 6 | XC6SLX150                                | 23 038 | 147 443     |  |

| Virtex    | XC7VX330T                                | 51 000 | 326 400     |  |

| Kintex    | XC7K160T                                 | 25 350 | 162 240     |  |

| Artix     | XC7A100T                                 | 15 850 | 101 440     |  |

The XC7VX330T from Virtex line has more than twice larger number of slices and cells, but a smaller one is not available.

Table 7 shows the current consumption for selected FPGAs. Values are specified for nominal voltage and temperature of 25°C. The Spartan 6 has the lowest consumption even for the part with the largest number of logic. Parts with less logic have smaller power consumption.

Table 7: Comparison of Xilinx's FPGAs based on power consumption [35]

|           | Part number | ICCINTQ |

|-----------|-------------|---------|

| Spartan 6 | XC6SLX150   | 51 mA   |

| Virtex    | XC7VX330T   | 1012 mA |

| Kintex    | XC7K160T    | 474 mA  |

| Artix     | XC7A100T    | 155 mA  |

As the power is one of the most important issues in the CubeSat design, the Spartan 6 product line was selected for the final design.

#### **4.3.2.** Memory

One of the biggest challenges in the design is to safely store the bitstream for the FPGA. Memory must have sufficient capacity and temperature range, but the most important is the ability to preserve data without an unwanted change. Therefore, the memory must be immune to radiation and interference. For bigger satellites and vehicles (where the price is not important), Rad-Hard memories are used. They are tolerant to radiation (up to hundreds of kRad(Si)), thoroughly tested and they have been successfully used on tens of space missions. Like Rad-Hard FPGAs, their price is too high to be used in CubeSat. The main manufacturer is 3D Plus.

Another option is One-Time Programmable (OTP) memory. The OPT memory can be programmed only once as it changes the internal circuit. Then the data are permanently saved and cannot be changed. Therefore, radiation or any interference does not have an effect on the data. Their advantage also makes an issue. As the data are permanent, the memory cannot be reprogrammed. It eliminates the possibility of uploading new bitstream. For this reason, OPT memory is not used for the design of the final board.

The best option is Magnetoresistive random-access memory (MRAM). Unlike other types of memories, MRAM uses magnetic fields to store data. It is a high-speed non-volatile memory, with low power consumption [36]. The main advantage of the design is that radiation does not affect the magnetic field. Therefore it does not change the data inside the memory. MRAM can also survive harsh environments and temperatures [37].

Table 8: Comparison of various types of memories [38]

|                       | MRAM     | SRAM     | DRAM     | FLAH    | FERAM   |

|-----------------------|----------|----------|----------|---------|---------|

| Read Speed            | Fast     | Fastest  | Medium   | Fast    | Fast    |

| Write Speed           | Fast     | Fastest  | Medium   | Low     | Medium  |

| Array<br>Efficiency   | Med/High | High     | High     | Med/Low | Medium  |

| Future<br>Scalability | Good     | Good     | Limited  | Limited | Limited |

| <b>Cell Density</b>   | Med/High | Low      | High     | Medium  | Medium  |

| Non-Volatility        | Yes      | No       | No       | Yes     | Yes     |

| Endurance             | Infinite | Infinite | Infinite | Limited | Limited |

| Cell Leakage          | Low      | Low/High | High     | Low     | Low     |

| Low Voltage           | Yes      | Yes      | Limited  | Limited | Limited |

| Complexity            | Medium   | Low      | Medium   | Medium  | Medium  |

The highest density MRAMs are made by Everspin Technologies. They offer MRAMs with a capacity of 128 kb, 256 kb, 1 Mb, 4 Mb and 16 Mb. 64 Mb memory is in development. Memories are available in Commercial, Industrial and Automotive grade.

Other types of memories are vulnerable to radiation and therefore cannot be used for storing the bitstream. Table 8 shows that MRAM also excels in other parameters. They are useful when large capacity is needed and some data loss can be tolerated. MRAM memory was found as the best option and is used to store the bitstream for the FPGA. Flash memory is used to store data from sensors as it has a larger capacity and is also non-volatile.

#### 4.3.3. FPGA selection

As the final board can have various types of application, it is desired to have as many sources available as possible. It means to choose an FPGA with the largest number of logic cells. The XC6SLX150 would be a suitable choice, but the device's bitstream is too large to be stored in the MRAM (33.8 Mb). As the largest available MRAM is 16 Mb, then the XC6SLX45 with bitstream size of 11.9 Mb is the best choice. The XA6SLX45 (an automotive version of XC6SLX45) has 43,661 logic cells and 6,822 slices. The device is made only in BGA package. BGA packages are not recommended for space applications, as there is a high risk of badly soldered pins, shortcuts between pads and other issues [39]. To minimize the risk of failure, it is recommended to choose a package with the biggest pads and pitch. The FGG484 package with size 23x23 mm and 1.0 mm pitch was selected for the board. This package provides 316 user I/Os.

#### 4.4. Enhanced products

For other electronic parts, another option is available. Texas Instruments offer Enhanced Products (EP) line. Products in this line are suitable for use in military, medical and space applications. Unlike commercial parts, they are designed for long lifetime applications (15+ years), they use a rugged lead frame, improved die attach and Au bond wires. Copper bond wires can break during high stress and they are not tested for harsh environments. Au wires have proven long term success without a failure in harsh environments.

EP are also built in one FAB, tested on the same site and have one material set for product build. It reduces the difference between parts. They also must comply more tests, which are also more challenging. For example, commercial parts are tested by Highly Accelerated Stress Test (HAST) for 96 hours while EP are tested for 250 hours [40].

EP provides lots of benefits while the price is only a few percent higher than commercial parts, but it has smaller product range. It can make a design more challenging as some required parts may not be available.

#### 4.5. Circuit design

One of the main tasks of the board is to provide reliable FPGA reset if an error is found. An error detection has to be implemented by software. The software should decide if the FPGA can be reset, as an error in unimportant function should not reset the FPGA while critical tasks have to be done. Spartan 6 also checks the configuration memory. If the CRC is wrong, the FPGA must be reset.

The design uses two MRAM memories for storing the bitstream. The first memory is used to store proven, tested and errorless golden bitstream. The memory has a Write enable pin. The voltage on the pin can be set to zero (active mode) only by plugging a jumper in.

The bitstream is uploaded to "golden" memory before launch. Then the jumper is unplugged and as the Write enable pin is permanently connected to  $V_{CC}$ , the bitstream cannot be changed. This solution provides reliable bitstream storage.

The second MRAM can be used to store a new version of the bitstream. It can be deleted, changed or uploaded during flight. Storing a user data is also possible.

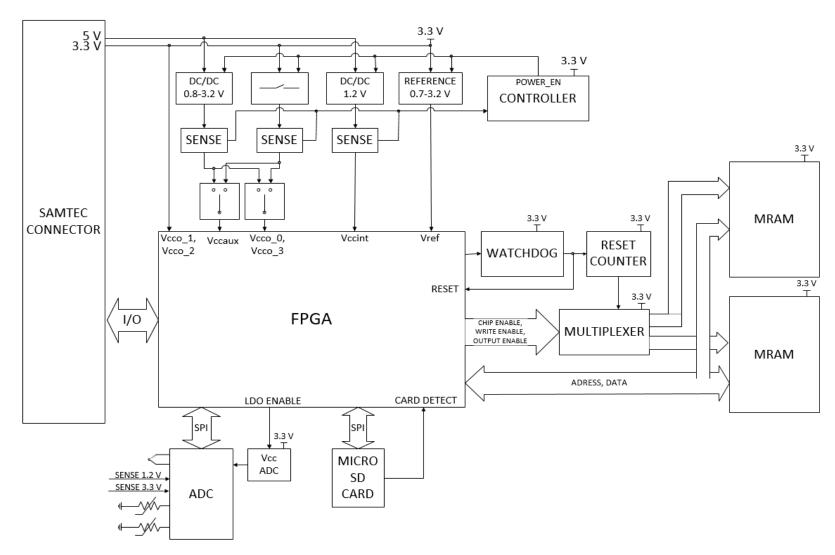

Block diagram of the final board is shown in Figure 13.

Figure 13: Block diagram of the control unit

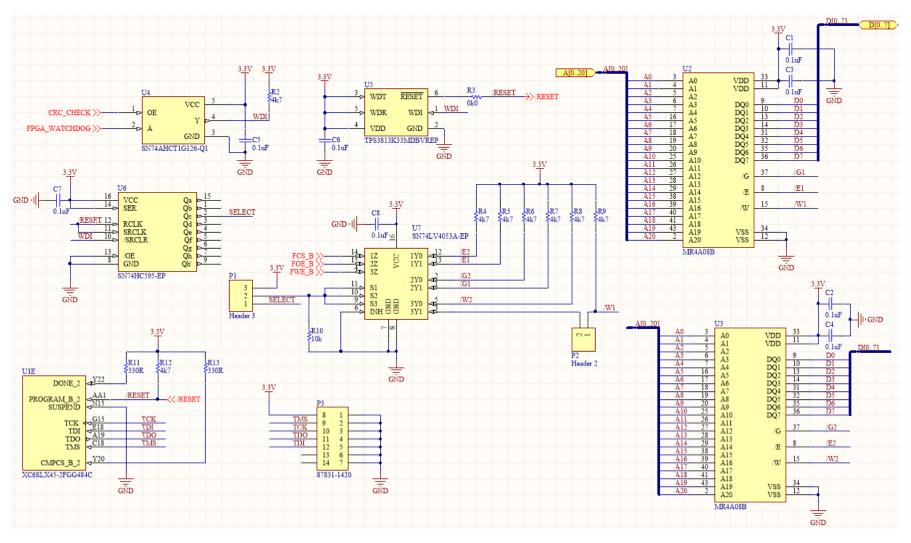

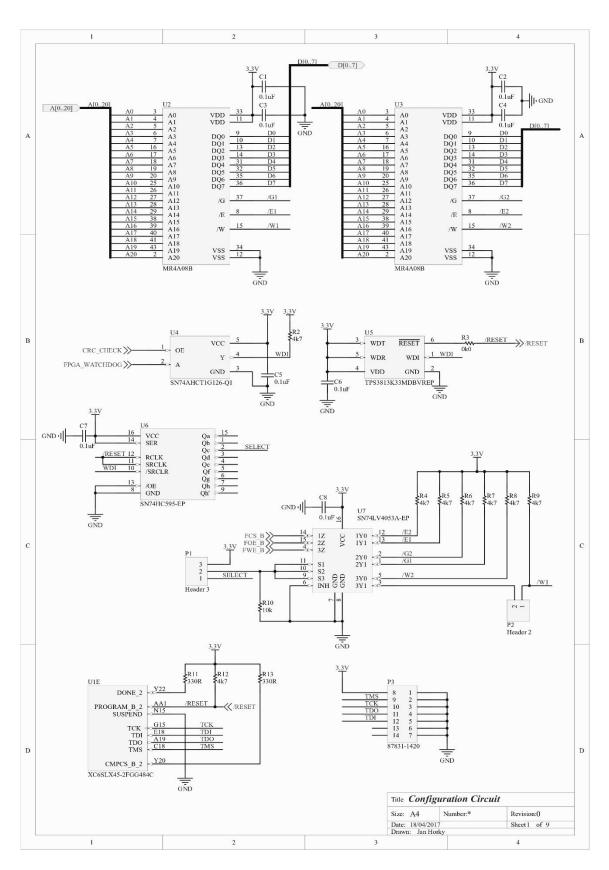

#### 4.5.1. FPGA configuration circuit

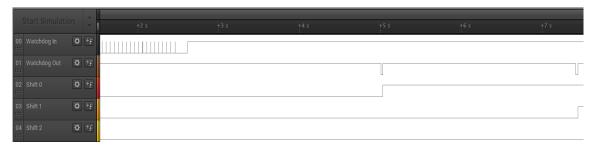

The FPGA must periodically produce a pulse on the WDI pin of the watchdog circuit (TPS3813K33MDBVREP). The pulse (longer than 3 us) must occur more often than 2 seconds but also less often than 25 ms. The signal goes through the buffer gate (SN74AHCT1G126). The buffer gate has Output Enable pin, which is controlled by INIT\_B from the FPGA. After the FPGA is programmed, CRC is periodically carried out. If an error is found, the INIT\_B is set to zero. That disables the buffer and the pulse cannot get to the watchdog.

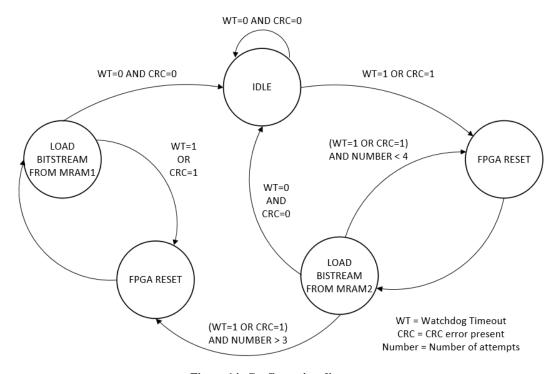

If the FPGA stops producing the pulse (by error or command) or the CRC sets INIT\_B to zero, then the watchdog timer resets the FPGA. Afterward, the FPGA is configured from the second MRAM. There can be an event when the configuration from the second MRAM fails. The reset can take place while uploading the bitstream, new code can incorporate an error and other faults. The FPGA can be stuck in reconfiguration loop and the whole CubeSat is unusable. To prevent this outcome, the board uses a shift register (SN74HC595) to count the number of configuration cycles. If the FPGA is reset three times in a row (the shift register needs two input pulses to shift the value), the shift register switches the multiplexer (SN74LV4053) to select the first MRAM with the golden bitstream. The whole process is illustrated in Figure 14. The multiplexer has a jumper on the Select input. Before the launch, when the golden bitstream has to be uploaded, the jumper ties the Select input to 3.3V. Only then the first MRAM can be accessed. Afterward, the jumper must be put into the other position to connect the Select input of the multiplexer to the output of the shift register.

Figure 14: Configuration diagram

All Data and Address signal are connected together; the multiplexer controls the MRAMs by signal Chip Enable, Output Enable, and Write Enable. A smaller multiplexer is needed than if all signals are switched. The MRAMs are switched in order of few hundreds of nanoseconds after the reset, while the FPGA needs at least 10us to start configuration [41]. The time window is sufficient to safely switch the signals. On the other hand, the default configuration clock is set to 2 MHz. Time needed for configuration is:

$$t_{CONFIG} = \frac{1}{clk_{CONFIG}} \cdot \frac{BITSTREAM}{8 \ bits} + t_{STARTUP}$$

$$t_{CONFIG} = \frac{1}{2 \cdot 10^6} \cdot \frac{11.9 \cdot 10^6}{8} + 10^{-3} \cong \underline{0.76 \ s}$$

$$(4.1)$$

where  $clk_{CONFIG}$  is configuration clock, BITSTREAM is the size of bitstream divided by 8 (MRAM has 8 data bits in parallel), and  $t_{STARTUP}$  is the time, until the FPGA starts configuration (defined primarily by ramp time of power sources).

As the watchdog timeout is 2 seconds, the configuration is fast enough to prevent the timeout. The frequency can be set up to 40 MHz if needed [41].

The pulse from the FPGA moreover resets the shift register. Such a solution increases the reliability of the circuit, as a chance of a change of the output by radiation is minimized.

When the board is powered for the first time, both memories are empty and the FPGA cannot load the bitstream. Therefore, programming the memories is not possible. Fortunately, the Spartan 6 provides the possibility to be programmed by JTAG. JTAG has to be used to program the FPGA and then the bitstream can be uploaded to the MRAMs. For this case, the watchdog must be disconnected by removing 0  $\Omega$  resistor on its output. Otherwise, the FPGA cannot be programmed as it is periodically reset before the bitstream's upload is finished. There is no need to use JTAG after the memories are programmed.

Proposed circuit is shown in Figure 15.

Figure 15: Schematic of the configuration circuit

#### 4.5.2. Power supply

The CubeSat specification requires that all boards must have standard interface connector. The connector's layout gives information that 5 V and 3.3 V are available as a power supply [42]. These voltages are active immediately after a CubeSat is switched on. A CubeSat should also provide additional 5V and 3.3V rails, which can be turned on by a command from the control unit. As only the FPGA can control them, they cannot be used for powering it.

The connector has a current rating of 3 Amps per pin. Each of main voltage rails uses two pins, but the design cannot ensure that the current does not go just through one pin. Therefore, the peak current value must be lower than 3 Amps.

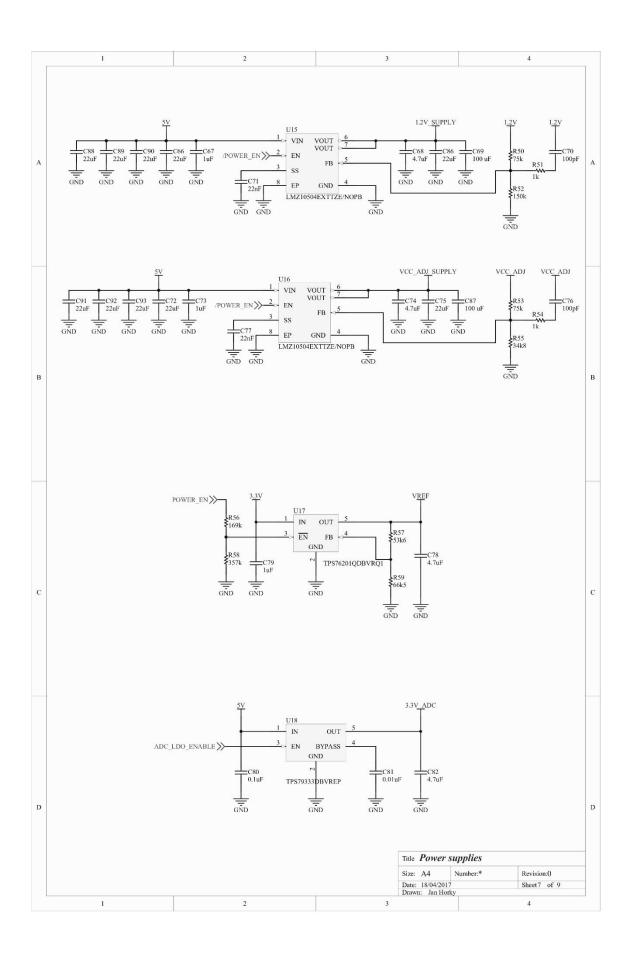

#### 4.5.2.1. Power for the FPGA's core

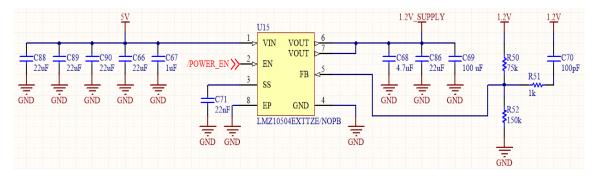

The Spartan 6 needs a different power supply for its core and I/O banks. The power consumption for its core depends mainly on logic usage. Xilinx offers a Power Estimator (XPE) which allows estimating all currents, temperature, and on-chip power. As the final application is not known, the XPE was used to assess the worst case. With the maximum logic used, 25,000 LUTs and 50,000 FFs with 50 MHz clock, the core needs a current of 2.4 Amps. Texas Instruments offers few EP DC/DC converters; however, their packages are too large to be used. Converter LMZ10504EXT was selected, as it passed EMI tests and military tests for vibration and drop. The converter has maximum output current 4 Amps, but can be changed to LMZ10505EXT with output current 5 Amps without any modifications.

To decrease the current through the connector, the converter uses 5 V as the input voltage. The converter has efficiency better than 80 %; input current can be calculated:

$$P_{OUT} = 0.8 \cdot P_{IN} \tag{4.2}$$

$$V_{OUT} \cdot I_{OUT} = 0.8 \cdot V_{IN} \cdot I_{IN}$$

$$1.2 \cdot 4 = 0.8 \cdot 5 \cdot x$$

$$x = 1.2 \text{ Amps}$$

$$(4.3)$$

where  $P_{OUT}$  is output power,  $P_{IN}$  is input power, 0.8 is the converter's efficiency,  $V_{OUT}$  is the output voltage,  $I_{OUT}$  is the output current,  $V_{IN}$  is the input voltage and  $I_{IN}$  is the input current.

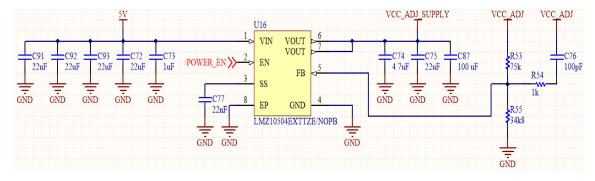

The input current is low enough not to damage the connector. The design was calculated using part's datasheet [43] for optimized ripple and transient response. The FPGA's core needs 1.2 V, the range of 1.14-1.26 V is allowed. Start-up time was set to 10 ms. The schematic of the converter is shown in Figure 16.

Figure 16: Schematic of the DC-DC converter

#### 4.5.2.2. Power supply for the FPGA's I/O banks

The Spartan 6 needs a separate power supply for I/O banks. The voltage depends on an I/O standard; the voltage can vary from 1.2 V to 3.3 V. Therefore, an adjustable voltage source is a must.

From the power estimation, the power consumption of I/O banks should not be higher than 3 Amps. Same DC/DC converter as for FPGA's core was selected to simplify the design. Output voltage can be changed in range 0.8 V to 3.3 V by changing resistor R55.

As other components on the board use 3.3V logic,  $V_{CCO\_1}$  and  $V_{CCO\_2}$  banks are permanently connected to 3.3V power rail and cannot be changed. It secures proper logic levels for communication with memories, ADC and other parts on the board.  $V_{CCO\_0}$  and  $V_{CCO\_3}$  banks have a jumper, which allows a user to select either 3.3V power rail or adjustable output from the converter. Selecting 3.3V power rail ensures same voltage potential for all banks, simplifies the design and space on the board (the converter can be removed) and decreases overall power dissipation, generated by the converter.

If different logic levels are not needed, all banks can be connected to the 3.3V power rail, the converter can be connected to  $V_{CCAUX}$  and set to 2.5 V. It decreases  $V_{CCAUX}$  current by 40 %. Otherwise, the  $V_{CCAUX}$  must be connected to 3.3V power rail as it can work only with 2.5 V and 3.3 V.

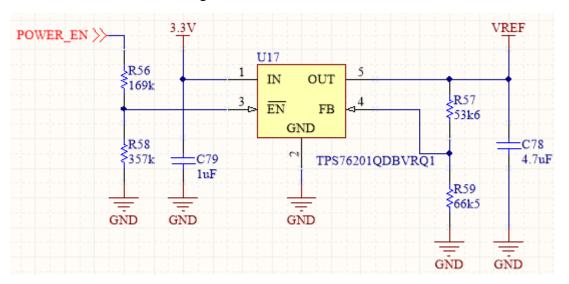

Final circuit is shown in Figure 17.

Figure 17: Schematic of the power supply for I/O banks

#### 4.5.2.3. Reference voltage

As some protocols also need a voltage reference for proper operation, an adjustable LDO is necessary. The need for current from the reference is negligible and therefore a small IC with low driving capability can be used. The board accommodates TPS76201, which is an Ultra-LDO with current capability up to 100 mA. Its output voltage can be set in a range from 0.7 V to 5.5 V with dropout voltage about 100 mV.

Final circuit is shown in Figure 18.

Figure 18: Reference voltage source

The power supplies are enabled by POWER\_EN signal. It uses 5V logic, but the TPS76201 can survive only voltages up to  $V_{\rm IN}$ . The input divider is used to decrease the Enable voltage.

The reference might be needed just on specific I/O banks; therefore, the voltage is connected through 0  $\Omega$  resistors. A user can disconnect the reference by removing these resistors.

#### 4.5.3. Latch-up protection

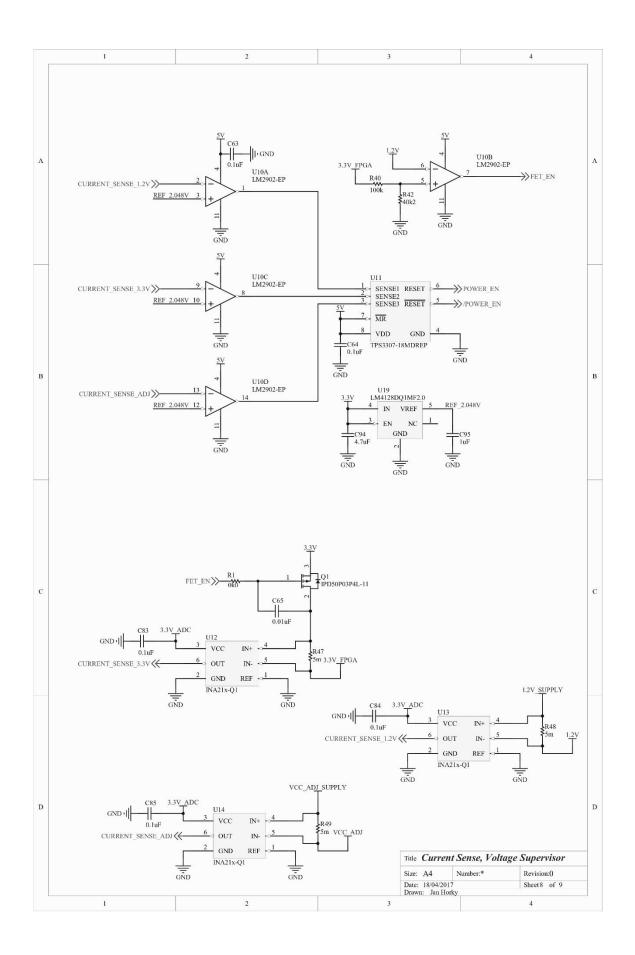

As previously discussed, SEL can permanently destroy an IC. Some sort of protection is a must.

The task of the protection circuit is to protect the FPGA. Protecting other devices would require large circuit and would significantly increase necessary space and overall cost. Also, if the FPGA and power supply are not harmed, the board can still work and do most of its tasks even when all other parts are destroyed.

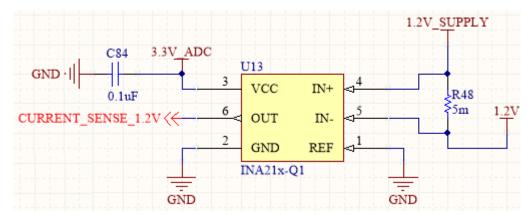

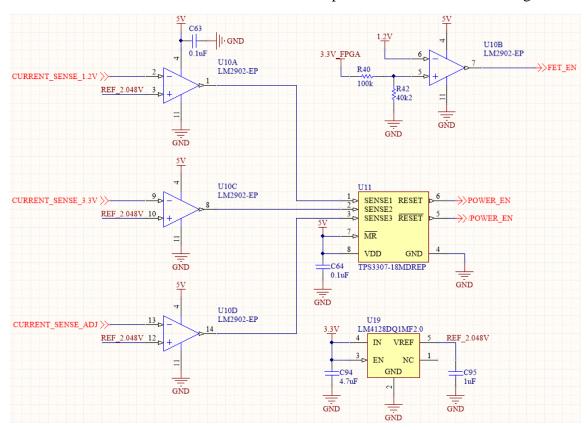

The circuit consists of sense resistors, amplifiers, comparators and supervisor circuit. The resistors are connected to 3.3V, 1.2V and ADJ supply rail for the FPGA. The resistors were selected to be 5 m $\Omega$ , as a bigger voltage dropout could cause malfunctions (supply voltage lower than needed). In 1.2V and ADJ supply rails, the resistors are placed before

voltage dividers to produce a stable output voltage, as the regulators compensate the voltage across the sense resistors.

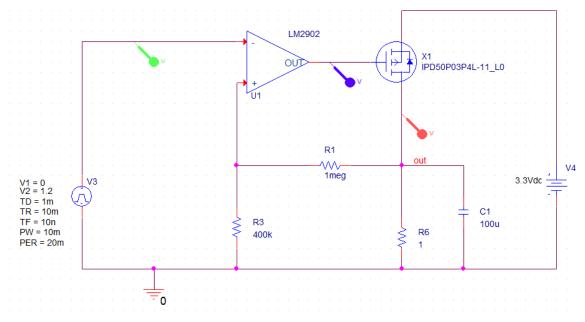

Figure 19: Sense circuit

The voltage across the sense resistors is amplified by op-amps INA214 (shown in Figure 19). Each op-amp has gain 100, and their output is connected to comparators LM2902-EP. If a comparator's input voltage is higher than the reference voltage, the comparator changes its output to log.0. If the voltage on any Sense input of the supervisor (TPS3307-18) is in log.0, the supervisor disables all power sources. Power sources are enabled when SEL is removed. The supervisor circuit is shown in Figure 20.

Figure 20: Schematic of the supervisor circuit

3.3V power rail is produced outside of the board, therefore a PMOS transistor is used to switch the rail on/off. The allowed voltage range is small, so power transistor with ultralow  $R_{DS}$  is a must. Also, the transistor must be fully opened at  $V_{GS}$  of 3.3~V.

The requirement for voltage ramp brings an issue with switching the PMOS. Providing a voltage with a ramp on the gate of the transistor is not a suitable option. The transistor would be closed until the voltage reaches threshold voltage of the transistor. Then the output voltage rises almost immediately to the supply rail. The ramp time of the voltage cannot be guaranteed. To provide desired ramp time, some feedback is necessary.

The opamp LM2902-EP uses 1.2V power rail as input. When power is enabled, the 1.2V rail rises with stable ramp time. The op-amp compares the power rail with the output of the PMOS and changes its output to achieve same value. Connected resistors divide the PMOS's output by 2.5. The reason is to have output voltage 3.3V when the input voltage is 1.0V. It decreases the ramp time, but the output is immune to any interference on the input. Figure 21 and 22 show improved circuit and its simulation.

Figure 21: Improved circuit

Figure 22: The input and output voltage

#### 4.5.4. Capacitors for supply rails

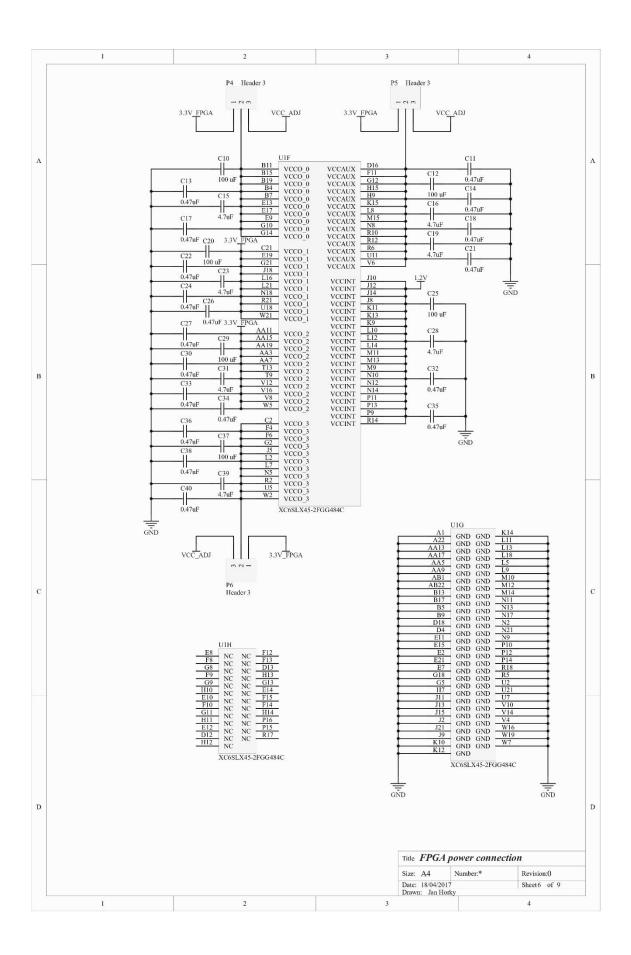

The FPGA needs specific capacitors for all supply rails and each bank. These capacitors and recommended layout are specified in the FPGA's datasheet.

#### 4.5.5. Clock generator

The FPGA needs an external clock for operation. A CMOS MEMS oscillator was selected, as this type is the only one with desired temperature range. Also, it usually has a smaller package.

The DSC1101 oscillator with 50MHz frequency was selected. It is qualified to MIL-STD-883, which means excellent shock and vibration immunity and reliability.

#### 4.5.6. Data storage

The board uses microSD card as main data storage. Using card brings benefits of bigger storage for data and simpler communication over SPI. That also means the significantly lower number of signal lines than for parallel communication.

MicroSD cards have great shock, vibration, humidity and magnetic immunity. The connector has a detect signal, which checks if the card is plugged in. The FPGA can check if the card is connected correctly before sending data.

The main problem is the temperature range. As MicroSD cards are capable surviving a temperature range from -25°C to 85°C [44], it decreases overall board usability. Other parts are selected to work in the range up to 125°C.

If the temperature is a concern and if there is no need for storing a large amount of data, one of the MRAM memories can be used as storage. A user can store data to MRAM without changing the circuit, the principle works the same way as storing new bitstream. The main disadvantage is that the board loses the ability to have two bitstreams. Also, the reconfiguration takes more time, as the circuit first tries to load bitstream from MRAM with user data. After it fails, it loads the golden bitstream.

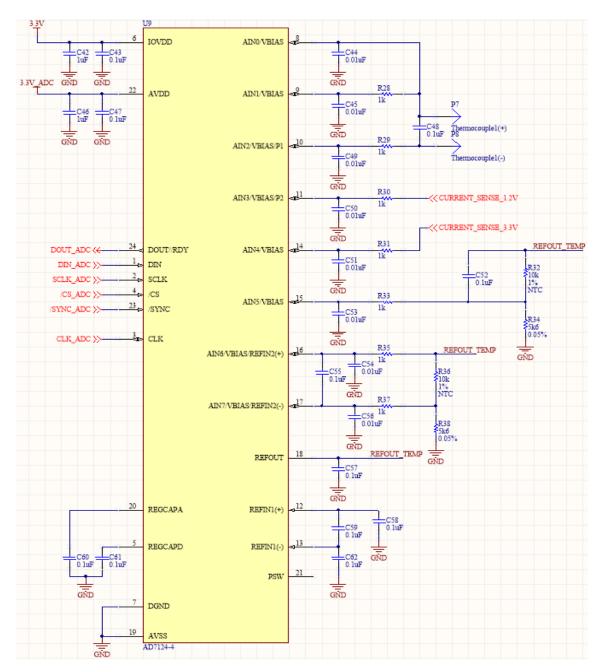

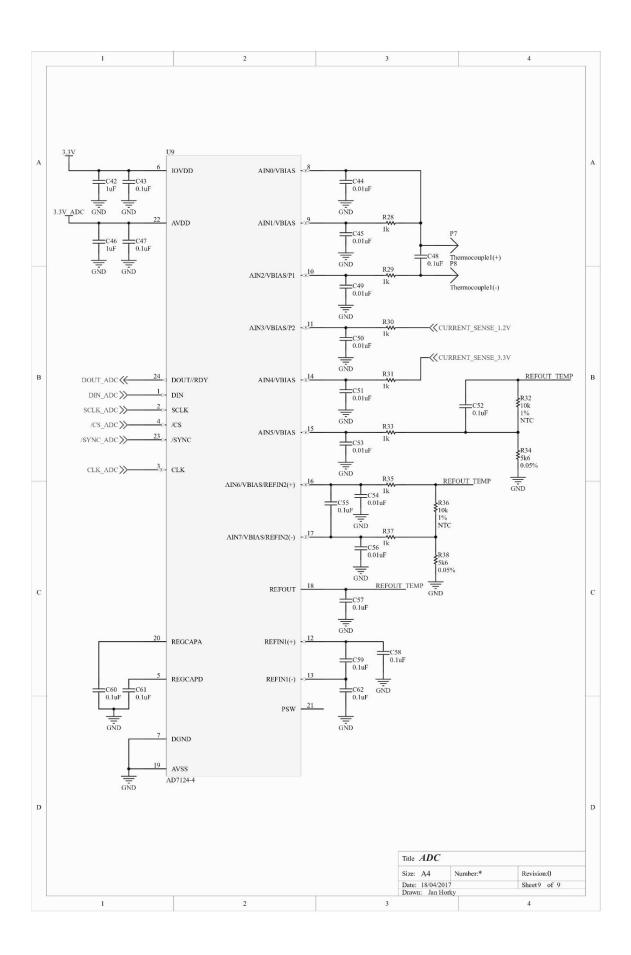

#### 4.5.7. AD converter

The main way how parts dissipate their heat is through heat convection with air. This way is not present in space vacuum; therefore the power dissipation is a big concern. The most important parts' temperature should be periodically checked and some measures must be done if temperature achieves threshold value.

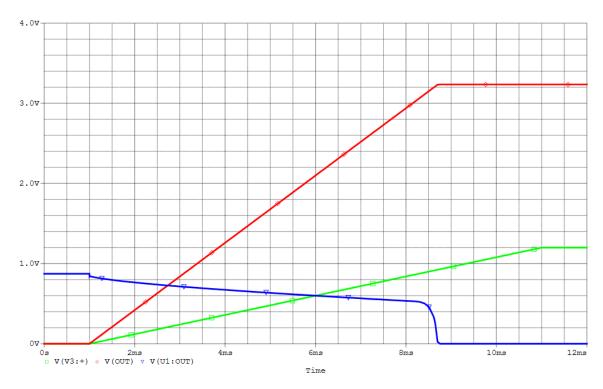

The parts with the highest dissipations on the board are the DC/DC converters and the FPGA. The converters have internal temperature sensors, which shut them down in a case of high temperature, yet another sensor can warn the FPGA early and some measures may be used. The ADC has two thermistors, which measure temperature on the board. As the main heat transfer in space is by conduction, a thermistor placed close to a part can sense the part's temperature. One of the thermistors should be placed near the FPGA as close as possible. The ADC also has a connection to thermocouples, which can be attached to any part on the board (or whole system). For example, it can be attached directly to the FPGA's package, measuring the temperature more accurately. A thermocouple measures only temperature difference, therefore one of the thermistors should be placed as close to thermocouple's terminals as possible to get the reference value. The circuit is shown in Figure 23.

The ADC also measures the voltage on the current sense circuits, so the current consumption on 1.2V and 3.3V power rails can be calculated:

$$V_{SENSE} = \frac{V_{CURRENT\_SENSE}}{GAIN_{INA214}} = \frac{V_{CURRENT\_SENSE}}{100}$$

(4.15)

$$I_{RAIL} = \frac{V_{SENSE}}{R_{SENSE}} = \frac{V_{SENSE}}{5 \cdot 10^{-3}}$$

(4.16)

where  $V_{SENSE}$  is the voltage on the sense resistor,  $V_{CURRENT\_SENSE}$  is the output voltage of the INA214 op-amp, GAIN<sub>INA214</sub> is the gain of the INA214 op-amp, I<sub>RAIL</sub> is the current through the sense resistor and R<sub>SENSE</sub> is the resistance of the sense resistor.

Figure 23: Schematics of the AD converter

## 5. PCB design

The PCB dimensions were designed according to CubeSat specification, described in chapter 3.1. The FPGA was placed as close to the I/O connector as possible to allow high-speed signals. The same reason was for placing oscillator and configuration circuit close to the FPGA.

Almost every part is placed on the top side of the board as it allows soldering by reflow. Only capacitors for the FPGA and the MRAMs are placed on the bottom side. It improves noise reduction and overall performance.

The PCB has copper pour in all layers, which improves shielding and heat conduction. The exception is the top layer under the FPGA. The copper plane can cause assembly issues, therefore is not used for this version. If the proper assembly can be ensured, the design can be easily changed. Top and bottom layer are connected to the GND and interconnected using via stitching. The board is shown in Figure 24.

Parts were assembled in vapor phase oven at Department of Microelectronics.

Figure 24: Final board

### 6. Price

The bill of materials is shown in Annex C. The overall price of the component is below 200 euro and price of the PCB is 67 euro [45]. Average control unit costs 4500 euro [22]. The unit proposed in this thesis brings significant cost reduction.

### 7. Digital design

As the aim of this thesis is hardware design, the main purpose of digital design is to demonstrate the unit's capabilities and test its functionality. Therefore, the Software-Implemented Error Recovery, Profile-Guided Code Transformation, and other techniques are not implemented. Using these techniques improves error mitigation and SEU protection [13].

The unit communicates with the user over UART, with one stop and start bit, no parity bit, and frequency 115200 bauds. The frequency can be easily changed in the code.

#### 7.1. TOP Module

The TOP module is mainly responsible for communication with the user and between other modules. It accepts requests from UART and sends responses. It also checks correct temperatures and voltages and resets the FPGA in the case of limit values.

#### 7.2. MRAM Controller

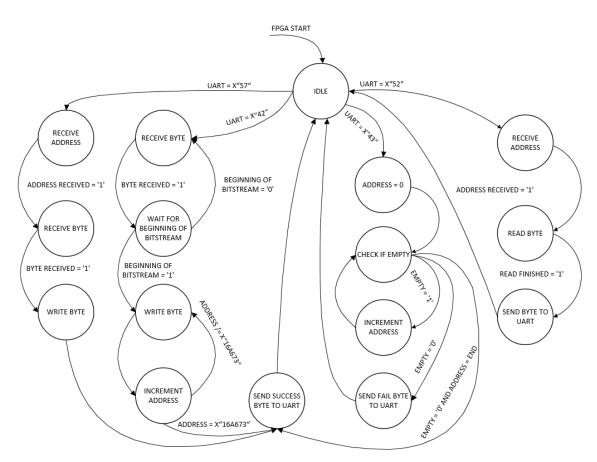

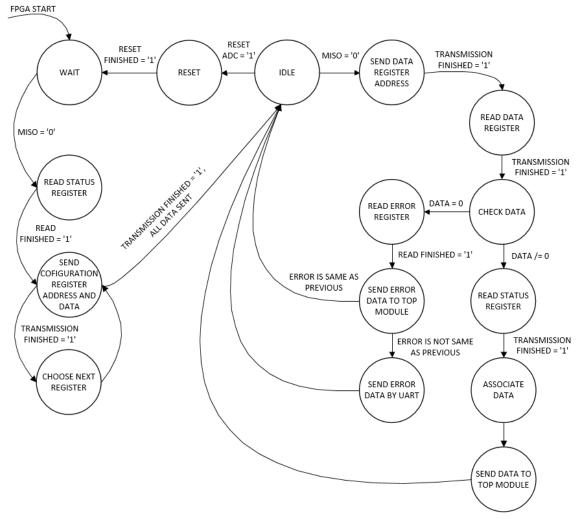

The MRAM controller is responsible for interaction with MRAM memories. It can erase the memories, write and read user data, and store bitstream for FPGA's configuration. The complete state machine is shown in Figure 25.

The write mode is selected by command  $57_{16}$ . Then the user sends three bytes to select desired address. The controller sets the address on output and waits for a data byte. The writing process is carried out in several steps, each of them lasts for 5  $\mu$ s. In the first step, the Chip Enable is pulled down to enable the MRAM. In the next step, the data byte is set to output and Write enable is pulled down. The controller waits another step to ensure the data are written properly. The "success" byte  $53_{16}$  is sent to the user at the end of the write cycle.

The bitstream store mode works in a similar way. The mode is selected by command  $42_{16}$ . The controller sets the address to zero and waits for two FF<sub>16</sub> bytes which signalize the beginning of bitstream. Then the controller increments the address every time a new byte is written. The write cycle ends when the address gets to value  $16A673_{16}$ , which is

a fixed size of the bitstream, and the "success" byte is sent. The bitstream must be binary, without swapped bits, and without compression.

To erase the memory, the user sends command  $45_{16}$ , the controller sets the address to zero and writes  $00_{16}$  byte. Then increments the address and repeats the cycle. The process is finished when the address reaches the end.

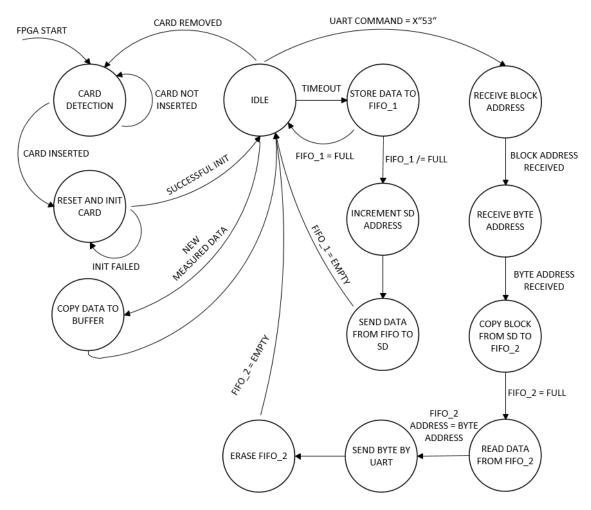

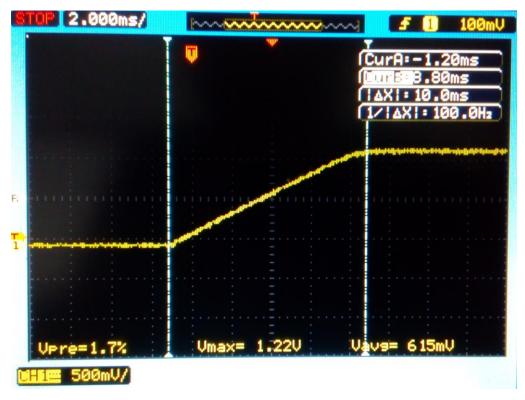

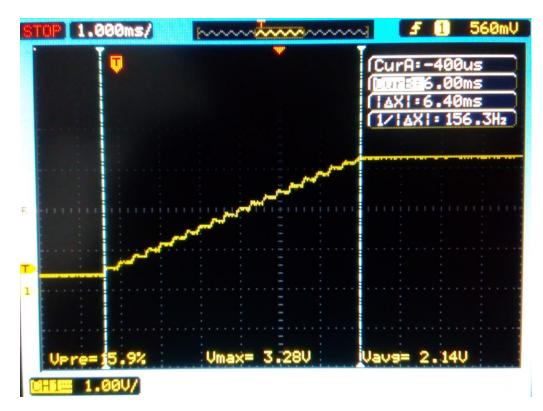

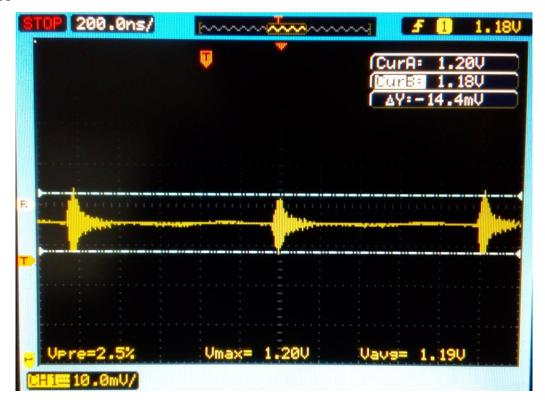

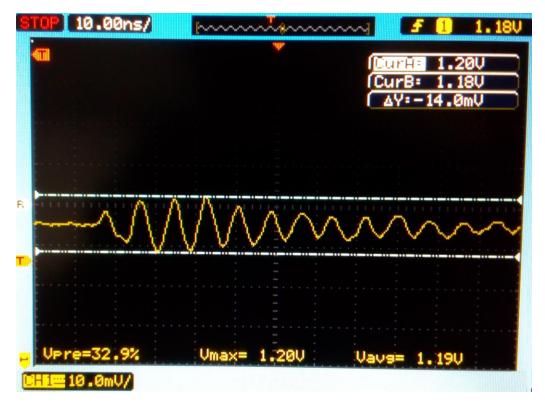

The read mode is selected by command  $52_{16}$ . Then the user sends three bytes to select desired address. The controller sets the address on output and starts the read cycle. As the writing process, data reading is carried out in several steps, each of them lasts for  $5 \mu s$ . In the first step, the Chip Enable is pulled down to enable the MRAM. In the next step, the Output enable is pulled down. The controller waits another step to ensure that the valid data are on the MRAM's output. Then the data are read and sent to the user.