# VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

#### FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

#### ÚSTAV TELEKOMUNIKACÍ

#### Ing. Norbert Herencsár

# NOVEL ACTIVE FUNCTION BLOCKS AND THEIR APPLICATIONS IN FREQUENCY FILTERS AND QUADRATURE OSCILLATORS

NOVÉ AKTIVNÍ FUNKČNÍ BLOKY A JEJICH APLIKACE V KMITOČTOVÝCH FILTRECH A KVADRATURNÍCH OSCILÁTORECH

### ZKRÁCENÁ VERZE PH.D. THESIS

Obor: Teleinformatika

Školitel: Doc. Ing. Ivo Lattenberg, Ph.D.

Oponenti: Prof. Ing. Pavel Zahradník, CSc.

Prof. Dr. Ing. Zdeněk Kolka

Datum obhajoby: 3.9.2010

#### **KEYWORDS**

Analog signal processing, current-mode, voltage-mode, mixed-mode, frequency filter, first-order all-pass filter, universal filter, KHN-equivalent, inverse filter, active grounded inductance simulator, quadrature oscillator, UCC, UVC, DBTA, PCA, CFTA, ZC-CFTA, CCCFTA, ZC-CCCITA, GCFDITA, CBTA, MCFOA, VGC-MCFOA, CC-VCIII-.

#### KLÍČOVÁ SLOVA

Analogové zpracování signálu, proudový mód, napěťový mód, smíšený mód, kmitočtový filtr, fázovací článek prvního řádu, univerzální filtr, KHN-ekvivalent, inverzní filtr, aktivní uzemněný induktor simulátor, kvadraturní oscilátor, UCC, UVC, DBTA, PCA, CFTA, ZC-CFTA, CCCFTA, ZC-CCCITA, GCFDITA, CBTA, MCFOA, VGC-MCFOA, CC-VCIII-.

Disertační práce je k dispozici na Vědeckém oddělení děkanátu FEKT VUT v Brně, Údolní 53, Brno, 602 00

### CONTENTS

| 1                         | State of art                                                                                     |                                                                                                  |           |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------|--|--|

| 2                         | The                                                                                              | esis objectives                                                                                  | 5         |  |  |

| 3                         |                                                                                                  | vel active building blocks and their properties                                                  | 7         |  |  |

|                           | 3.1                                                                                              | Differential-input buffered and transconductance amplifier (DBTA)                                | 7         |  |  |

|                           | 3.2<br>3.3                                                                                       | Current follower transconductance amplifier (CFTA) . Z-copy current-controlled current inverting | 8         |  |  |

|                           |                                                                                                  | transconductance amplifier (ZC-CCCITA)                                                           | 9         |  |  |

|                           | 3.4                                                                                              | Generalized current follower differential input transconductance amplifier (GCFDITA)             | 10        |  |  |

|                           | 3.5                                                                                              | Voltage gain-controlled modified current-<br>feedback operational amplifier (VGC-MCFOA)          | 11        |  |  |

|                           | 3.6                                                                                              | Minus-type current-controlled third-                                                             |           |  |  |

|                           |                                                                                                  | generation voltage conveyor (CC-VCIII–)                                                          | 11<br>12  |  |  |

| 4                         | First-order all-pass filter design 4.1 Electronically tunable resistorless all-pass filter using |                                                                                                  |           |  |  |

|                           | 1.1                                                                                              | novel voltage conveyor                                                                           | 12        |  |  |

| 5                         | Second-order multifunction and                                                                   |                                                                                                  |           |  |  |

|                           |                                                                                                  | versal filters Universal VM filter employing single DBTA                                         | 17<br>17  |  |  |

| 6                         | $\mathbf{A}\mathbf{p}_{\mathbf{j}}$                                                              | plications on grounded inductance simulators                                                     | 11<br>21  |  |  |

|                           | 6.1                                                                                              | Active-C grounded positive and negative inductor simulators in compact form                      | 21        |  |  |

| 7                         |                                                                                                  | adrature sinusoidal oscillators                                                                  | <b>25</b> |  |  |

|                           |                                                                                                  | VM SRCO design using generalized CFTA and UGVF                                                   | 25        |  |  |

| 8                         | Cor                                                                                              | nclusion                                                                                         | 29        |  |  |

| $\mathbf{B}_{\mathbf{i}}$ | bliog                                                                                            | graphy                                                                                           | 31        |  |  |

#### INTRODUCTION

Frequency filters and sinusoidal oscillators are linear electric circuits [64] that are used in wide area of electronics and also are the basic building blocks in analogue signal processing. The analogue frequency filters are the most often used as anti-aliasing video filters in the analogue sections of high-speed data communication systems defined by ITU BT 601 standard [66] or for signal processing in wireless LANs described by IEEE 802.11 standard [42], in IF (Intermediate Frequency) receiver stages of the GSM cellular telephones [23], in receiver baseband blocks of modern radio systems [52], in hard-drive communication interfaces [39], measurement systems [68], automotive industry [26], or in piezoresistive pressure sensors [54]. Oscillators also represent an important unit in many telecommunication, instrumentation and control systems [1], [3], [18], [30].

In the last decade, for analogue signal processing huge number of active building blocks were introduced. However, there is still the need to develop new active elements that offer new and better advantages. This thesis is, therefore, focused on definition of other novel ABBs and, furthermore, novel filter and oscillator structure designs.

In the present days a number of trends can be noticed in the area of analogue filter and oscillator design, namely reducing the supply voltage of integrated circuits and transition to the current-mode [64]. On the other hand, voltage- and mixed-mode circuit design still receive considerable attention of many researchers. Therefore, the proposed circuits in this work are working in current-, voltage-, or mixed-mode.

#### 1 STATE OF ART

Nowadays, the presented structures of active frequency filters and oscillators are often employing current conveyors (CCs), where the second-generation current conveyor (CCII) [56] is the most popular. The CCII is the basic block of many other active elements. Here, the current-feedback operational amplifier (CFOA) [22], [61] that is a combination of the CCII and voltage follower (VF) [55] or the composite current conveyor (CCC) [59] that is the interconnection of the plus-type and minus-type CCIIs can be mentioned. Recently, based on the CCC the modified CFOA (MCFOA) [70] was reported. Later, the inverting second-generation current conveyor (ICCII) as a missing building block in analogue signal processing techniques has been introduced [4]. By the combination of CCII and ICCII the dual-X second-generation current conveyor (DXCCII) [72] for the tunable continuous-time filter design has been built. Recently, further research

has focused on CCs with variable current and/or voltage gains such as electronically tunable second-generation current conveyor (ECCII) [46], variable gain current conveyor (VGCCII) [71], or voltage and current gain second-generation current conveyor (VCG-CCII) [20].

Using the duality principle, the voltage conveyor (VC) has been presented in 1981 [27]. As in the theory of CCs, also here the first- and second-generation VCs (VCI, VCII, IVCI, and IVCII) were described [27], [21], [47]. The best known VC is the plus-type differential current voltage conveyor (DCVC+) [53] that is more often labelled as the current differencing buffered amplifier (CDBA) [2]. Recently, the current-controlled CDBA (C-CDBA), the current-controlled inverting CDBA (C-ICDBA), and the z copy-controlled gain-CDBA (ZC-CG-CDBA) [8] have also been introduced [44]. By the modification of the CDBA or replacement of the VF by the operational transconductance amplifier (OTA) [29] the differential-input current feedback amplifier (DCFA) [73], and current differencing transconductance amplifier (CDTA) [7] have been presented.

Based on the idea of the "universal" active element [17] the universal current conveyor (UCC) [5], [14], [85] was designed and developed as a sample series containing 50 pieces, using the CMOS 0.35  $\mu$ m technology, under the designation UCC-N1B 0520 at our workplace, and produced in cooperation with AMI Semiconductor Czech, Ltd., (now ON Semiconductor Czech Republic, Ltd.). On the basis of the UCC, the universal voltage conveyor (UVC) was designed [15], [47], [75], [88]–[91], and produced under the designation UVC-N1C 0520. The realizable generations and types of VCs using the UVC were shown by Minarcik and Vrba in [47].

#### 2 THESIS OBJECTIVES

In the last decade, for analogue signal processing huge number of active building blocks (ABBs) were introduced, however, there is still a need to develop new active elements that offer new and better advantages. Therefore, the main aim of this thesis is to define various types of novel active building blocks. The first intention is to define such novel more-terminal ABB with low-impedance current/high-impedance voltage inputs and high-impedance current/low-impedance voltage outputs, which will belong to the group of "universal" active elements, e.g. UCC and UVC. Special attention will be paid on active element with only current inputs and outputs. From the cascadability point of view, ABBs with low-input and high-output impedance terminals are the most interesting. The proposed active element will be further studied

and, if possible, modified according to special needs.

In the present days a number of trends can be noticed in the area of active function block design. The attention is also focused on ABBs with tunability property. Here the current or voltage gain tuning can be mentioned. Hence, part of this work is focused on such novel ABB design that voltage gain can be controlled by means of external current.

Voltage conveyors are also important and useful elements in analogue signal processing, however, their potentials are still not enough studied. Therefore, special attention will be also paid on novel VC design with tunability feature.

The main part of the thesis will concentrate on application possibilities of the defined functional blocks. First-order all-pass filters are widely used in analogue signal processing. Several current-mode (CM), voltage-mode (VM), or mixed-mode first-order AP filter realizations using different active building blocks have been reported in the literature. These topologies realize either inverting or non-inverting type of filters. For realizing the complementary type, they need to change the circuit topology. Furthermore, most of the reported realizations do not include electronical tunability property. Hence, the intention is to propose such AP filters that enable both the inverting and the non-inverting type AP filter responses simultaneously and easy tunability of the natural frequency.

Part of this work focuses on such second-order filter structures that can provide all standard filter responses without changing the circuit topology. Special attention is paid to Kerwin-Huelsman-Newcomb structure that enables mutually independent control of the quality factor Q and characteristic frequency  $\omega_0$ .

Due to disadvantages of conventional inductors, active element-based inductor design is very desirable to designers today. During the last few decades, various grounded inductors have been created using different high-performance active building blocks. However, they employ excessive number of active and passive components. Thus, the aim is to create single grounded capacitor-based positive grounded inductor simulator in compact form.

Quadrature oscillators also represent an important unit in many communication, control systems, instrumentation and measurement systems. Therefore, part of this work attempts this issue.

In the first step the theoretical analyses are done using SNAP software [38]. To verify the behavior of the proposed circuits, defined active elements are implemented using bipolar or CMOS internal structures. The feasibility of selected circuits are also confirmed by experimental measurements.

# 3 NOVEL ACTIVE BUILDING BLOCKS AND THEIR PROPERTIES

This Chapter presents different novel active elements, where all of them have been introduced and developed within this work at the Department of Telecommunications, Brno University of Technology. These active building blocks (ABBs) are further used in this work for various filter and oscillator designs.

# 3.1 Differential-input buffered and transconductance amplifier (DBTA)

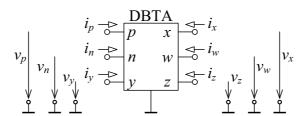

The differential-input buffered and transconductance amplifier (DBTA) [76], [77], [79], [80], [87], was introduced at our Department in 2009 and it belongs to the group of "universal" active elements presented above. It is a six-port active element, which schematic symbol is shown in Fig. 3.1. It has low-impedance current inputs p, n and high-impedance voltage input y. The difference of the  $i_p$  and  $i_n$  currents flows into auxiliary terminal z. The voltage  $v_z$  on this terminal is transferred into output terminal w using the VF [55] and also transformed into current using the transconductance  $g_m$ , which flows into output terminal x.

Fig. 3.1: Schematic symbol of DBTA

Relations between the individual terminals of the non-ideal DBTA can be described by following hybrid matrix:

$$\begin{bmatrix} v_p \\ v_n \\ i_y \\ i_z \\ v_w \\ i_x \end{bmatrix} = \begin{bmatrix} 0 & 0 & \beta_p & 0 & 0 & 0 \\ 0 & 0 & \beta_n & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 \\ \alpha_p & -\alpha_n & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & \gamma & 0 & 0 \\ 0 & 0 & 0 & \pm g_m & 0 & 0 \end{bmatrix} \begin{bmatrix} i_p \\ i_n \\ v_y \\ v_z \\ i_w \\ v_x \end{bmatrix},$$

(3.1)

where  $\alpha_p = 1 - \varepsilon_i$ ,  $\alpha_n = 1 - \varepsilon_i$  and  $\varepsilon_i$  ( $|\varepsilon_i| \ll 1$ ) are the current tracking errors from p and n terminals to z terminal,  $\beta_p = 1 - \varepsilon_v$ ,

$\beta_n = 1 - \varepsilon_v$  and  $\varepsilon_v$  ( $|\varepsilon_v| \ll 1$ ) are the voltage tracking errors from p and n terminals to z terminal and  $\gamma = 1 - \varepsilon_v$  and  $\varepsilon_v$  ( $|\varepsilon_v| \ll 1$ ) is the voltage tracking error from z terminal to w terminal of DBTA, respectively.

#### 3.2 Current follower transconductance amplifier (CFTA)

When the CDTA has been introduced in 2003 [7], it has been considered to be a versatile active building block for current-mode signal processing circuits. Analogous to the CDBA [2], the input circuitry of the CDTA is also formed by the CDU, which is followed by the OTA [29]. In the point of view of the low power dissipation and manufacturing cost, it is important to keep the internal structure transistor count and the count of ABBs at minimum. The earlier reported circuits in [7], [6], [62], [67], do not fully use the potential of the CDTAs, since one of the input terminals p or n is not used. This may cause some noise injection into the monolithic circuit [35]. Thus, to avoid this problem, the CDTA has been simplified by replacing the CDU by a simple current follower (CF) or inverter (CI). The appropriate novel ABBs are called current follower transconductance amplifier (CFTA) [12], [74], [81], [83], and inverted current follower transconductance amplifier (ICFTA) [82], which was in [12] also introduced as current inverter transconductance amplifier (CITA).

The generalized CFTA (GCFTA) element consists of an input CF (positive or negative) that transfers the input current to the z terminal and a dual-output OTA stage, which is used to convert the voltage at the z terminal to dual-output currents [86]. The transconductance parameter  $g_m$  corresponds for the positive output and  $-g_m$  for the negative output. In general, the equations describing an ideal GCFTA (Fig. 3.2) are:

$$\begin{bmatrix} v_f \\ i_z \\ i_{x1} \\ i_{x2} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ a & 0 & 0 & 0 \\ 0 & b_1 g_m & 0 & 0 \\ 0 & b_2 g_m & 0 & 0 \end{bmatrix} \begin{bmatrix} i_f \\ v_z \\ v_{x1} \\ v_{x2} \end{bmatrix},$$

(3.2)

$$\frac{i_f}{f} \xrightarrow{\text{GCFTA}} \underbrace{i_{x1}}_{x_1} \xrightarrow{i_{x2}} \underbrace{i_{x2}}_{x_2} \xrightarrow{i_{x2}} \underbrace{i_{x2}}_{x_1}$$

Fig. 3.2: Schematic symbol of GCFTA

where  $a, b_1, b_2 \in \{1, -1\}.$

# 3.3 Z-copy current-controlled current inverting transconductance amplifier (ZC-CCCITA)

The ZC-CCCITA (z-copy current-controlled current inverting transconductance amplifier) is recently presented ABB at our Department [84], which is a derivative of the conventional ZC-CITA [9]. It essentially consists of an input negative current-controlled current follower (i.e. current-controlled current inverter) stage that transfers the input current to the z and zc terminals and a transconductance amplifier stage, which converts the voltage at the z terminal to output current at the z terminal. The circuit symbol of ZC-CCCITA is shown in Fig. 3.3 and the hybrid matrix is as follows:

$$\begin{bmatrix} v_f \\ i_z \\ i_{zc} \\ i_{x+} \\ i_{x-} \end{bmatrix} = \begin{bmatrix} R_f & 0 & 0 & 0 & 0 \\ -1 & 0 & 0 & 0 & 0 \\ -1 & 0 & 0 & 0 & 0 \\ 0 & g_m & 0 & 0 & 0 \\ 0 & -g_m & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} i_f \\ v_z \\ v_{zc} \\ v_{x+} \\ v_{x-} \end{bmatrix}.$$

(3.3)

In (3.3), the intrinsic resistance  $R_f$  and the transconductance  $g_m$  can be defined as:

$$R_f = \frac{V_{\rm T}}{2I_{\rm O}}$$

and  $g_m = \frac{I_{\rm B}}{2V_{\rm T}}$ , (3.4)

respectively. Here the  $V_{\rm T}$  is the thermal voltage (approximately 26 mV at 27°C), the  $I_{\rm O}$  is the bias current to control the intrinsic resistance of the input terminal f, and the  $I_{\rm B}$  is the control current adjusting the transconductance  $g_m$  of the ZC-CCCITA.

Fig. 3.3: Schematic symbol of ZC-CCCITA

# 3.4 Generalized current follower differential input transconductance amplifier (GCFDITA)

In one of more recent publication [11], authors introduced a modified version of the GCFTA [82] with buffered voltage outputs wherein the transconductance of conventional GCFTA is changed to differential input transconductance amplifier. Here presented new ABB is called generalized current follower differential input transconductance amplifier (GCFDITA), which is a derivative of the circuit presented in [11]. Compared to [11], the new ABB does not have a buffered voltage output terminal.

The generalized current follower differential input transconductance amplifier (GCFDITA) consists of an input positive or negative current follower that transfers the input current at terminal f to the z terminal and a balanced-output differential input transconductance amplifier (BO-DITA) stage, which is used to convert the difference voltage between the z and v terminals to balanced output currents. The transconductance parameter  $g_m$  corresponds for the positive output and  $-g_m$  for the negative output. The schematic symbol of GCFDITA is shown in Fig. 3.4. In general, the hybrid matrix characterizing an ideal GCFDITA is:

where  $a \in \{1, -1\}$  and  $g_m = \frac{I_B}{2V_T}$ . Here the  $V_T$  is the thermal voltage (approximately 26 mV at 27°C) and the  $I_B$  and is control current adjusting the transconductance  $g_m$ . Depending on the values of a, two variants of GCFDITA are possible, namely current follower differential input transconductance amplifier (CFDITA) for a = 1 and current inverter differential input transconductance amplifier (CIDITA) for a = -1.

$$\begin{array}{c|c}

i_f & GCFDITA & i_{x+} \\

f & x+ & O \\

\hline

z & v & V

\end{array}$$

Fig. 3.4: Schematic symbol of GCFDITA

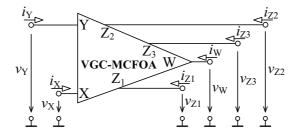

### 3.5 Voltage gain-controlled modified currentfeedback operational amplifier (VGC-MCFOA)

The voltage gain-controlled MCFOA (VGC-MCFOA) (Fig. 3.5) is recently presented ABB at our Department, which is a derivative of the MCFOA presented in [69]. Relations between the individual terminals of the VGC-MCFOA can be described by the following hybrid matrix:

$$\begin{bmatrix} i_{\rm Y} \\ i_{\rm Z1} \\ i_{\rm Z2} \\ i_{\rm Z3} \\ v_{\rm W} \end{bmatrix} = \begin{bmatrix} -\alpha_1 & 0 & 0 & 0 & 0 & 0 \\ 0 & \alpha_2 & 0 & 0 & 0 & 0 \\ 0 & -\alpha_3 & 0 & 0 & 0 & 0 \\ \alpha_4 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & h\beta_1 & 0 & 0 & 0 \\ 0 & 0 & 0 & \beta_2 & 0 & 0 \end{bmatrix} \begin{bmatrix} i_{\rm W} \\ i_{\rm X} \\ v_{\rm Y} \\ v_{\rm Z1} \\ v_{\rm Z2} \\ v_{\rm Z3} \end{bmatrix},$$

(3.6)

where  $\alpha_j = 1 - \varepsilon_{ij}$  and  $\beta_k = 1 - \varepsilon_{vk}$  (j = 1, 2, 3 and k = 1, 2) are the non-ideal current and voltage gains, respectively, and  $\varepsilon_{ij}$   $(|\varepsilon_{ij}| \ll 1)$  and  $\varepsilon_{vk}$   $(|\varepsilon_{vk}| \ll 1)$  denote current and voltage tracking errors of the VGC-MCFOA, respectively. The presented novel ABB can be easily electronically tuned by means of the voltage gain h.

Fig. 3.5: Schematic symbol of VGC-MCFOA

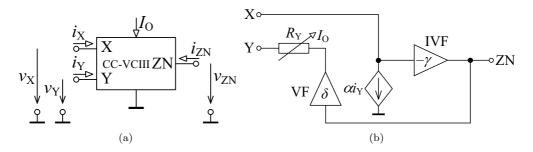

### 3.6 Minus-type current-controlled thirdgeneration voltage conveyor (CC-VCIII-)

The minus-type current-controlled third-generation voltage conveyor (CC-VCIII—) is a novel three-port building block with electronic tuning, which schematic symbol and behavioral model are shown in Fig. 3.6 [78]. The current through the X terminal follows the current of the Y terminal. The voltage of the Y terminal follows the voltage of the X terminal. Finally, the voltage of the ZN terminal follows the inverted voltage of the X terminal. The intrinsic resistance of Y terminal can be easily controlled by means of external control current  $I_{\rm O}$ , which

Fig. 3.6: (a) Schematic symbol and (b) behavioral model of CC-VCIII-

makes the introduced ABB attractive for resistorless and electronically controllable linear circuit applications. Relations between the individual terminals of the non-ideal CC-VCIII— can be described by the following hybrid matrix:

$$\begin{bmatrix} i_{X} \\ v_{Y} \\ v_{ZN} \end{bmatrix} = \begin{bmatrix} 0 & \alpha & 0 \\ \delta & R_{Y} & 0 \\ -\gamma & 0 & 0 \end{bmatrix} \begin{bmatrix} v_{X} \\ i_{Y} \\ i_{ZN} \end{bmatrix}, \tag{3.7}$$

where  $\alpha = 1 - \varepsilon_i$ ,  $\delta = 1 - \varepsilon_{v1}$ , and  $\gamma = 1 - \varepsilon_{v2}$ . Here, the  $R_Y$  is the intrinsic resistance of the y terminal,  $\varepsilon_i$  ( $|\varepsilon_i| \ll 1$ ) and  $\varepsilon_{v1}$ ,  $\varepsilon_{v2}$  ( $|\varepsilon_{v1}|$ ,  $|\varepsilon_{v2}| \ll 1$ ) denote current and voltage tracking errors of CC-VCIII—, respectively.

#### 4 FIRST-ORDER ALL-PASS FILTER DESIGN

First-order all-pass (AP) filters are widely used in analogue signal processing in order to shift the phase of an electrical signal while keeping its amplitude constant. First proposed AP filters employing op-amps suffer from the well-known limitations of opamp-based circuits such as frequency limitations, the use of a large number of passive elements and lack of electronic tuning [50]. Therefore, to eliminate these disadvantages, other types of active elements have started to be used for AP filter design. They also play a great role in the design of other types of active circuits such as quadrature or multiphase oscillators and high-Q band-pass filters [16], [25], [63].

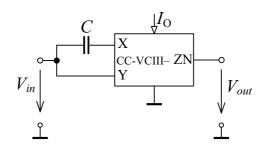

# 4.1 Electronically tunable resistorless all-pass filter using novel voltage conveyor

Nowadays, as already mentioned, the electronically tunable resistorless VM all-pass filters receive considerable attention. In current tech-

Fig. 4.1: Proposed electronically tunable resistorless first-order all-pass filter

nical literature huge number of such filters are presented, where the tunability feature of circuits used are solved in different ways. For example, in recently presented voltage differencing-differential input buffered amplifier (VD-DIBA)-based VM all-pass filter [10] the tunability property of the OTA is used to shift the phase response of the circuit. Another technique is given in [43], where the appropriate resistor is replaced via MOSFET-based VCR. After the CCCII [24] was introduced, a new period has been opened with respect to electronical tunability in the analog filter design. Here the intrinsic X-input resistance of the CCCII is controlled via an external current, as shown in [45]. The same technique is adapted to the novel type of voltage conveyor, namely CC-VCIII— [78], where analogously the input circuitry is formed by the CCCII.

The novel VM all-pass filter using canonic number of passive and active elements (i.e. single capacitor, and single CC-VCIII–) is shown in Fig. 4.1 [78]. Considering the ideal CC-VCIII– (i.e.  $\alpha$ ,  $\delta$ , and  $\gamma$  are unity), routine analysis yields voltage transfer function in following form:

$$T(s) = \frac{V_{out}}{V_{in}} = -\frac{sCR_{\rm Y} - 1}{sCR_{\rm Y} + 1}.$$

(4.1)

From (4.1), the phase of the filter is found as:

$$\varphi(\omega) = -2\operatorname{arctg}(\omega C R_{Y}),$$

(4.2)

and the natural frequency  $\omega_0$  can be express as:

$$\omega_0 = \frac{1}{CR_{\rm V}}.\tag{4.3}$$

Taking into account the non-idealities of the CC-VCIII–, the TF in (4.1) converts to:

$$T(s) = \frac{V_{out}}{V_{in}} = -\frac{\gamma(sCR_{Y} - \alpha)}{sCR_{Y} + \alpha\delta\gamma},$$

(4.4)

Assuming that all of the nonideal gains are constant in our frequency range of interest, the phase response of the filter is given as:

$$\varphi(\omega) = -\operatorname{arctg}\left(\frac{\omega C R_{Y}}{\alpha}\right) - \operatorname{arctg}\left(\frac{\omega C R_{Y}}{\alpha \delta \gamma}\right).$$

(4.5)

From (4.4) and (4.5) it can be seen that the non-idealities of the CC-VCIII—slightly affect the magnitude and phase responses of the filter. Consequently, the pole frequency of the presented filter is found as:

$$\omega_0 = \frac{\alpha \delta \gamma}{CR_{\rm Y}},\tag{4.6}$$

and the active and passive sensitivities of  $\omega_0$  are given as:

$$S_{\alpha}^{\omega_0} = S_{\delta}^{\omega_0} = S_{\gamma}^{\omega_0} = 1, \quad S_C^{\omega_0} = S_{R_Y}^{\omega_0} = -1.$$

(4.7)

From Eq. (4.7) it is evident that all sensitivities of active parameters and passive components for  $\omega_0$  are unity in relative amplitude. Hence, the proposed filter shows low sensitive performance.

For a complete analysis of the circuit, it is also important to take into account parasitic impedances of the CC-VCIII—. Therefore, the matrix relationship of (3.7) changes as follows:

$$\begin{bmatrix} i_{\mathbf{X}} \\ v_{\mathbf{Y}} \\ v_{\mathbf{ZN}} \end{bmatrix} = \begin{bmatrix} sC_{\mathbf{X}} + \frac{1}{R_{\mathbf{X}}} & \alpha & 0 \\ \delta & R_{\mathbf{Y}} & 0 \\ -\gamma & 0 & sC_{\mathbf{ZN}} + \frac{1}{R_{\mathbf{ZN}}} \end{bmatrix} \begin{bmatrix} v_{\mathbf{X}} \\ i_{\mathbf{Y}} \\ i_{\mathbf{ZN}} \end{bmatrix}. \tag{4.8}$$

Here  $R_X$ ,  $R_{ZN}$ ,  $C_X$ , and  $C_{ZN}$  are the parasitic resistances and capacitances at their relevant terminals. Considering these parasitics of the all-pass filter in Fig. 4.1, the ideal TF of (4.1) turns to be:

$$T(s) = \frac{V_{out}}{V_{in}} = -\frac{\gamma R_{X}(sCR_{Y} - \alpha)}{R_{Y}R_{X}s(C + C_{x}) + R_{Y} + \alpha\delta\gamma R_{X}},$$

(4.9)

where  $R_X$  and  $C_X$  denote parasitic resistance and capacitance at X terminal of the CC-VCIII—. Note that the parasitic capacitance  $C_X$  can be absorbed into the external capacitor as it appears in parallel with it. If  $R_Y$  is sufficiently higher than  $R_X$  and  $C\gg C_X$ , the TF in (4.9) become to form presented in (4.4).

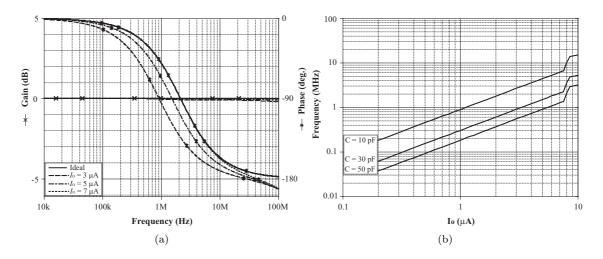

Using the CMOS implementation of the CC-VCIII–, the proposed circuit in Fig. 4.1 has been simulated in SPICE software. The transistors are modeled by the TSMC 0.35  $\mu$ m CMOS process parameters. The DC power supply voltages are equal to  $\pm 2.5$  V and  $V_{\rm B} = -1.7$  V. Fig. 4.2(a) shows the ideal and simulated phase and gain responses il-

Fig. 4.2: a) Electronical tunability of gain and phase responses by the bias current  $I_{\rm O}$ , (b) possibility of tuning the pole frequency by the bias current  $I_{\rm O}$  at different values of C

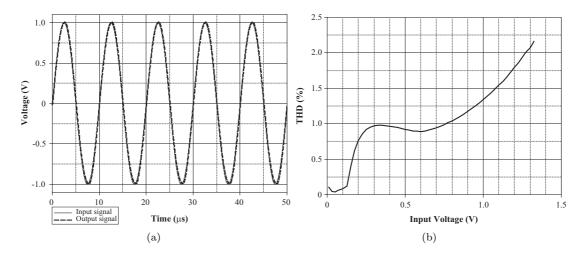

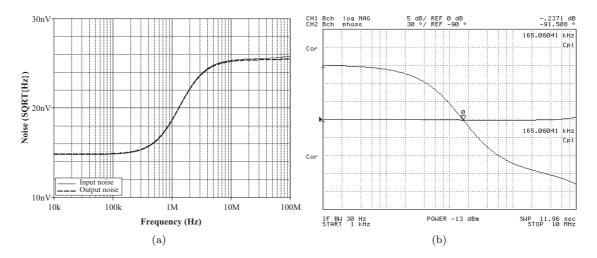

lustrating the electronic tunability for C = 30 pF. The pole frequency of the proposed filter is varied for  $f_0 \approx \{0.908; 1.52; 2.12\}$  MHz using the bias current  $I_{\rm O} = \{3; 5; 7\} \mu A$ , respectively. Similarly, possibility of tuning the pole frequency by the bias current  $I_{\rm O}$  at three different values of C is shown in Fig. 4.2(b). To illustrate the time-domain performance, transient analysis is performed to evaluate the voltage swing capability and phase errors of the filter as shown in Fig. 4.3(a). A sinewave input of 1 V amplitude and frequency of 100 kHz was applied to the filter while keeping the bias current  $I_0 = 5 \mu A$  and C = 30 pF. Note that the output waveform is very close to the input one. The THD variation with respect to amplitude of the applied sinusoidal input voltage at 100 kHz (filter parameter:  $I_{\rm O} = 5 \,\mu{\rm A}$  and  $C = 30 \,{\rm pF}$ ) is shown in Fig. 4.3(b). The THD rapidly increases when the input signal is increased beyond 0.7 V amplitude. An input with the amplitude of 1 V yields THD value of 1.34%. Using the INOISE and ONOISE statements, the input and output noise behavior with respect to frequency has also been simulated, as it is shown in Fig. 4.4(a). The equivalent input and output noises at pole frequency ( $f_0 \cong 1.52 \text{ MHz}$ ) are found as 20.83 and 20.82  $\text{nV}/\sqrt{\text{Hz}}$ , respectively. The total power dissipation of the proposed all-pass filter at  $f_0 \approx 1.52$  MHz is found to be 15.6 mW.

In order to confirm the simulation results, the behavior of the proposed all-pass filter has also been verified by experimental measurements. In the measurements the UVC-N1C 0520 [60], [88] integrated circuit has been used. The capacitor value has been chosen as 1 nF and the intrinsic resistance value of the Y terminal has been selected as 1 k $\Omega$ . In this case a 90° phase shift is at  $f_0 \cong 159.15$  kHz. In the

Fig. 4.3: (a) Time-domain responses of the proposed all-pass filter at  $100~\mathrm{kHz}$ , (b) THD of the all-pass filter at  $100~\mathrm{kHz}$

Fig. 4.4: (a) Input and output noise variations versus frequency, (b) measured gain and phase characteristics of the proposed VM first-order all-pass filter

measurements the network analyzer Agilent 4395A has been used and the results are shown in Fig. 4.4(b). The real behavior of the filter corresponds to theory well.

### 5 SECOND-ORDER MULTIFUNCTION AND UNIVERSAL FILTERS

In the present days the highest attention is paid on such second-order filter structures that can provide at least the basic three standard filter functions, i.e. low-, band-, high-pass or all standard (also band-stop and all-pass) filter responses without changing the circuit topology. Such circuit topologies are called multifunction or universal filters, respectively. Probable the best known multifunction filtering structure is the KHN (Kerwin–Huelsman–Newcomb) that, furthermore, enables mutually independent control of the quality factor Q and characteristic frequency  $\omega_0$  [34]. This Chapter is focused on this issue.

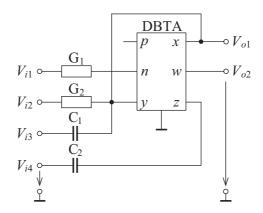

#### 5.1 Universal VM filter employing single DBTA

This Section presents the application possibilities of the recently defined DBTA in VM universal filter. The proposed VM second-order filtering structure employing single DBTA and four passive components is shown in Fig. 5.1 [80]. Note that even if all passive elements are shown as floating, which might be not attractive for integration [13], it should be mentioned that unused voltage inputs are always grounded, as described below.

Fig. 5.1: Proposed voltage-mode universal filter using single DBTA

The output voltages  $V_{o1}$  and  $V_{o2}$  of this circuit are given by the relations:

$$V_{o1} = \frac{G_1 g_m V_{i1} + s C_2 G_2 V_{i2} + s^2 C_1 C_2 V_{i3} - s C_2 g_m V_{i4}}{D}, \qquad (5.1)$$

$$V_{o1} = \frac{\begin{bmatrix} -(sC_1G_1 + G_1G_2)V_{i1} + G_1G_2V_{i2} + \\ +sC_1G_1V_{i3} + (s^2C_1C_2 + sC_2G_2)V_{i4} \end{bmatrix}}{D},$$

(5.2)

where

$$D = s^2 C_1 C_2 + s C_2 G_2 + G_1 q_m. (5.3)$$

For the proposed filter depending on the status of circuit input four voltages  $V_{i1}$ ,  $V_{i2}$ ,  $V_{i3}$  and  $V_{i4}$  numerous filter functions are obtained. Based on the output selected there are two cases shown as presented below:

Case I. If the  $V_o = V_{o1}$  is used as output, then from (5.1) the realizable transfer functions in voltage mode are:

- (i) If  $V_{i2} = V_{i3} = V_{i4} = 0$  (grounded), a low-pass filter (LP1) can be obtained with  $V_o/V_{i1}$ ;

- (ii) If  $V_{i1} = V_{i3} = V_{i4} = 0$  (grounded), a band-pass filter (BP1) can be obtained with  $V_o/V_{i2}$ ;

- (iii) If  $V_{i1} = V_{i2} = V_{i4} = 0$  (grounded), a high-pass filter (HP1) can be obtained with  $V_o/V_{i3}$ ;

- (iv) If  $V_{i1} = V_{i2} = V_{i3} = 0$  (grounded), a band-pass filter (BP2) can be obtained with  $V_o/V_{i4}$ ;

- (v) If  $V_{i2} = V_{i4} = 0$  (grounded) and  $V_{i1} = V_{i3} = V_{in}$ , a band-stop filter (BS) can be obtained with  $V_o/V_{in}$ ;

- (vi) If  $V_{i1} = 0$  (grounded) and  $V_{i2} = V_{i3} = V_{i4} = V_{in}$ , an all-pass (AP) can be obtained with  $V_o/V_{in}$ .

In this case the proposed circuit is universal and can provide all standard types of filter functions, i.e. low-, band-, high-pass, bandstop, and an all-pass response without changing the circuit topology.

Case II. If the  $V_o = V_{o2}$  is used as output, then from (5.2) the realizable transfer functions in voltage mode are:

- (vii) If  $V_{i1} = V_{i3} = V_{i4} = 0$  (grounded), a low-pass filter (LP2) can be obtained with  $V_o/V_{i2}$ ;

- (viii) If  $V_{i1} = V_{i2} = V_{i4} = 0$  (grounded), a band-pass filter (BP3) can be obtained with  $V_o/V_{i3}$ ;

- (ix) If  $V_{i3} = 0$  (grounded) and  $V_{i1} = V_{i2} = V_{i4} = V_{in}$ , a high-pass filter (HP2) can be obtained with  $V_o/V_{in}$ .

Thus, the circuit is multifunction and it is capable of realizing low-, band- and high-pass response without changing the circuit topology. In case of HP2 response the proposed circuit requires component matching conditions  $C_1 = C_2$  and  $G_1 = G_2$ .

For all filters the natural frequency  $\omega_0$ , quality factor Q and band-

width BW derived from (5.3) are:

$$\omega_0 = \sqrt{\frac{G_1 g_m}{C_1 C_2}}, \ Q = \frac{1}{G_2} \sqrt{\frac{C_1 G_1 g_m}{C_2}}, \ \text{BW} = \frac{\omega_0}{Q} = \frac{G_2}{C_1}.$$

(5.4)

Note that the quality factor Q can be controlled independently of natural frequency  $\omega_0$  by  $G_2$ . By replacing appropriate conductor by FET-based VCR [31], [58], the quality factor Q can be controlled electronically, which is particular advantage of the proposed circuit. The natural frequency  $\omega_0$  can be independently adjusted from the bandwidth, by varying  $C_2$ ,  $G_1$  or  $g_m$  of the proposed frequency filter. Here, the appropriate capacitor can be replaced by a voltage-controlled capacitor (VCC) [41], [48], or by digitally-controlled varactor (DCV) [19] for electronical control of the natural frequency  $\omega_0$  independently from the bandwidth.

The relative sensitivities of the  $\omega_0$ , Q and BW parameters of the designed circuit derived from (5.4) are:

$$S_{G_1,g_m}^{\omega_0} = -S_{C_1,C_2}^{\omega_0} = \frac{1}{2}, \quad S_{G_2}^{\omega_0} = 0,$$

$$S_{C_1,G_1,g_m}^Q = -S_{C_2}^Q = \frac{1}{2}, \quad S_{G_2}^Q = -1,$$

$$S_{G_2}^{\text{BW}} = -S_{C_1}^{\text{BW}} = 1, \quad S_{C_2,G_1,g_m}^{\text{BW}} = 0.$$

$$(5.5)$$

From the results it is evident that the sensitivities are low and not larger than unity of absolute value.

Taking into account the non-idealities of DBTA and assuming the transconductance  $g_m$  of its OTA as follows [65]:

$$g_m = \frac{g_m \omega_g}{s + \omega_q} \cong g_m (1 - \mu s), \tag{5.6}$$

where  $\omega_g$  is the first-pole of the OTA and  $\mu = 1/\omega_g$ , the denominator of (5.1), (5.2) becomes:

$$D = s^{2}C_{1}C_{2} + sC_{2}G_{2}\left(1 - \frac{\alpha_{n}\beta_{n}G_{1}g_{m}\mu}{C_{2}G_{2}}\right) + \alpha_{n}\beta_{n}G_{1}g_{m}.$$

(5.7)

Due to the parasitic effect, the characteristic departs from the ideal responses. But, the parasitic effect can be made negligible satisfying the following condition:

$$\frac{\alpha_{\rm n}\beta_{\rm n}G_1g_m\mu}{C_2G_2} \ll 1. \tag{5.8}$$

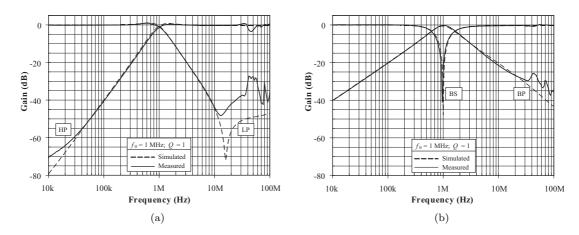

Fig. 5.2: Simulated and measured frequency characteristics for: (a) LP1 and HP1, (b) BP2 and BS responses of the proposed circuit of Fig. 5.1

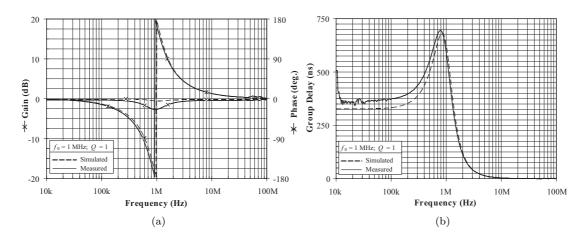

Fig. 5.3: Simulated and measured frequency responses of the all-pass (AP) filter: (a) gain and phase responses, (b) group delay response

Using the bipolar implementation of the DBTA, the proposed universal filter structure (Case~I) has been designed for characteristic frequency  $f_0 \approx 1$  MHz and the quality factor of filters Q=1, and simulated in SPICE software. The following values have been chosen:  $C_1 = C_2 = 150$  pF,  $G_1 = G_2 = 1$  mA/V ( $R_1 = R_2 = 1$  k $\Omega$ ) and  $g_m = 1$  mA/V ( $I_B = 50~\mu$ A). For the practical measurements the DBTA has been implemented by using commercially available amplifiers. The simulation and measurement results of the low- (LP1), band- (BP2), high-pass (HP1), band-stop (BS), and all-pass (AP) frequency filter working in voltage mode are shown in Fig. 5.2 and Fig. 5.3. From the results it is evident that the results of the measurements are in agreement with the simulations. In the higher-frequency region the real properties of the amplifiers and parasitic capacities or inductances of the constructed prototypes begin to be more significant.

### 6 APPLICATIONS ON GROUNDED INDUCTANCE SIM-ULATORS

Conventional spiral inductors are too big, too heavy, too costly, and they require tuning. Due to these disadvantages, active element-based inductor design is very desirable to designers today. The positive inductance simulators (PIS) can be used in many applications such as active filter design, oscillator design, analog phase shifters and cancellation of parasitic element [32]. Not only the PIS, but also a negative inductance simulator (NIS) plays an importance role in cancellation/compensation of parasitic inductances. Actively simulated NISs also find in several applications such as in microwave circuits for impedance matching, in chaotic oscillations, in antenna to minimize reflection at the input so that it provides a better radiation pattern, to compensate bond wire inductance which is an increasing problem in high-speed/low-power integrated circuits because of reduced noise margin and cancellation of undesired inductance. It is well known that, unlike capacitance, the magnitude of the negative inductance increases with frequency in the same way as for positive inductances. However, a negative inductance provides a negative 90° phase like a capacitor [36].

# 6.1 Active-C grounded positive and negative inductor simulators in compact form

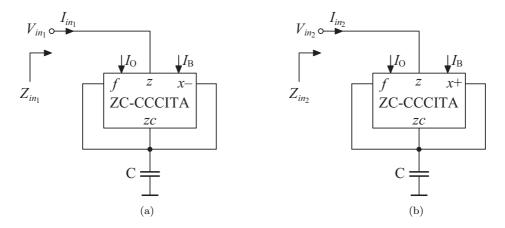

The proposed PIS and NIS in this Section (Fig. 6.1) use canonic number of passive and active elements (i.e. single grounded capacitor, single ZC-CCCITA). Using (3.3) and doing routine circuit analysis yields the following input impedances for both the circuits:

$$Z_{in_1} = -Z_{in_2} = sL_{eq} = \frac{sCR_f}{g_m} = \frac{sCV_T^2}{I_O I_B}.$$

(6.1)

From (6.1) it is obvious that circuits in Fig. 6.1 represent lossless positive and negative inductor simulators, respectively. In both circuits it can be also clearly seen that the inductance value  $L_{eq}$  can be adjusted electronically by either  $I_{\rm O}$  and/or  $I_{\rm B}$  currents.

Here, the non-ideal analysis will only focus on the grounded PIS circuit (i.e. Fig. 6.1(a)). It is sufficient since in case of the NIS it involves only sign change. Hence, taking into account the non-idealities of the ZC-CCCITA, except for the parasitics  $R_z$  and  $C_z$ , the input

Fig. 6.1: Proposed grounded (a) positive and (b) negative inductance simulators

impedance of the circuit from Fig. 6.1(a) is given as:

$$Z'_{in_{1}} = R_{lossy} + sL_{eq} =$$

$$= \frac{1 - \beta_{2}}{\beta_{1}g_{m}} + \frac{R_{f}}{\beta_{1}g_{m}(R_{zc}||R_{x})} + \frac{s(C + C_{zc} + C_{x})R_{f}}{\beta_{1}g_{m}} =$$

$$= \frac{2V_{T}(1 - \beta_{2})}{I_{B}\beta_{1}} + \frac{V_{T}^{2}}{I_{O}I_{B}\beta_{1}(R_{zc}||R_{x})} + \frac{V_{T}^{2}s(C + C_{zc} + C_{x})}{I_{O}I_{B}\beta_{1}}.$$

(6.2)

This equation clearly indicates that there is a lossy term (resistance) in the simulated impedance and thus the quality factor of the inductor is not infinite. To increase the quality factor of the simulated inductor, the lossy term needs to be minimized and this can be achieved by:

- (i) making the  $\beta_2$  very close to unity (by using high-output resistance current mirrors) and,

- (ii) choosing  $R_f \ll R_{zc}||R_x$ .

Assuming now the lossy term being minimized, the input impedance  $Z'_{in_1}$  approximates to the inductance of value  $L_{eq} = \frac{(C + C_{zc} + C_x)R_f}{\beta_1 g_m}$ . In practice, the external capacitor is chosen such that  $C \gg C_{zc} + C_x$ .

Till now, we have neglected the effects of parasitics  $R_z$  and  $C_z$ . Taking into account them we get the input admittance as:

$$Y_{in_1} = \frac{1}{R_z} + sC_z + \frac{1}{sL_{eq}}. (6.3)$$

Assuming the operating frequency  $\omega_0 \ll min\left(\frac{R_z}{L_{eq}}, \sqrt{\frac{1}{C_z L_{eq}}}\right)$ , the upper frequency potential of the circuit is limited, but the effects of the parasitics on the simulated inductance can be reduced.

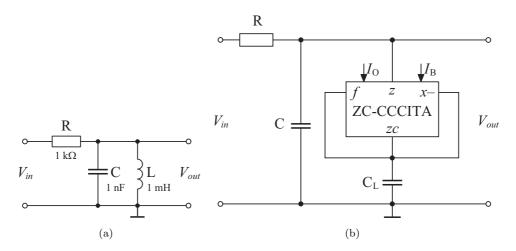

Fig. 6.2: (a) Second-order band-pass prototype and (b) its transformed equivalent circuit diagram

Ass application, the passive RLC band-pass filter (BPF) is shown in Fig. 6.2(a) [51] and the appropriate active circuit using the proposed grounded PIS is shown in Fig. 6.2(b). Routine circuit analysis yields the following voltage transfer function of the BPF:

$$K_{\rm BPF}(s) = \frac{V_{out}}{V_{in}} = \frac{s\frac{1}{CR}}{s^2 + s\frac{1}{CR} + \frac{1}{CL}} = \frac{s\frac{1}{CR}}{s^2 + s\frac{1}{CR} + \frac{I_{\rm O}I_{\rm B}}{CC_LV_{\rm T}^2}}.$$

(6.4)

The denominator of circuits in Fig. 6.2 is identically same, therefore, the natural angular frequency  $\omega_0$ , the quality factor Q, and the bandwidth BW ( $\omega_0/Q$ ) can be found as:

$$\omega_0 = \frac{1}{V_{\rm T}} \sqrt{\frac{I_{\rm O} I_{\rm B}}{C C_L}}, \quad Q = \frac{R}{V_{\rm T}} \sqrt{\frac{I_{\rm O} I_{\rm B} C}{C_L}}, \quad BW = \frac{1}{C R}.$$

(6.5)

The active and passive sensitivities of the filter parameters are following:

$$S_{I_{\rm O},I_{\rm B}}^{\omega_0} = -S_{C,C_L}^{\omega_0} = \frac{1}{2}, \ S_{V_{\rm T}}^{\omega_0} = -1, \ S_R^{\omega_0} = 0,$$

(6.6)

$$S_{I_{\rm O},I_{\rm B},C}^Q = -S_{C_L}^Q = \frac{1}{2}, \ S_R^Q = -S_{V_{\rm T}}^Q = 1,$$

(6.7)

$$S_{C,R}^{BW} = -1, \ S_{I_0,I_B,V_T,C_L}^{BW} = 0,$$

(6.8)

that are all not more than unity in magnitude.

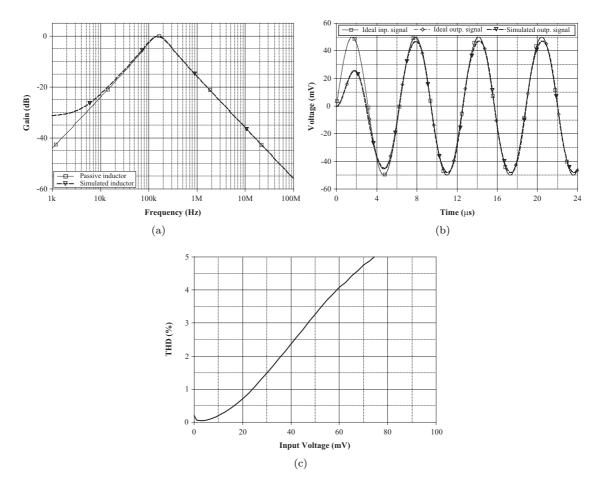

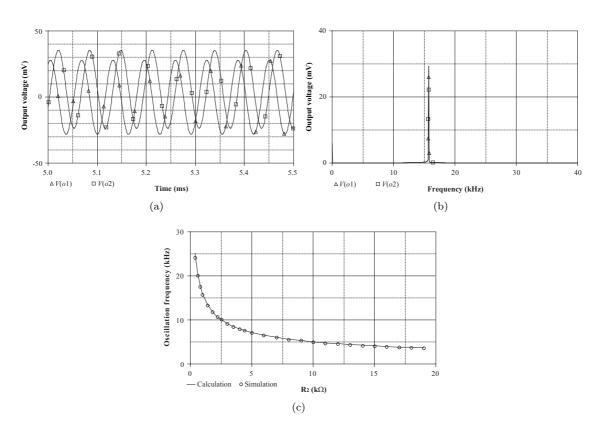

Using the proposed bipolar implementation of the ZC-CCCITA, the proposed grounded PIS in Fig. 6.1(a) and the second-order voltage-mode band-pass filter from Fig. 6.2(b) has been simulated for the characteristic frequency  $f_0 = \omega_0/2\pi \cong 159.15$  kHz and the quality

Fig. 6.3: Ideal and simulated gain responses of the (a) second-order VM BPF, (b) time-domain responses of the proposed second-order BPF at  $159.15~\mathrm{kHz}$ , (c) THD of the proposed second-order BPF at  $159.15~\mathrm{kHz}$

factor Q=1. The passive component values are shown in Fig. 6.2(a). The bipolar implementation of the ZC-CCCITA has been used and in the design the transistor model parameters NR100N (NPN) and PR100N (PNP) of bipolar arrays ALA400-CBIC-R from AT&T were used [28]. The inductor simulator is realized with the following active parameters and passive element values:  $g_m=1~\text{mA/V}$  ( $I_B=52~\mu\text{A}$ ),  $R_f=1~\text{k}\Omega$  ( $I_O=13~\mu\text{A}$ ), and  $C_L=1~\text{nF}$  to obtain the required L=1~mH. Ideal and simulated gain responses of the second-order CM multifunction filter and VM BPF are shown in Fig. 6.3(a) and Fig. 6.3(b), respectively. Additionly, transient simulation result of the filter is shown in Fig. 6.3(c) in which a sinusoidal input voltage signal with 50 mV peak value at 159.15 kHz is applied to the filter. In order to investigate distortion of the proposed BPF, the THD at 159.15 kHz has been simulated and the results are shown in Fig. 6.3(d).

The SPICE simulations confirm the feasibility of the proposed PIS and results are in good agreement with theory.

#### 7 QUADRATURE SINUSOIDAL OSCILLATORS

The quadrature oscillator (QO) is a circuit that provides two sinusoids with 90° phase difference. Such circuit is frequently used in various applications, i.e. in telecommunications for quadrature mixers and single-sideband generators, for measurement purposes in vector generators or selective voltmeters. Therefore, quadrature oscillators represent an important unit in many communication, control systems, signal processing, instrumentation and measurement systems [3], [30], [37], [57].

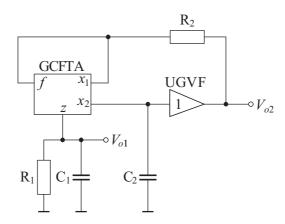

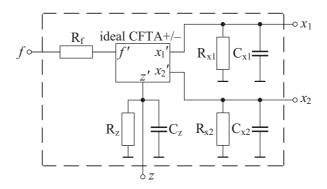

#### 7.1 VM SRCO design using generalized CFTA and UGVF

The generalized configuration realizing VM SRCOs using GCFTA and UGVF is shown in Fig. 7.1. Using (3.2) and doing routine circuit analysis, the CE for the circuit topology can be found as:

CE:

$$s^2C_1C_2R_1R_2 + sC_2R_2(1 - ab_1g_mR_1) - ab_2g_mR_1 = 0.$$

(7.1)

For the above equation to represent a valid CE for an oscillator, the following conditions should be simultaneously satisfied:

$$ab_1 = 1, \quad ab_2 = -1.$$

(7.2)

Only two structures confirm these, as described in Tab. 7.1. From (7.1) and (7.2), it is clear that for both the structures A and B, the CO, i.e. the term with s has to be 0 (zero), is:

$$CO: g_m R_1 \ge 1, \tag{7.3}$$

Fig. 7.1: The proposed generalized single-resistance-controlled quadrature oscillator using GCFTA and UGVF

and the FO is:

FO:

$$f_0 = \frac{1}{2\pi} \sqrt{\frac{g_m}{C_1 C_2 R_2}}$$

. (7.4)

It should be pointed out that although (7.3) defines the strict CO, however in practise  $g_m R_1$  is made slightly more than unity for the start-up of oscillations. It is evident from (7.3) and (7.4) that the CO can be controlled independently of FO by changing  $R_1$  and the FO can be controlled by means of resistor  $R_2$ . Therefore, the circuit truly describes a SRCO. The two quadrature voltage outputs of the general circuit topology as depicted in Fig. 7.1, are related as:

$$V_{o1} = jb_2kV_{o2}$$

, where  $k = \frac{\omega_0 C_2}{g_m}$ . (7.5)

Clearly, for k=1 the two quadrature voltages have equal amplitude. For a complete analysis, it is important to take into account the non-idealities of the GCFTA. Here, we provide the non-ideal analysis for variant A (i.e. the one using CFTA+/-). The model of the CFTA+/- including parasitic elements is shown in Fig. 7.2. The non-ideal analysis for variant B can be carried on similar lines.

- The non-zero parasitic input resistance at the terminal f is represented by  $R_f$ .

- $I_z = \alpha I_f$ , where  $\alpha$  represents the parasitic current gain, whose ideal value is unity. Similarly, the voltage transfer gain  $\gamma$  for the unity-gain voltage follower (buffer) differs slightly from its ideal

Tab. 7.1: Coefficients of GCFTA

| variant | a  | $b_1$ | $b_2$ |

|---------|----|-------|-------|

| A       | 1  | 1     | -1    |

| В       | -1 | -1    | 1     |

Fig. 7.2: Model of the CFTA+/- including parasitic elements

value of unity because of the voltage tracking error.

- The parasitic resistance  $R_z$  and parasitic capacitance  $C_z$  appears between the high-impedance z terminal and ground. The stray/parasitic capacitance  $C_z$  is absorbed into the external capacitance  $C_1$  as it appears in parallel with it. Also, since the value of  $R_z$  is in the order of  $M\Omega$ , hence for an external resistor of value  $R_1 \ll R_z$  connected at this terminal,  $R_z||R_1 \approx R_1$ . Thus, the non-ideal effects of parasitic impedance at terminal z are reduced, if not completely eliminated.

- The parasitic resistance  $R_{x_2}$  and parasitic capacitance  $C_{x_2}$  appears between the high-impedance  $x_2$  terminal and ground. The parasitic capacitance can be absorbed in the external capacitance  $C_2$ , but the presence of parasitic resistance at terminal  $x_2$  would change the type of the impedance, which should be of a purely capacitive character. A possible solution is to make the operating frequency  $\omega_o > \frac{1}{R_{x_2}C_2}$ .

- The parasitic resistance  $R_{x_1}$  and parasitic capacitance  $C_{x_1}$  appears between the high-impedance  $x_1$  terminal and ground. To alleviate the effects of parasitic impedance at terminal  $x_1$ , the CFTA should be designed to have a very low input parasitic resistance at terminal f. Ideally, the value of input parasitic resistance at terminal f is zero and terminal f is virtually grounded. Thus, the parasitic impedance at terminal  $x_1$  is connected between a virtual ground and a true ground.

Considering the first non-ideality and the parasitic capacitances at terminal z and  $x_2$ , the CO and FO of the proposed SRCO in Fig. 7.1 get modified and are given as:

CO:

$$\alpha g_m R_1 \ge 1$$

, (7.6)

and

FO:

$$f_0 = \frac{1}{2\pi} \sqrt{\frac{\alpha \gamma g_m}{(C_1 + C_z)(C_2 + C_{x_2})R_2}}$$

(7.7)

The sensitivity study indicates that:

$$|S_{\alpha,\gamma,g_m,R_2}^{f_0}| = \frac{1}{2},\tag{7.8}$$

$$S_{C_1}^{f_0} = -\frac{C_1}{2(C_1 + C_z)},\tag{7.9}$$

$$S_{C_z}^{f_0} = -\frac{C_z}{2(C_1 + C_z)},\tag{7.10}$$

$$S_{C_2}^{f_0} = -\frac{C_2}{2(C_2 + C_{x_2})}, (7.11)$$

$$S_{C_{x_2}}^{f_0} = -\frac{C_{x_1}}{2(C_2 + C_{x_2})}. (7.12)$$

It is evident from (7.8)–(7.12) that the magnitude values of all  $f_0$  sensitivities are less than unity and hence the proposed SRCO exhibits an attractive sensitivity performance. Also, both the CO and the FO in (7.6) and (7.7) are subject to process and temperature variations, to the presence of  $g_m$  term in the expressions. Similar tuning laws are also present in [40] and [33]. This should not be seen as a drawback for the FO, since the designer can control it using  $R_2$ . For the CO, a common practice is to make  $R_1 > \frac{1}{g_m}$ , so that even for any changes in the right-hand side value  $(g_m)$  the inequality is satisfied and there is an appropriate start-up of the oscillations. For more accurate tuning, the external resistors could be replaced by non-linearity canceled MOSFETs (working in triode region) [58]. This shall provide electronic tuning properties via gate voltages to both the CO and FO and a voltage-controlled oscillator (VCO) is created.

Fig. 7.3: (a) Quadrature voltage outputs  $V_{o1}$  and  $V_{o2}$  during steady stage, (b) simulated frequency spectrums of outputs  $V_{o1}$  and  $V_{o2}$ , (c) variation of oscillation frequency with  $R_2$

In order to confirm the above given theoretical analysis, the proposed CFTA-based SRCO (variant A) has been simulated with SPICE simulation program. The bipolar implementation of the CFTA+/- and the bipolar implementation of the UGVF, presented in [49] as output stage of CFOA, has been used with the DC supply voltages of  $+V_{CC} = -V_{EE} = 2$  V. In the design the transistor model parameters NR100N (NPN) and PR100N (PNP) of bipolar arrays ALA400-CBIC-R from AT&T were used [28] that are also listed in Tab. 9.1. The maximum value of terminal voltage of the UGVF without producing significant distortion is in the full scale of the supply voltage (in this case  $\pm 2$  V). The DC voltage gain of the UGVF  $\gamma \cong 0.9992$  with bandwidth  $f_{\gamma} \cong 3.971$  GHz.

The proposed circuit was designed using the following component values:  $C_1 = C_2 = 10$  nF,  $R_2 = 1$  k $\Omega$ , and  $g_m = 1$  mS ( $I_B = 52$   $\mu$ A). The value of  $R_1$  is kept slightly more than 1 k $\Omega$  to start the oscillations. The simulated output waveforms for  $V_{o1}$  and  $V_{o2}$  at steady stage are shown in Fig. 7.3(a). It is evident from Fig. 7.3(a) that the proposed circuit provides nearly equal sinusoidal waves and which is in accordance with (7.4). The offset (about 12 mV) of the  $V_{o2}$  is caused by the simple structure of the UGVF used [49] that does not enable suppress this parameter. Fig. 7.3(b) shows the frequency spectrum of the output waveforms and the value of THD at both the outputs are 1.67%. The variation of FO with resistor  $R_2$  without affecting the CO is shown in Fig. 7.3(c) and it is seen that the simulated values exhibit a close correspondence with the theoretical predictions.

#### 8 CONCLUSION

In the last decade, for analogue signal processing huge number of active building blocks were introduced, however, there is still the need to develop new active elements that offer new and better advantages. Therefore, the main contribution of this thesis was the definition of such novel ABBs, and their application possibilities.

Chapter 3 presents various active elements and introduces novel ones, such as the differential-input buffered and transconductance amplifier (DBTA), the current follower transconductance amplifier (CFTA), the z-copy current-controlled current inverting transconductance amplifier (ZC-CCCITA), the generalized current follower differential input transconductance amplifier (GCFDITA), the voltage gain-controlled modified current-feedback operational amplifier (VGC-MCFOA), and the minus-type current-controlled third-generation voltage conveyor (CC-VCIII—).

Using the proposed ABBs, in Chapter 4, novel structures of first-order all-pass filters are proposed. Chapter 5 presents novel structures of second-order universal filters, KHN-equivalent circuits, and inverse filters. Active grounded inductor simulators are discussed in Chapter 6, and in the Chapter 7 various quadrature sinusoidal oscillators are proposed. The proposed circuit work in the current-, voltage-, or mixed-mode and their comparison can be found in Appendix B.

To verify the behavior of the proposed circuits, all defined active elements are implemented using either bipolar or CMOS internal structure. The feasibility of selected circuits is also confirmed by experimental measurements.

Here, it is worth mention that part of this work has already been published in journals with impact factor (10 papers in the following journals: International Journal of Electronics, IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, IEICE Electronics Express, and AEU - International Journal of Electronics and Communications) and presented at international conferences (17 papers): PWC'07 (12th IFIP International Conference on Personal Wireless Communications, Prague, Czech Republic), TELFOR'08 (16th Telecommunications Forum, Belgrade, Serbia), ICONS'08 (Third International Conference on Systems, Cancun, Mexico), APPEL'08, APPEL'09, and APPEL'10 (Applied Electronics, Pilsen, Czech Republic), NCSP'09 (RISP International Workshop) on Nonlinear Circuits and Signal Processing, Honolulu, Hawaii, USA), ELECO'09 (6th International Conference on Electrical and Electronics Engineering, Bursa, Turkey), TSP'08 (International Conference on Telecommunications and Signal Processing, Paradfurdo, Hungary), TSP'09 (32th International Conference on Telecommunications and Signal Processing, Dunakiliti, Hungary), TSP'10 (33th International Conference on Telecommunications and Signal Processing, Baden near Vienna, Austria), and CSS'10 (4th International Conference on Circuits, Systems and Signals, Corfu Island, Greece).

Moreover, here it should be also noticed that my works have received 12 citations from international researchers (for more details, please refer my CV).

#### **BIBLIOGRAPHY**

- ABUELMA'ATTI, M. T., AL-ABSI, M. A. A current conveyor-based relaxation oscillator as a versatile electronic interface for capacitive and resistive sensors, *International Journal of Electronics*, 2005, vol. 92, no. 8, pp. 473–477.

- [2] ACAR, C., OZOGUZ, S. A new versatile building block: current differencing buffered amplifier suitable for analog signal processing filters, *Microelectronics Journal*, 1999, vol. 30, no. 2, pp. 157–160.

- [3] AHMED, M. T., KHAN, I. A., MINHAJ, N. On transconductance-C quadrature oscillators, *International Journal of Electronics*, 1997, vol. 83, no. 2, pp. 201–207.

- [4] AWAD, I. A., SOLIMAN, A. M. Inverting second generation current conveyors: the missing building blocks, CMOS realizations and applications, *International Journal of Electronics*, 1999, vol. 86, no. 4, pp. 413–432.

- [5] BECVAR, D., VRBA, K., ZEMAN, V., MUSIL, V. Novel universal active block: a universal current conveyor, In *Proceedings of the IEEE Int. Symposium on Circuits and Systems - ISCAS'00*, Geneva, Switzerland, 2000, pp. 471–474.

- [6] BERKI, A. T., ANDAY, F. Nth-order low-pass filter employing current differencing transconductance amplifiers, In Proceedings of the 17th European Conference on Circuit Theory and Design - ECCTD'05, Cork, Ireland, 2005, pp. 193–196.

- [7] BIOLEK, D. CDTA building block for current-mode analog signal processing, In *Proceedings of the 16th European Conference on Circuit Theory and Design ECCTD'03*, Krakow, Poland, 2003, pp. 397–400.

- [8] BIOLEK, D., BAJER, J., BIOLKOVA, V., KOLKA, Z., KUBICEK, M. Z copy-controlled gain-current differencing buffered amplifier and its applications, *International Journal of Circuit Theory and Applications*, accepted in 2010 and available online, DOI: 10.1002/cta.632.

- [9] BIOLEK, D., BIOLKOVA, V. Allpass filter employing one grounded capacitor and one active element, Electronics Letters, 2009, vol. 45, no. 16, pp. 807–808.

- [10] BIOLEK, D., BIOLKOVA, V. First-order voltage-mode all-pass filter employing one active element and one grounded capacitor, Analog Integrated Circuits and Signal Processing, 2009, in print, available online, DOI: 10.1007/s10470-009-9435-2.

- [11] BIOLEK, D., BIOLKOVA, V. Modified buffered transconductance amplifier for analog signal processing, In Proceedings of the Radioelektronika'09, Bratislava, Slovak Republic, 2009, pp. 191–194.

- [12] BIOLEK, D., SENANI, R., BIOLKOVA, V., KOLKA, Z. Active elements for analog signal processing: classification, review, and new proposals, *Radioengineering*, 2008, vol. 17, no. 4, pp. 15–32.

- [13] BHUSAN, M., NEWCOMB, R. W. Grounding of capacitors in integrated circuits, *Electronics Letters*, 1967, vol. 3, no. 4, pp. 148–149.

- [14] CAJKA J., DOSTAL T., VRBA, K. General view on current conveyors, International Journal of Circuit Theory and Applications, 2004, vol. 32, no. 3, pp. 133–138.

- [15] CAJKA, J., VRBA, K. The voltage conveyor may have in fact found its way into circuit theory, AEU -International Journal of Electronics and Communications, 2004, vol. 58, no. 4, pp. 244–248.

- [16] CAKIR, C., CAM, U., CICEKOGLU, O. Novel allpass filter configuration employing single OTRA, IEEE Transactions on Circuits and Systems-II, 2005, vol. 52, no. 3, pp. 122–125.

- [17] CARLOSENA, A., CABEZA, R., SERRANO, L. On the search for a universal active element, In *Proceedings of the IEEE Int. Symposium on Circuits and Systems ISCAS'94*, London, UK, 1994, pp. 779–782.

- [18] CICEKOGLU, O., TOKER, A. Current-mode oscillator with linear period control over a wide range, International Journal of Electronics, 1999, vol. 86, no. 12, pp. 1453–1462.

- [19] CHEN, P.-L., CHUNG, C.-C., LEE, C.-Y. A portable digitally controlled oscillator using novel varactors, IEEE Transactions on Circuits and Systems-II, 2005, vol. 52, no. 5, pp. 233–237.

- [20] DE MARCELLIS, A., FERRI, G., GUERRINI, N.C., SCOTTI, G., STORNELLI, V., TRIFILETTI, A. The VCG-CCII: a novel building block and its application to capacitance multiplication, *Analog Integrated Circuits and Signal Processing*, 2009, vol. 58, no. 1, pp. 55–59.

- [21] DOSTAL T., POSPISIL, J. Hybrid models of 3-port immittance convertors and current and voltage conveyors, *Electronics Letters*, 1982, vol. 18, no. 20, pp. 887–888.

- [22] EVANS, S. Current Feedback Op-amp Applications Circuit Guide, Fort Collins, CO: Complinear Corp., 1988, pp. 11.20–11.26.

- [23] FABRE, A., SAAID, O., WIEST, F., BOUCHERON, C. Low power current-mode second-order bandpass IF filter, IEEE Transactions on Circuits and Systems-II, 1997, vol. 44, no. 6, pp. 436-446.

- [24] FABRE, A., SAAID, O., WIEST, F., BOUCHERON, C. High frequency applications based on a new current controlled conveyor, *IEEE Transactions on Circuits Systems-I*, 1996, vol. 43, no. 2, pp. 82–91.

- [25] GIFT, S. J. G. The application of all-pass filters in the design of multiphase sinusoidal systems, Microelectronics Journal, 2000, vol. 31, no. 1, pp. 9–13.

- [26] FERRI, G., GUERRINI, N. C. Low-Voltage Low-Power CMOS Current Conveyors, London: Kluwer Acad. Publ., 2003.

- [27] FILANOVSKY, I. M., STROMSMOE, K. A. Current-voltage conveyor, *Electronics Letters*, 1981, vol. 17, no. 3, pp. 129–130.

- [28] FREY, D. R. Log-domain filtering: an approach to current-mode filtering, IEE Proceedings-G, 1993, vol. 140, no. 6, pp. 406–416.

- [29] GEIGER, R. L., SANCHEZ-SINENCIO, E. Active filter design using operational transconductance amplifiers: a tutorial, *IEEE Circuits and Devices Magazine*, 1985, vol. 1, no. 2, pp. 20–32.

- [30] HOLZEL, R. A simple wide-band sine wave quadrature oscillator, IEEE Transactions on Instrumentation and Measurement, 1993, vol. 42, no. 3, pp. 758–760.

- [31] HRIBSEK, M., NEWCOMB, R. W. VCO controlled by one variable resistor, IEEE Transactions on Circuits and Systems, 1976, vol. 23, no. 3, pp. 166–169.

- [32] JAIKLA, W., SIRIPRUCHYANUN, M. Current controlled CDBAs based-novel floating and grounded negative inductance simulators, In Proceedings of the International Technical Conference on Circuits/Systems, Computers, and Communications ITC-CSCC'06, Chiang Mai, Thailand, 2006, pp. 701-704.

- [33] JAIKLA, W., SIRIPRUCHYANUN, M., BAJER, J., BIOLEK, D. A simple current-mode quadrature oscillator using single CDTA, *Radioengineering*, 2008, vol. 17, no. 4, pp. 33–40.

- [34] KERWIN, W. J., HUELSMAN, L. P., NEWCOMB, R. W. State variable synthesis for insensitive integrated circuit transfer functions, *IEEE Journal of Solid-State Circuits*, 1967, vol. 2, no. 3, pp. 87–92.

- [35] KESKIN, A. U., AYDIN, C., HANCIOGLU, E., ACAR, C. Quadrature oscillators using current differencing buffered amplifiers (CDBAs), Frequenz, 2006, vol. 60, no. 3–4, pp. 57–59.

- [36] KILINC, S., SALAMA, K. N., CAM, U. Realization of fully controllable negative inductance with single operational transresistance amplifier, *Circuits, Systems, and Signal Processing*, 2006, vol. 25, no. 1, pp. 47– 57.

- [37] KHAN, I. A., KHWAJA, S. An integrable Gm-C quadrature oscillator, International Journal of Electronics, 2000, vol. 87, no. 11, pp. 1353–1357.

- [38] KOLKA, Z. SNAP program for symbolic analysis, Radioengineering, 1999, vol. 8, no. 1, pp. 23–24.

- [39] LABER, C. A., GRAY, P. R. A 20-MHz sixth-order BiCMOS parasitic-insensitive continuous-time filter and second-order equalizer optimized for disk-drive read channels, *IEEE Journal of Solid-State Circuits*, 1993, vol. 28, no. 4, pp. 462–470.

- [40] LAHIRI, A. Novel voltage/current-mode quadrature oscillator using current differencing transconductance amplifier, Analog Integrated Circuits and Signal Processing, 2009, vol. 61, pp. 199–203.

- [41] LEE, A., KO, H., CHO, D. D., HWANG, G. Non-ideal behavior of a driving resonator loop in a vibratory capacitive microgyroscope, *Microelectronics Journal*, 2008, vol. 39, no. 1, pp. 1–6.

- [42] LO, T. Y., KAO, C. S., HUNG, C. C. A Gm-C continuous-time analog filter for IEEE 802.11 a/b/g/n wireless LANs, Analog Integrated Circuits and Signal Processing, 2009, vol. 58, no. 3, pp. 197–204.

- [43] METIN, B., PAL, K., CICEKOGLU, O. All-pass filters using DDCC- and MOSFET-based electronic resistor, *International Journal of Circuit Theory and Applications*, accepted in 2010 and available online, DOI: 10.1002/cta.682.

- [44] METIN, B., PAL, K., CICEKOGLU, O. CMOS-controlled inverting CDBA with a new all-pass filter application, *International Journal of Circuit Theory and Applications*, accepted in 2010 and available online, DOI: 10.1002/cta.648.57.

- [45] MINAEI, S., CICEKOGLU, O. A resistorless realization of the first-order all-pass filter, *International Journal of Electronics*, 2006, vol. 93, no. 3, pp. 177–183.

- [46] MINAEI, S., SAYIN, O. K., KUNTMAN, H. A new CMOS electronically tunable current conveyor and its application to current-mode filters, *IEEE Transactions on Circuits and Systems-I*, 2006, vol. 53, no. 7, pp. 1448–14.

- [47] MINARCIK, M., VRBA, K. Low-output and high-input impedance frequency filters using universal voltage conveyor for high-speed data communication systems, In *Proceedings of the IARIA 5th International Con*ference on Networking - ICN'06, Mauritius, 2006, pp. 155–158.

- [48] NEWCOMB, R. W. The semistate description of nonlinear time-variable circuits, *IEEE Transactions on Circuits and Systems*, 1981, vol. 28, no. 1, pp. 62–71.

- [49] PALUMBO, G. Bipolar current feedback amplifier: compensation guidelines, Analog Integrated Circuits and Signal Processing, 1999, vol. 19, no. 2, pp. 107–114.

- [50] PONSONBY, J. E. B. Active all-pass filter using a differential operational amplifier, *Electronics Letters*, 1966, vol. 2, no. 4, pp. 134–135.

- [51] PRASAD, D., BHASKAR, D. R., SINGH, A. K. New grounded and floating simulated inductance circuits using current differencing transconductance amplifiers, *Radioengineering*, 2010, vol. 19, no. 1, pp. 194–197.

- [52] RUDELL, J. C., OU, J. J., CHO, T. B., CHIEN, G., BRIANTI, F., WELDON, J. A., GREY, P. A 1.9-GHz wide-band IF double conversion CMOS receiver for cordless telephone applications, *IEEE Journal of Solid-State Circuits*, 1997, vol. 32, no. 12, pp. 2071–2088.

- [53] SALAMA, K., SOLIMAN, A. Novel MOS-C quadrature oscillator using the differential current voltage conveyor, In Proceedings of the 42nd Midwest Symposium on Circuits and Systems - MWSCAS'99, Las Cruces, USA, 1999, pp. 279–282.

- [54] SAMITIER, J., PUIG-VIDAI, M., BOTA, S. A., RUBIO, C., SISKOS, S. K., LAOPOULOS, T. A current-mode interface circuit for a piezoresistive pressure sensor, *IEEE Transactions on Instrumentation and Measurement*, 1998, vol. 47, no. 3, pp. 708–710.

- [55] SEDRA, A. S. A class of stable active filters using unity-gain voltage followers, IEEE Journal of Solid-State Circuits, 1972, vol. 7, no. 4, pp. 311–315.

- [56] SEDRA, A., SMITH, K. C. A second-generation current conveyor and its applications, IEEE Transactions on Circuit Theory, 1970, vol. 17, no. 1, pp. 132–134.

- [57] SEDRA, A. S., SMITH, K. C. Microelectronic circuits, Holt, 3rd ed., Rinehart and Winston, Inc., Florida, 1991.

- [58] SENANI, R. Realization of linear voltage-controlled-resistance in floating form, *Electronics Letters*, 1994, vol. 30, no. 23, pp. 1909–1911.

- [59] SMITH, K. C., SEDRA, A. S. Realization of the Chua family of new nonlinear network elements using the current conveyor, *IEEE Transactions on Circuit Theory*, 1970, vol. 17, no. 1, pp. 137–139.

- [60] SPONAR, R., VRBA, K. Measurements and behavioral modelling of modern conveyors, IJCSNS International Journal of Computer Science and Network Security, 2006, vol. 6, no. 3A, pp. 57–65.

- [61] SVOBODA, J. A., MCGORY, L., WEBB, S. Applications of a commercially available current conveyor, International Journal of Electronics, 1991, vol. 70, no. 1, pp. 159–164.

- [62] TANGSRIRAT, W. Current differencing transconductance amplifier-based current-mode four-phase quadrature oscillator, *Indian Journal of Engineering and Materials Sciences*, 2007, vol. 14, no. 4, pp. 289– 294.

- [63] TOKER, A., OZOGUZ, S., CICEKOGLU, O., ACAR, C. Current-mode all-pass filters using current differencing buffered amplifier and a new high-Q bandpass filter configuration, *IEEE Transactions on Circuits and Systems-II*, 2000, vol. 47, no. 9, pp. 949–954.

- [64] TOUMAZOU, C., LIDGEY, F. J., HAIGH, D. G. Analogue IC design: the current-mode approach, London: Peter Peregrinus Ltd., 1990, 646 pages.

- [65] TSUKUTANI, T., EDASAKI, S., SUMI, Y., FUKUI, Y. Current-mode universal biquad filter using OTAs and DO-CCII, Frequenz, 2006, vol. 60, no. 11–12, pp. 237–240.

- [66] UYGUR, A., KUNTMAN, H. Seventh-order elliptic video filter with 0.1 dB pass band ripple employing CMOS CDTAs, AEU - International Journal of Electronics and Communications, 2007, vol. 61, no. 5, pp. 320–328.

- [67] UYGUR, A., KUNTMAN, H., ZEKI, A. Multi-input multi-output CDTA-based KHN filter, In Proceedings of the 4th International Conference on Electrical and Electronics Engineering - ELECO'05, Bursa, Turkey, 2005, pp. 46–50.

- [68] VAINIO, O., OVASKA, S. J. A class of predictive analog filters for sensor signal processing and control instrumentation, IEEE Transactions on Industrial Electronics, 1997, vol. 44, no. 4, pp. 565–578.

- [69] YUCE, E. On the implementation of the floating simulators employing a single active device, AEU -International Journal of Electronics and Communications, 2007, vol. 61, no. 6, pp. 453–458.

- [70] YUCE, E., MINAEI, S. A modified CFOA and its applications to simulated inductors, capacitance multipliers, and analog filters, *IEEE Transactions on Circuits and Systems-I*, 2008, vol. 55, no. 1, pp. 266–275.

- [71] YUCE, E., PAL, K., MINAEI, S. A high input impedance voltage-mode all-pass/notch filter using a single variable gain current conveyor, *Journal of Circuits, Systems, and Computers*, 2008, vol. 17, no. 5, pp. 827–834.

- [72] ZEKI, A., TOKER, A. The dual-X current conveyor (DXCCII): a new active device for tunable continuoustime filters, *International Journal of Electronics*, 2002, vol. 89, no. 12, pp. 913–923.

- [73] ZEKI, A., TOKER, A., OZOGUZ, S. Linearly tunable transconductor using modified CDBA, Analog Integrated Circuits and Signal Processing, 2001, vol. 26, no. 2, pp. 179–183.

#### Selected publications of the Author

- [74] HERENCSAR, N., KOTON, J., LATTENBERG, I., VRBA, K. Signal-flow graphs for current-mode universal filter design using current follower transconductance amplifiers (CFTAs), In *Proceedings of the Applied Electronics APPEL'08*, Pilsen, Czech Republic, 2008, pp. 113–116.

- [75] HERENCSAR, N., KOTON, J., VRBA, K. A new electronically tunable voltage-mode active-C phase shifter using UVC and OTA, *IEICE Electronics Express*, 2009, vol. 6, no. 17, pp. 1212–1218. (Impact Factor 2009 = 0.510)

- [76] HERENCSAR, N., KOTON, J., VRBA, K. Differential-input buffered and transconductance amplifier (DBTA): a novel building block for analog signal processing, In Proceedings of the 2009 RISP International Workshop on Nonlinear Circuits and Signal Processing - NCSP'09, Honolulu, Hawaii, USA, 2009, pp. 542– 545.

- [77] HERENCSAR, N., KOTON, J., VRBA, K. Differential-input buffered and transconductance amplifier (DBTA)-based new trans-admittance- and voltage-mode first-order all-pass filters, In *Proceedings of the* 6th International Conference on Electrical and Electronics Engineering - ELECO'09, Bursa, Turkey, 2009, pp. 256–259.

- [78] HERENCSAR, N., KOTON, J., VRBA, K. Novel resistorless allpass filter using current-controlled thirdgeneration voltage conveyor (CC-VCIII), Analog Integrated Circuits and Signal Processing, to be submitted in 2010. (Impact Factor 2009 = 0.408)

- [79] HERENCSAR, N., KOTON, J., VRBA, K., LAHIRI, A. New voltage-mode quadrature oscillator employing single DBTA and only grounded passive elements, *IEICE Electronics Express*, 2009, vol. 6, no. 24, pp. 1708–1714. (Impact Factor 2009 = 0.510)

- [80] HERENCSAR, N., KOTON, J., VRBA, K., LATTENBERG, I. New voltage-mode universal filter and sinusoidal oscillator using only single DBTA, *International Journal of Electronics*, 2010, vol. 97, no. 4, pp. 365–379. (Impact Factor 2009 = 0.430)

- [81] HERENCSAR, N., KOTON, J., VRBA, K., LATTENBERG, I. Novel SIMO type current-mode universal filter using CFTAs and CMIs, in *Proceedings of the 31th International Conference on Telecommunications* and Signal Processing - TSP'08, Paradfurdo, Hungary, 2008, pp. 107–110.

- [82] HERENCSAR, N., KOTON, J., VRBA, K., LATTENBERG, I., MISUREC, J. Generalized design method for voltage-controlled current-mode multifunction filters, In *Proceedings of the 16th Telecommunications* Forum - TELFOR'08, Belgrade, Serbia, 2008, pp. 400–403.

- [83] HERENCSAR, N., KOTON, J., VRBA, K., MISUREC, J. A novel current-mode SIMO type universal filter using CFTAs, *Contemporary Engineering Sciences*, 2009, vol. 2, no. 2, pp. 59–66.

- [84] HERENCSAR, N., LAHIRI, A., KOTON, J., VRBA, K. Realization of resistorless positive and negative grounded inductor simulators using single ZC-CCCITA, *Radioengineering*, submitted in 2010, paper no. 10– 107. (Impact Factor 2009 = 0.312)

- [85] HERENCSAR, N., VRBA, K. Current conveyors-based circuits using novel transformation method, *IEICE Electronics Express*, 2007, vol. 4, no. 21, pp. 650–656. (Impact Factor 2009 = 0.510)

- [86] HERENCSAR, N., VRBA, K., KOTON, J., LAHIRI, A. Realisations of single-resistance-controlled quadrature oscillators using generalised current follower transconductance amplifier and unity-gain voltage-follower, *International Journal of Electronics*, 2010, vol. 97, no. 8, pp. 897–906. (Impact Factor 2009 = 0.430)

- [87] HERENCSAR, N., VRBA, K., KOTON, J., LATTENBERG, I. The conception of differential-input buffered and transconductance amplifier (DBTA) and its application, *IEICE Electronics Express*, 2009, vol. 6, no. 6, pp. 329–334. (Impact Factor 2009 = 0.510)

- [88] KOTON, J., HERENCSAR, N., VRBA, K. KHN-equivalent voltage-mode filters using universal voltage conveyors, AEU International Journal of Electronics and Communications, accepted in 2010 and available online, DOI: 10.1016/j.aeue.2010.02.005. (Impact Factor 2009 = 0.508)

- [89] KOTON, J., HERENCSAR, N., VRBA, K. Minimal configuration precision full-wave rectifier using current and voltage conveyors, *IEICE Electronics Express*, 2010, vol. 7, no. 12, pp. 844–849. (Impact Factor 2009 = 0.510)

- [90] KOTON, J., HERENCSAR, N., VRBA, K. Single-input three-output variable Q and  $\omega_0$  filter using universal voltage conveyors, *International Journal of Electronics*, 2010, vol. 97, no. 5, pp. 531–538. (Impact Factor 2009 = 0.430)

- [91] KOTON, J., VRBA, K., HERENCSAR, N. Tuneable filter using voltage conveyors and current active elements, International Journal of Electronics, 2009, vol. 96, no. 8, pp. 787–794. (Impact Factor 2009 = 0.430)

#### Curriculum Vitae

#### Norbert Herencsár

Personal Address: Sidlisko Buducnost c. 1298, SVK-925 82 Tesedikovo, Slovak Republic

Information Born: May, 29, 1982, Sala, Slovak Republic

$\begin{array}{lll} Phone: & +420\ 776\ 674\ 845 \\ Fax: & +420\ 541\ 149\ 192 \\ E-mail: & \text{herencsn@feec.vutbr.cz} \end{array}$

Web: www.utko.feec.vutbr.cz/herencsar/ Language Skills: Slovak, Hungarian, Czech, English

#### **EDUCATION**

#### 2006–2010: Brno University of Technology, Brno, Czech Republic

Faculty of Electrical Engineering and Communication

• Doctoral studies of the specialization *Teleinformatics*

#### 2009 Sept.-2010 Feb.: Bogazici University, Istanbul, Turkey

Department of Electrical and Electronic Engineering

• Erasmus LLP Exchange Student

#### 2000–2006: Brno University of Technology, Brno, Czech Republic

Faculty of Electrical Engineering and Communication

• Master studies of the specialization *Electronics and Communication*

## PARTICIPATION IN PROJECTS

#### During doctoral studies Mr. Herencsár participated in solving following projects:

#### Projects supported by the Czech Science Foundation