# Decomposed Implicit Models of Piecewise - Linear Networks

Jaromír BRZOBOHATÝ

Department of Microèlectronics

and

Jiří POSPÍŠIL

Department of Radioelectronics

Technical University of Brno

Antonínská 1, 662 09 Brno

ČSFR

## **Abstract**

The general matrix form of the implicit description of a piecewise-linear (PWL) network and the symbolic block diagram of the corresponding circuit model are proposed. Their decomposed forms enable us to determine quite separately the existence of the individual breakpoints of the resultant PWL characteristic and their coordinates using independent network parameters. For the two-diode and three-diode cases all the attainable types of the PWL characteristic are introduced.

#### Introduction

In recent papers [1],[2],[3] several methods of piecewise-linear (PWL) network synthesis have been introduced as well as a new approach based on a implicit description of the whole system [4],[5],[6]. The corresponding circuit model usually contains an active linear transformation block loaded by ideal diodes as basic PWL elements. However, none of these methods provides the possibility of determining and realizing all attainable types and shapes of the resultant PWL characteristic including all special cases; in other words no systematic synthesis of the PWL networks has been published yet. The present contribution suggests how to achieve that by using the generalization and modification of the procedure introduced in [4],[5],[6].

### Global implicit model

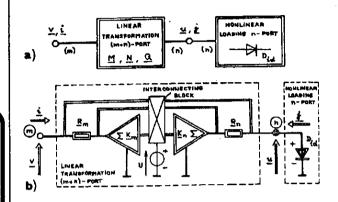

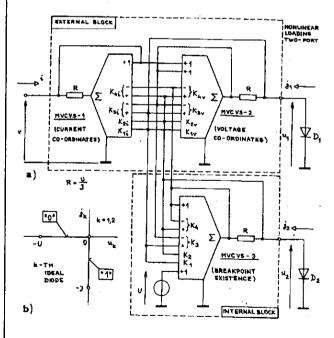

Consider a structure consisting of a linear active transformation (m+n)-port and a nonlinear loading n-port (Fig.1a). The transformation block can be realized by (m+n) multiple voltage controlled voltage sources (MVCVSs), (m+n) linear resistors, and one independent voltage source U (Fig.1b). Loading block is represented by n separate ideal diodes whose A-V characteristics are of simple rectangular shape (Fig.4b). The double-line symbols

in Fig.1 represent sets of network elements [6]. Similarly,

Fig.1. General form of the symbolic representation of PWL network, a) Block diagram, b)Circuit model containing MVCVSs and ideal diodes

the double lines and the full lines symbolize sets of zerocurrent and nonzero-current connections, respectively. Denoting the vectors of the external variables as

$$\mathbf{v} = [v_1, ..., v_m]^T, \mathbf{i} = [i_1, ..., i_m]^T$$

(1)

and those of the internal variables as

$$\mathbf{u} = [u_1, ..., u_n]^{\mathrm{T}}, \mathbf{j} = [j_1, ..., j_n]^{\mathrm{T}}$$

(2)

the nonlinear loading block can be then described by

$$\mathbf{u}, \mathbf{j} < 0, \ \mathbf{j}^{\mathrm{T}} \cdot \mathbf{u} = 0 \tag{3}$$

and the linear transformation block generally by

$$M[v, u]^{T} + N[i, j]^{T} + O = 0$$

(4)

As the configuration of the nonlinear block (set of ideal diodes) is chosen, the synthesis of the required PWL characteristic is then reduced to that of the linear transforma-

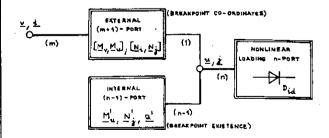

Fig.2a. Decomposed form of the symbolic representation of PWL network, block diagram

Fig.2b. Decomposed form of the symbolic representation of PWL network, circuit model containing MVCVSs and ideal diodes

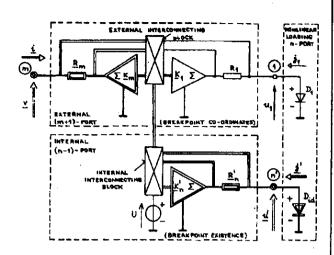

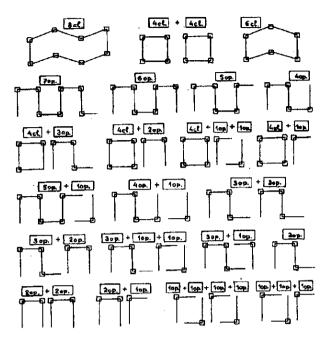

Fig.3. Symbolic representation of all the possible diode-state combinations. a) to b) One diode to four diodes case

tion block. After finding the matrices M, N, Q (Fig.1a) the corresponding MVCVS gain matrices  $K_m$ ,  $K_n$  (Fig.1b) can easily be derived [6]. Each MVCVS can be realized by one op. amp. and linear resistors [7].

#### Decomposed implicit model

The global implicit description (4) can be rewritten into the submatrix form

$$\begin{bmatrix} \mathbf{M}_{\mathbf{v}} \, \mathbf{M}_{\mathbf{u}} \\ \mathbf{0} \, \mathbf{M}_{\mathbf{u}}' \end{bmatrix} \begin{bmatrix} \mathbf{v} \\ \mathbf{u} \end{bmatrix} + \begin{bmatrix} \mathbf{N}_{\mathbf{i}} \, \mathbf{N}_{\mathbf{j}} \\ \mathbf{0} \, \mathbf{N}_{\mathbf{j}}' \end{bmatrix} \begin{bmatrix} \mathbf{i} \\ \mathbf{j} \end{bmatrix} + \begin{bmatrix} \mathbf{0} \\ \mathbf{Q}' \end{bmatrix} = \mathbf{0}$$

(5)

which corresponds to the decomposed form of the symbolic representation of any PWL network, While formula (4) represents (m + n) equations describing the whole transformation (m + n)-port, the individual rows in formula (5) describe separately the external (m + 1)-port and the internal (n-1)-port (Fig.2). Such a block configuration enables us to decide quite separately the existence of the individual breakpoints of the resultant PWL characteristic and to adjust their co-ordinates by using the independent network parameters. Any of the n loading ideal diodes can be either in "off" state (symbol "0") or in "on" state (symbol "1") - see Fig.4b, and therefore the total number of all possible diode-state combinations is generally 2<sup>n</sup> (the synthesis procedure developed in [4],[5],[6] utilizes only (n + 1) of these combinations.). Each breakpoint of the resultant PWL characteristic corresponds to such a transient state between two adjoining combinations when only one diode changes its state  $(u_k = 0, j_k = 0)$  while the remaining (n-1) diodes are either in "off" or in "on" state so that just (n-1) internal variables have nonzero values. As the internal block is described by (n-1) equations expressing the relations among the internal variables only, i.e.

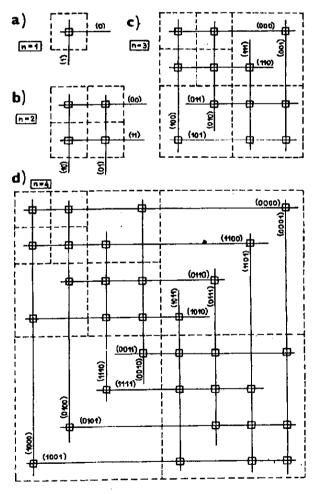

Fig.4. Two diodes PWL network. a) Complete circuit model. b) Rectangular A-V characteristics of ideal diodes

$$\mathbf{M}_{\mathbf{u}} \mathbf{u} + \mathbf{N}_{\mathbf{j}} \mathbf{j} + \mathbf{Q} = \mathbf{0} \tag{6}$$

it evidently determines the existence of the individual breakpoints of the resultant PWL characteristic. Then the initial step of the systematic synthesis of PWL network consists in derivation of submatrices  $M_u$ ,  $N_i$  and Q corre-

Fig.5. Complete survey of all attainable types of PWL characteristics for three diodes case

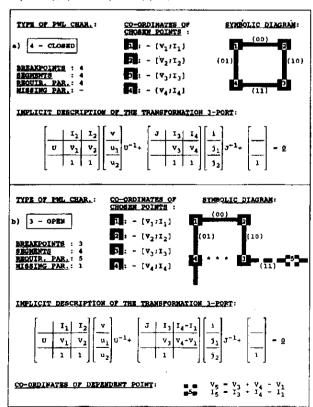

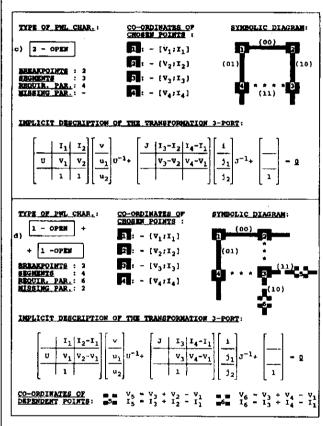

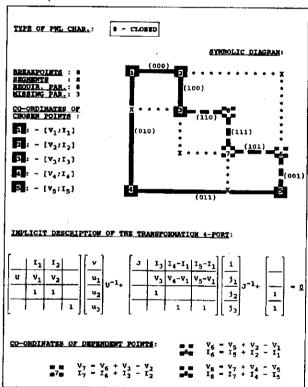

Tab.1 Complete solution for a two diodes network. a) 4 breakpoints (closed), b) 3 breakpoints (open).

sponding to the required type of PWL characteristic. Although this problem has not been solved completely and generally yet, some principles of this procedure have been developed. The results for the two-diode and the three-diode case are available.

After finding submatrices  $M_u$ ,  $N_j$  and Q we can substitute the values of the internal variables u, j for the individual breakpoints into the (m + 1) equations describing the external block, i.e.

$$[\mathbf{M}_{v_i} \ \mathbf{M}_{u}] [\mathbf{v}, \mathbf{u}]^T + [\mathbf{N}_{i_i} \ \mathbf{N}_{i_i}] [\mathbf{i}, \mathbf{j}]^T = \mathbf{0}$$

(7)

Tab. 1 Complete solution for a two diodes network. c) 2 breakpoints (open), d) 2 times 1 breakpoints (open)

The values of the external variables v, i correspond to the coordinates of these breakpoints and then we can derive or choose the parameters of the submatrices in formula (7). It is worth nothing that the number of free parameters is only (n + 2).

#### Attainable types of PWL characteristics

The procedure suggested above enables us not only to utilize all the possible diode-state combinations but also (for a given number of n ideal diodes) to derive all the attainable types of the resultant PWL characteristics. The symbolic representation introduced in Fig.3 (n = 1 to 4) is very useful for this purpose because every next diagram can easily be derived from the previous one by the systematic hierarchical procedure. It is evident that maximum two breakpoints of the possible n can exist on each segment.

The complete universal circuit model for the simplest case (m = 1, n = 2) is introduced in Fig.4a which gives a possibility to realize all four attainable types of the resultant

A-V characteristic. It includes the closed (cl.), open (op.), and decomposed cases in accordance with Tab.1. Further details, including the corresponding values of the individual MVCVS gains, can be found in ref. [8]. For the multi-diode case the number of attainable types rapidly increases (for n=3 it is 21 - see Fig.5). For a better survey the shapes of PWL characteristics introduced in Fig.5 are shown only symbolically. An example of the PWL characteristic for the case of three diodes (8 breakpoints, closed shape) is shown in its complete form in Tab.2.

#### Conclusions

Decomposed implicit model provides the following new possibilities in the synthesis of PWL networks:

Tab.2. Complete solution for a three diodes network (8 breakpoints closed)

- to utilize all the possible diode-state combinations

- to derive all attainable types of PWL characteristics

- to choose separately the existence of any breakpoint

- to adjust independently the co-ordinates of the chosen breakpoints.

The closed characteristic can be used, for example, in a simple nonharmonic generator synthesis while the decomposed characteristic in multi-stable network synthesis or modelling of bifurcations. In monothematic paper [9] some other details and complete solutions for all the attainable PWL characteristics (n = 2, n = 3) will be presented, i.e. the complete forms of the M, N, Q matrices, the values of the MVCVS gains in the corresponding circuit models, etc.

#### References

- [1] HUERTAS,J.L., and RUEDA,A.: Synthesis of Resistive n-Port Sectionwise Piece Wise Linear Networks. IEEE Trans., 1982, CAS-29, pp. 6-14.

- [2] VAN BOKHOVEN,W.M.G.: On The Synthesis of Piecewise Linear n-Port Networks. Proc. ISCAS 84, Montreal, 1984, pp. 1369-1371.

- [3] LINARES-BARANCO,B., RAMIREZ-ANGULO,J., SANCHEZ-SINENCIO,E., and RODRIGUEZ-VASQUEZ,A.: Programmable Piece-Wise Linear Function Synthesizers Using Operational Transconductance Amplifiers. Proc. ECCTD'89, Brighton, 1989, pp. 452-456.

- [4] BRZOBOHATÝ, J., and POSPÍŠIL, J.: Universal Piecewise Linear Model of Nonlinear Resistive Network. Modelling, Simulation & Control, A-19, No. 2, 1988, pp. 57-63.

- [5] BRZOBOHATÝ, J., and POSPÍŠIL, J.: Generalized Synthesis of Piecewise Linear Resistive Two-Port. Proc. ECCTD'87, Paris, 1987, pp. 747-752.

- [6] BRZOBOHATÝ, J., and POSPÍŠIL, J.: Multidimensional Piecewise Linear Network Synthesis. Proc. ECCTD'89, Brighton, 1989, pp. 552-556.

- [7] CICHOCKI,A., and OSOWSKI,S.: Realisation of Resistive n-Port Using Operational Amplifiers. Electron. Letters, 1978, 14, pp. 412-413.

- [8] BRZOBOHATÝ, J., and POSPÍŠIL, J.: Universal Network Realising Basic Piecewise-Linear I/V Characteristics. Electron. Letters, 1991, 27, No. 5, pp. 402-404.

- [9] BRZOBOHATÝ,J., and POSPÍŠIL,J.: Piecewise-Linear Network Synthesis Using Decomposed Implicit Model (will be publ.).

#### About authors. ...

Jaromír Brzobohatý was born in Brno, Czechoslovakia, in 1935. M.S. and Ph.D. (equivalent degrees): 1960 and 1980, respectively, both in el. eng., Technical University of Brno, Czechoslovakia.1960-1963: researcher in Metra Blansko; 1963: Assoc. Prof.; 1987:Prof.; 1985-1989: Dean of Faculty of Electrical Engineering; since 1980: Head of Dept. of Microelectronics. Research and pedagogical interest: Theory of Circuits, Microelectronics(current-mode networks, piecewise-linear networks). IEEE: M.-1988, S.M.-1990.

Jiří Pospíšil was born in Brno, Czechoslovakia, in 1939. M.S. and Ph.D. (equivalent degrees): 1963 and 1973, respectively; Dr.Sc.(Doctor of Technical Sciences): 1988, all in el. eng., Technical University of Brno, Czechoslovakia. 1964: Assist. Prof., Military Academy of Brno, Dept. of El. Eng.; 1970-1972: Visit. Prof., Military Technical College, Cairo, Egypt; since 1974: Technical University of Brno, Dept. of Radioelectronics; 1980: Assoc.Prof.; 1989: Prof. Research and pedagogical interest: Theory of Circuits, Network Theory; (active RC networks, piecewise-linear networks).