# MOS-Only Voltage-Mode All-Pass Filter Core Suitable for IC Design

METIN, B.; HERENCSÁR, N.; KLEDROWETZ, V.; CICEKOGLU, O.

AEU - International Journal of Electronics and Communications 2019, vol. 110, October 2019, pp. 1-7

ISSN: 1434-8411

DOI: https://doi.org/10.1016/j.aeue.2019.152834

Accepted manuscript

# MOS-Only Voltage-Mode All-Pass Filter Core Suitable for IC Design

Bilgin Metin<sup>a,\*</sup>, Norbert Herencsar<sup>b</sup>, Vilem Kledrowetz<sup>c</sup> and Oguzhan Cicekoglu<sup>d</sup>

#### ARTICLE INFO

Keywords: all-pass filter analog filter MOS-only filter post-layout simulations resistorless filter TSMC 180 nm CMOS voltage-mode

# ABSTRACT

In this paper, an area efficient CMOS first-order voltage-mode (VM) all-pass filter (APF) is proposed. The introduced resistorless MOS-only core circuit consists of three transistors only. For the design three transconductances and one gate-to-source capacitance of MOS transistors are sufficient instead of external passive resistors and capacitors, while the full implementation of the VM APF consists of 12 MOS transistors and one grounded capacitor only. Hence, the proposed circuit exhibits important features such as simplicity, permitting reduced chip area when integrated and wide operating frequency range compared to classical analog counterparts that require active elements employing large number of transistors. The theoretical results are in detail verified by numerous post-layout simulations using Cadence IC6 Spectre analog design environment. In the design, medium  $V_{\rm th}$  transistors with 1.8 V supply voltage were used and modeled by the TSMC 180 nm CMOS process parameters available in EU-ROPRACTICE IC Service design kit. The post-layout simulated pole frequency of the VM APF is 4.825 MHz, the implemented layout including metal-insulator-metal on-chip capacitor occupies an area of 31.1  $\mu$ m $\times$ 39.5  $\mu$ m, while the total power consumption of the filter is found to be only 92.57  $\mu$ W.

# 1. Introduction

Recently, there is growing demand for analog filter structures circuits [1]–[30] operated with low-voltage and with capabilities of higher frequency of operation [31]. Most conventional analogue building blocks (ABBs) based on Op-Amps, Current Conveyors, etc. may remain inadequate for applications beyond tens of megahertz frequency range or may require advanced ABB with larger number of transistors. For higher frequencies,  $g_{\rm m}$ -RL [20], or  $g_{\rm m}$ -C [21] type filters can be preferred. In the most of the publications in the literature active component count is a comparison parameter in analog filter designs. This is understandable since it directly gives an idea about power consumption and chip area. However, in many recent papers about circuits with reduced chip area and power consumption, MOSFET-only analog design approach attracts growing attention [19], [22]–[30].

In MOSFET-only design approach only metal-oxidesemiconductor (MOS) transistors operating in the saturation region are used instead of generic active elements. Moreover, instead of passive resistors, the transconductance  $(g_m)$  parameter of MOS is used to obtain resistive (or conductive) dimension for analog circuit de-

\*Corresponding author

bilgin.metin@boun.edu.tr (B. Metin);

herencsn@feec.vutbr.cz (N. Herencsar);

kledrowetz@feec.vutbr.cz (V. Kledrowetz);

cicekogl@boun.edu.tr (O. Cicekoglu)

ORCID(s): 0000-0002-5828-9770 (B. Metin);

0000-0002-9504-2275 (N. Herencsar); 0000-0002-6720-1224

(V. Kledrowetz); 0000-0002-2038-4203 (O. Cicekoglu)

sign. In other words, the small-signal model of the MOS transistor with its transconductance and gate-to-source capacitance  $(C_{\rm gs})$  is very suitable for designing high performance active circuits. Such applications are therefore expected to exhibit important features such as reduced number of transistors, simplicity, reduced chip area, and wide operating frequency range compared to classical analog circuits that employ standard ABBs.

In this study, an easily integrable area efficient CMOS first-order voltage-mode (VM) all-pass filter (APF) is proposed. All-pass filters are widely used as phase equalizers where they shift the phase of an input signal without altering its amplitude. Table 1 provides a fair performance comparison of proposed VM APF to state-of-the-art VM APFs [1]-[21] based on relevant criterion. The basic core topology of the proposed filter employs only 3 MOS transistors operating in saturation mode. In addition, the on-chip implemented VM APF containing an additional biasing circuitry and inverting output voltage level shifter employs in total 12 transistors and a single grounded capacitor. Therefore, it was very favorable in Cadence IC6 Spectre analog design environment from the integrated circuit implementation point of view.

# 2. Circuit Description

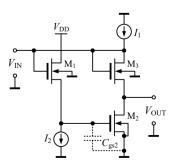

The proposed first-order VM APF core circuit is shown in Fig. 1. Assuming that size of the transistor  $M_2$  is large enough such that its gate-to-source capacitance is at least an order of magnitude greater than the  $C_{\rm gs}$  of  $M_1$  and  $M_3$  with the matching condition of

<sup>&</sup>lt;sup>a</sup>Department of Management Information Systems, Bogazici University, Bebek, Istanbul, 34342, Turkey

<sup>&</sup>lt;sup>b</sup>Department of Telecommunications, Brno University of Technology, Technicka 3082/12, 616 00 Brno, Czech Republic

<sup>&</sup>lt;sup>c</sup>Department of Microelectronics, Brno University of Technology, Technicka 3058/10, 616 00 Brno, Czech Republic

<sup>&</sup>lt;sup>d</sup>Department of Electrical and Electronics Engineering, Bogazici University, Bebek, Istanbul, 34342, Turkey

Table 1 Comparison of previously published state-of-the-art first-order all-pass filters.

| Ref.                                     | Operation<br>mode | No. and<br>ABB type <sup>b</sup> | No. of<br>transistors | No. of $R/C/L$ (gr. or float.) | No passive/<br>active<br>matching<br>constraints | Technology                                  | Power supplies (V) | $f_{	extsf{p\_sim}}$ (Hz) | Power<br>consumption<br>(W) | Area of designed<br>layout/<br>fabricated<br>APF on-chip |

|------------------------------------------|-------------------|----------------------------------|-----------------------|--------------------------------|--------------------------------------------------|---------------------------------------------|--------------------|---------------------------|-----------------------------|----------------------------------------------------------|

| [1]                                      | Voltage-mode      | 1 CCII-                          | _                     | 1 float.; 2 gr./1 float./0     | no                                               | _                                           | _                  | -                         | _                           | NA                                                       |

| [2] <sup>a</sup>                         | Voltage-mode      | 1 CCII-                          | NA                    | 2 gr./1 float./0               | no                                               | $D^d$                                       | -                  | 1 k                       | -                           | NA                                                       |

| [3] <sup>a</sup>                         | Voltage-mode      | 1 FTFN                           | 17                    | 2 gr./1 float./0               | no                                               | TÜBİTAK YITAL<br>3 μm CMOS <sup>d</sup>     | $\pm 5$            | 159 k                     | -                           | NA                                                       |

| [4] <sup>a</sup>                         | Voltage-mode      | 1 CCII+                          | NA                    | 2 float./1 float./0            | no                                               | $D^{d}$                                     | $\pm 12$           | 159 k                     | _                           | NA                                                       |

| [5] <sup>a</sup>                         | Voltage-mode      | 1 CCII-                          | NA                    | 1 float.; 1 gr./1 float./0     | no                                               | D <sup>e</sup>                              | $\pm 12$           | 1 k                       | _                           | NA                                                       |

| [6] <sup>a</sup>                         | Voltage-mode      | 2 CCII+                          | NA                    | 2 gr./2 gr./0                  | no                                               | De                                          | $\pm 12$           | 15.9 k                    | _                           | NA                                                       |

| [7]                                      | Voltage-mode      | 1 DO-CCII                        | 23°                   | 2 float./1 gr./0               | no                                               | TSMC 350 nm CMOS <sup>d</sup>               | $\pm 1.5$          | 1 M                       | _                           | NA                                                       |

| [8]                                      | Voltage-mode      | 1 MCCII-                         | 21 <sup>c</sup>       | 2 float./1 gr./0               | no                                               | TSMC 350 nm CMOS <sup>d</sup>               | $\pm 2.5$          | 1 M                       | _                           | NA                                                       |

| [9] <sup>a</sup>                         | Voltage-mode      | 1 FD-Op-Amp                      | NA                    | 1 float./1 float./0            | yes                                              | D <sup>e</sup>                              | $\pm 5$            | 33.9 k                    | _                           | NA                                                       |

| [10]                                     | Voltage-mode      | 1 VD-DIBA                        | NA                    | 0/1 gr./0                      | yes                                              | De                                          | $\pm 5$            | 316 k                     | _                           | NA                                                       |

| [11]                                     | Voltage-mode      | 1 VDIBA                          | 6°                    | 0/1 float./0                   | yes                                              | TSMC 180 nm CMOS <sup>d</sup>               | $\pm 0.9$          | 9.44 M                    | 10.5 m                      | NA                                                       |

| [12] <sup>a</sup>                        | Voltage-mode      | 2 OTA, 1 DVB                     | 34°                   | 0/1 gr./0                      | no                                               | TSMC 180 nm CMOS <sup>d</sup>               | $\pm 0.9$          | 1.658 M                   | _                           | NA                                                       |

| [13]                                     | Voltage-mode      | 2 Subtractors                    | 20                    | 1 float./1 gr./0               | yes                                              | IBM 130 nm CMOS <sup>d</sup>                | $\pm 0.75$         | 6.37 M                    | 1.77 m                      | NA                                                       |

| [14]                                     | Voltage-mode      | MOS-RC circuit                   | 6                     | 1 float./1 gr./0               | yes                                              | 350 nm CMOSf                                | 3.3                | 1.59 M                    | _                           | NA                                                       |

| [15]                                     | Current-mode      | MOS-C circuit                    | 10                    | 0/1 float./0                   | no                                               | 40 nm CMOS <sup>d</sup>                     | $\pm 1.25$         | 512 k                     | 980 μ                       | NA                                                       |

| [16] <sup>a</sup>                        | Voltage-mode      | 2 IVB                            | 5                     | 0/1 float./0                   | yes                                              | TSMC 180 nm CMOS <sup>d</sup>               | $\pm 0.9$          | 3.18 M                    | - '                         | NA                                                       |

| [17] <sup>a</sup>                        | Current-mode      | BJT-C circuit                    | 6°                    | 0/1 gr./0                      | yes                                              | PR100N (PNP)<br>& NP100N (NPN) <sup>d</sup> | 1.5                | 159 k                     | 169 $\mu$                   | NA                                                       |

| [18]                                     | Current-mode      | 2 DO-CF                          | 10                    | 0/1 gr./0                      | yes                                              | TSMC 180 nm CMOSd                           | $\pm 0.9$          | 2.99 M                    | 266 μ                       | NA                                                       |

| [19] <sup>a</sup>                        | Voltage-mode      | MOS-only circuit                 | 4 <sup>c</sup>        | 0/0/0                          | no                                               | TSMC 350 nm CMOSg1                          | 1.65               | 150 M                     | _ ′                         | NA                                                       |

| [20]                                     | Current-mode      | MOS-RL circuit                   | 3                     | 1 float./0/1 gr.               | no                                               | IBM 130 nm CMOSg2                           | 1.5                | 8.74 G                    | 19 m                        | $186 \ \mu\text{m} \times 125 \ \mu\text{m}$             |

| [21]a                                    | Current-mode      | MOS-C circuit                    | 8                     | 0/1 float./0                   | no                                               | TSMC 180 nm CMOS <sup>d</sup>               | 1.8                | 9.4 M                     | 760 μ                       | NA                                                       |

| This work                                |                   |                                  |                       |                                |                                                  |                                             |                    |                           | •                           |                                                          |

| (core circuit<br>in Fig. 1)              | Voltage-mode      | MOS-only circuit                 | 3°                    | 0/0/0                          | no                                               | _                                           | -                  | -                         | -                           | NA                                                       |

| This work<br>(full circuit<br>in Fig. 4) | Voltage-mode      | MOS-C circuit                    | 12                    | 0/1 gr./0                      | no                                               | TSMC 180 nm CMOS <sup>g2</sup>              | 1.8                | 4.825 M                   | 92.57 $\mu$                 | $31.1~\mu{\rm m}{	imes}39.5~\mu{\rm m}$                  |

- Not mentioned; NA: Not applicable; D: Discrete IC(s) used: [2], [4], [6] AD844; [9] LMH6550; [10] OPA860 & AD8130

- <sup>a</sup> Considered circuit: [2] Fig. 1; [3] Fig. 2(a); [4] Fig. 2(a); [5] Fig. 1; [6] Fig. 1; [6] Fig. 3; [12] Fig. 3; [12] Fig. 1; [16] Fig. 2; [17] Fig. 4; [19] Fig. 3(a); [21] Fig. 3(a)

<sup>b</sup> Refer Appendix for nomenclature of the ABBs

- c Ideal current source(s) used

- <sup>d</sup> OrCAD PSpice simulation results

- Experimental measurement results

- HSPICE simulation results

- g Cadence IC6 Spectre simulation results: 1pre-layout; 2post-layout

transconductance gains of  $2g_{m3} = g_{m2}$ , routine analysis yields the following transfer function (TF):

$$T(s) = \frac{V_{\text{OUT}}}{V_{\text{IN}}} = \frac{-g_{\text{m1}} + sC_{\text{gs2}}}{g_{\text{m1}} + sC_{\text{gs2}}},$$

(1)

where  $g_{mn}$  and  $C_{gsn}$  represent the transconductances and gate-to-source capacitances of the n-th transistor, respectively. In this circuit  $C_{\rm gs2}$  can directly be used as the filter's capacitor if a high frequency operation is desired, but it can be shunted by a metal-insulatormetal (MIM) on-chip capacitor to improve linearity and as remedy against tolerances of gate-to-source capacitance. From (1), the phase response and the pole  $(\omega_{\rm p})$ and zero  $(\omega_z)$  frequencies of the filter can be respec-

Figure 1: The proposed first-order voltage-mode all-pass filter core circuit.

tively calculated as:

$$\varphi(\omega) = 180^{\circ} - 2\tan^{-1}\left(\frac{\omega C_{\rm gs2}}{g_{\rm m1}}\right),$$

(2)

and

$$\omega_{\rm p} = \omega_{\rm z} = \frac{g_{\rm m1}}{C_{\rm gs2}}.\tag{3}$$

Hence, from (2) it can be seen that the proposed VM APF can provide phase shifting between 180° (at  $\omega = 0$ ) to  $0^{\circ}$  (at  $\omega = \infty$ ). The pole and zero frequency sensitivities of the proposed APF core are given as:

$$S_{g_{\rm m1}}^{\omega_{\rm p},\omega_{\rm z}} = -S_{C_{\rm gs2}}^{\omega_{\rm p},\omega_{\rm z}} = 1,$$

(4)

which are not higher than unity in magnitude.

# 3. Non-Ideal Analysis and Compensation for Non-Ideal Effects

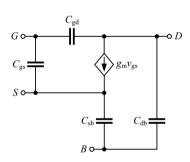

MOS transistor small-signal ac model including dominant parasitic elements is shown in Fig. 2. From a signal point of view it behaves as a voltage-controlled current source, which accepts a signal  $v_{\rm gs}$  between gate and source and provides a current  $g_{\rm m}v_{\rm gs}$  at the drain terminal. The input resistance of this controlled source is very high, ideally infinite, while the output resistance that is looking into the drain is also high.

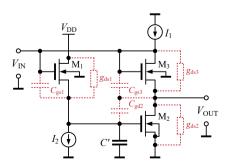

The proposed first-order VM APF core circuit including main parasitics is shown in Fig. 3. The following mathematical analysis is only focused on the effect of channel-length modulation, which is modeled by output resistance  $r_{\rm o}$  of MOSFETs. Therefore, the body effect is ignored due to simplicity and other parasitic capacitances can also be neglected since they are either in parallel with  $C_{\rm gs2}$  or their value can be too small compared to  $C_{\rm gs2}$ . Indicating the output resistances of MOS transistors as  $r_{\rm on}=1/g_{\rm dsn}$  for n=(1,2,3) and considering  $C'=C+C_{\rm gs2}$ , where C is a MIM on-chip capacitor used in the implemented filter, the TF in (1) turns to (for  $2g_{\rm m3}=g_{\rm m2}$ ):

$$T'(s) = \frac{V_{\text{OUT}}}{V_{\text{IN}}} = \frac{\left[g_{\text{ds3}}\left(g_{\text{m1}} + g_{\text{ds1}}\right) + g_{\text{m3}}\left(g_{\text{ds1}} - g_{\text{m1}}\right) + sC'\left(g_{\text{m3}} + g_{\text{ds3}}\right)\right]}{\left(g_{\text{m3}} + g_{\text{ds2}} + g_{\text{ds3}}\right)\left(g_{\text{m1}} + g_{\text{ds1}} + sC'\right)}.$$

(5)

For the compensation of undesired  $g_{\rm ds}$  parasitics, TF (5) was recalculated for the matching condition of  $kg_{\rm m3}=g_{\rm m2}$  instead of  $2g_{\rm m3}=g_{\rm m2}$  to obtain:

$$T''(s) = \frac{V_{\text{OUT}}}{V_{\text{IN}}} = \frac{\left\{g_{\text{m3}} \left[g_{\text{m1}} (1 - k) + g_{\text{ds1}}\right] + + g_{\text{ds3}} \left(g_{\text{m1}} + g_{\text{ds1}}\right) + sC' \left(g_{\text{m3}} + g_{\text{ds3}}\right)\right\}}{\left(g_{\text{m3}} + g_{\text{ds2}} + g_{\text{ds3}}\right) \left(g_{\text{m1}} + g_{\text{ds1}} + sC'\right)}.$$

(6)

Figure 2: Simplified small-signal ac model of a MOS transistor.

Figure 3: The proposed first-order VM APF core circuit including main parasitic elements.

From (6) we can find a  $k = g_{\rm m2}/g_{\rm m3}$  value as given below that will preserve the all-pass response:

$$k = \frac{2(g_{\rm m1} + g_{\rm ds1})(g_{\rm m3} + g_{\rm ds3})}{g_{\rm m1}g_{\rm m3}}.$$

(7)

Using k in (6), the following TF can be obtained:

$$T'''(s) = \frac{V_{\text{OUT}}}{V_{\text{IN}}} =$$

$$= -\frac{(g_{\text{m3}} + g_{\text{ds3}}) (g_{\text{m1}} + g_{\text{ds1}} - sC')}{(g_{\text{m3}} + g_{\text{ds2}} + g_{\text{ds3}}) (g_{\text{m1}} + g_{\text{ds1}} + sC')}.$$

(8)

Note that here the APF response is preserved with a slightly modified gain and phase responses. However, for the slight deviation in the phase response due to  $g_{\rm ds1}$ , phase compensation is easily possible by decreasing  $g_{\rm m1}$  by an amount of  $g_{\rm ds1}$ .

## 4. Simulation Results

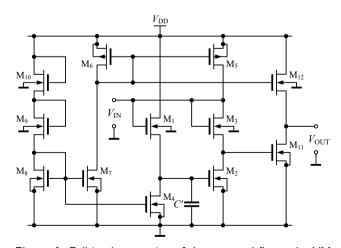

To verify the theoretical study, the behavior of the designed first-order VM APF with full implementation shown in Fig. 4 has been verified by simulations in Cadence IC6 Spectre analog design environment. In the structure, transistors M<sub>1</sub>-M<sub>3</sub> represent the initial core filter shown in Fig. 1 and  $M_4-M_{10}$  realize the bias current sources  $I_1$ ,  $I_2$ . In addition, transistors  $M_{11}$  and M<sub>12</sub> operate as an inverting voltage level shifter, which is very favorable sub-circuit for low-voltage operation since it employs only two NMOS transistors between its rails. It can be clearly seen that the first presented circuit shown in Fig. 1 has an offset voltage problem at the output. This offset voltage can be defined as  $V_{

m OUT} = V_{

m IN} - V_{

m gs3}$  in Fig. 1. Therefore, in the full implementation,  $M_{11}$  and  $M_{12}$  transistors are added to the design to eliminate the output offset voltage. Therefore, the offset voltage can be calculated as follows:  $V_{\text{OUT}} = -(V_{\text{IN}} - V_{\text{gs1}} + V_{\text{gd11}})$ . DC power sup-

**Figure 4:** Full implementation of the proposed first-order VM APF core circuit.

**Table 2**Aspect ratios of MOSFETs in implemented first-order VM APF shown in Fig. 4.

| PMOS Transistors | W ( $\mu$ m) / L ( $\mu$ m) |

|------------------|-----------------------------|

| $M_5$            | 20.2 / 1                    |

| $M_6$            | 4 / 1                       |

| NMOS Transistors | W ( $\mu$ m) / L ( $\mu$ m) |

| $M_1$            | 3 / 1                       |

| $M_2$            | 76 / 5.6                    |

| $M_3$            | 2.3 / 1.15                  |

| $M_4$ , $M_8$    | 3.5 / 0.5                   |

| $M_7$            | 3.5 / 1.1                   |

| $M_9$ , $M_{10}$ | 1.4 / 2                     |

| $M_{11}$         | 32 / 1                      |

| $M_{12}$         | 3 / 2.9                     |

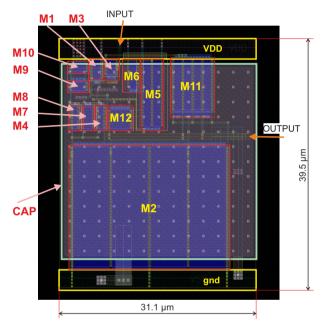

**Figure 5:** Layout of the designed first-order VM APF shown in Fig. 4.

ply voltage was set equal to  $V_{\rm DD}=1.8$  V, all transistors with recommended minimal length 300 nm are of medium  $V_{\rm th}$ , which were modeled by the TSMC 180 nm CMOS process parameters available in EUROPRACTICE IC Service design kit. The aspect ratios of transistors are listed in Table 2. Note that the W/L ratio of the transistor M<sub>2</sub> should be selected sufficiently high to reach significantly greater  $C_{\rm gs}$  than other parasitics in the circuit. The corresponding layout with proper labeling and dimension 31.1  $\mu$ m×39.5  $\mu$ m is depicted in Fig. 5. During design DRC (design rule check) and ERC (electrical rule check) have been successfully performed. The total power consumption of the designed filter is found to be 92.57  $\mu$ W.

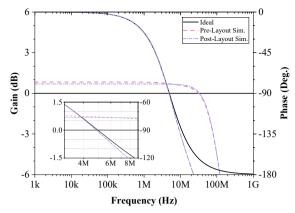

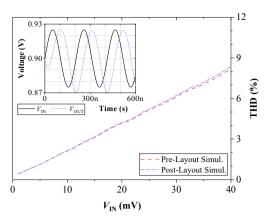

First of all, the performance of the filter was tested by AC analyses. Fig. 6 shows the ideal, pre-layout,

**Figure 6:** Ideal, pre-layout, and post-layout simulated gain and phase responses of the first-order VM APF and corresponding zoom in pole frequency region as inset.

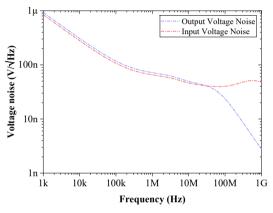

**Figure 7:** Post-layout simulated output and equivalent input noise variations vs. frequency.

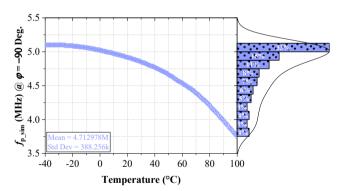

**Figure 8:** Post-layout simulated temperature dependence of pole frequency and corresponding histogram.

and post-layout (extraction settings: distributed resistors, distributed capacitors, coupling capacitors, no inductance) simulated gain and phase responses of the first-order VM APF and corresponding zoom in pole frequency region as inset. In simulations the value of the capacitor C has been selected as 1.79 pF. Note that this MIM capacitor (in layout labeled as CAP) appears parallel with  $C_{\rm gs2}$  parasitic capacitance of the transistor  $\rm M_2$ , which value is equal to 2.18 pF. Theoret-

**Figure 9:** THD variation of the proposed first-order VM APF against applied input voltages at 4.825 MHz and post-layout simulated example of time-domain response with applied input voltage with amplitude of 25 mV as inset.

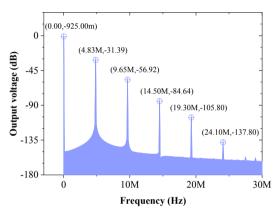

**Figure 10:** Post-layout simulated FFT spectrum of the proposed first-order VM APF.

ically, therefore, its total value equal to  $C' \approx 3.97 \text{ pF}$ should be taken into account. Hence, the  $-90^{\circ}$  phase shift is at pole frequency  $f_{\rm p\_sim} \cong 4.825$  MHz, which is close to the ideal  $f_{\rm p\_theor}$  equal to 4.94 MHz. The gain response for the output is flat far beyond the pole frequency in large frequency range. The obtained prelayout and post-layout simulated gains at  $f_{\rm p\_sim}$  are equal to 0.71 dB and 0.68 dB, respectively. The gain roll-off and discrepancy against theoretical gain 0 dB can be mainly attributed to non-unity gain of the inverting voltage level shifter sub-circuit. The output and equivalent input noise variations against frequency have also been simulated, as it is shown in Fig. 7. The equivalent output/input noises at post-layout simulated pole frequency are found as  $57.7 \text{ nV}/\sqrt{\text{Hz}}$  and  $53.2 \text{ nV}/\sqrt{\text{Hz}}$ , respectively. The effect of temperature on  $f_{\rm p}$  sim of the proposed APF at  $\varphi = -90^{\circ}$  was examined in range  $T \in \{-40; +100\}^{\circ}$ C and the post-layout simulation results with corresponding statistical evaluation are depicted in Fig. 8.

To illustrate the time-domain performance, transient analysis is performed to evaluate the voltage swing

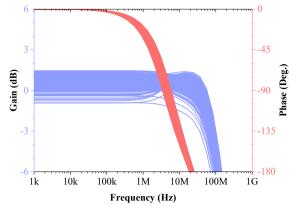

**Figure 11:** Monte Carlo statistical analysis: Post-layout simulated gain and phase responses change due to variation of process, mismatch, transistors, and capacitor.

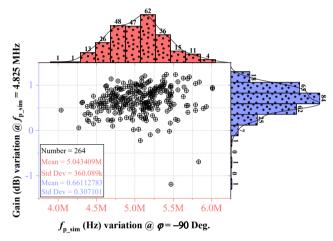

**Figure 12:** Evaluation of Monte Carlo statistical analysis results shown in Fig. 11: Variations of the pole frequency at  $-90^{\circ}$  vs. variations of the gain of VM APF at simulated pole frequency 4.825 MHz.

capability and phase errors of the filter. The pre-layout and post-layout simulated total harmonic distortion (THD) variations with respect to amplitude of the applied sinusoidal input voltage at  $f_{\rm p\_sim}$  are depicted in Fig. 9. As an example, post-layout simulated time-domain result is shown as inset in which a sine-wave input of 25 mV amplitude was applied to the filter and it yields THD value of 5.2%. Moreover, the corresponding FFT spectrum of the output signal is shown in Fig. 10.

Finally, in order to evaluate the potential vary of the proposed filter parameters due to tolerances incurred from manufacturing processes, Monte Carlo statistical analysis is performed with default setting for process, mismatch, transistors, and MIM capacitor tolerances and 264 runs. Note that manufacturing processes may affect the value of each MOS, however, vary in value of  $\rm M_2$  is the most critical for the proposed VM APF. Therefore, potential change of  $g_{\rm m2}$  is during filter implementation reduced by precise design of bias circuitry (proper settings of transistors  $\rm M_9$  and

$M_{10}$ ) and especially thanks to use of medium  $V_{\rm th}$  transistors. Fig. 11 shows the post-layout simulated gain and phase responses of the proposed APF. Histograms in Fig. 12 demonstrate the variations of the pole frequency at  $-90^{\circ}$  with mean value 5.043 MHz and variations of the gain of APF at simulated pole frequency  $f_{\rm p\_sim} \cong 4.825$  MHz with mean value 0.66 dB, respectively.

Computed Cadence IC6 Spectre post-layout simulation results are in good agreement with theory and confirm the feasibility of the proposed circuit for on-chip fabrication.

# 5. Conclusion

In this brief, a simple first-order voltage-mode allpass filter with reduced complexity designed with MOSonly technique is presented. The circuit has a potential to be used as an intermediate block in analog design applications. In particular, in this work the VM APF is implemented using medium  $V_{\rm th}$  transistors supplied with 1.8 V voltage and modeled by the TSMC 180 nm CMOS process parameters available in EUROPRAC-TICE IC Service design kit. The functionality of the circuit is verified in detail with numerous post-layout simulations. The simulated pole frequency of the implemented VM APF is 4.825 MHz and its layout occupies an area of 31.1  $\mu$ m×39.5  $\mu$ m. The total power consumption is found to be only 92.57  $\mu$ W. Depending on the selected sub-nanometer integrated circuit technology and the capacitor value, the circuit can operate in GHz frequency region.

# Appendix

This section provides full nomenclature of the mentioned ABBs in Table 1 in alphabetical order.

CCII+ (-): Plus-Type (Minus-Type) Second-Generation

Current Conveyor

DO-CCII: Dual-Output Second-Generation Current

Conveyor

DO-CF: Dual-Output Current Follower

DVB: Differential Voltage Buffer

DV-VB: Differential-Voltage Voltage Buffer FD-Op-Amp: Fully-Differential Operational Amplifier

FTFN: Four-Terminal Floating Nullor IVB: Inverting Voltage Buffer

MCCII-: Minus-Type Modified Second-Generation

Current Conveyor

OTA: Operational Transconductance Amplifier VD-DIBA: Voltage Differencing-Differential Input

Buffered Amplifier

VDIBA: Voltage Differencing Inverting Buffered

Amplifier

# **Declaration of Competing Interest**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

# Acknowledgments

This study is supported by Bogazici University Research Fund BAP 10740, Turkey. This article is also based upon support of international mobility project MeMoV, No. CZ.02.2.69/0.0/0.0/16\_027/00083710 funded by European Union, Ministry of Education, Youth and Sports, Czech Republic and Brno University of Technology, and National Sustainability Program under grant LO1401. For the research, infrastructure of the SIX Center was used. Authors also wish to thank the anonymous reviewers for their useful and constructive comments that helped to improve the paper and Habip Bilgin for his support during the preparation of the initial version of the manuscript.

### References

- Higashimura M, Fukui Y. Research note Realization of allpass networks using a current conveyor. Int. Journal of Electronics 1988:65(2):249-250.

- [2] Khan IA, Maheshwari S. Simple first order all-pass section using a single CCII. Int. Journal of Electronics 2000;87(3):303-6.

- [3] Cam U, Cicekoglu O, Gulsoy M, Kuntman H. New voltage and current mode first-order all-pass filters using single FTFN. Frequenz 2000;54(7-8):177-9.

- [4] Toker A, Ozcan S, Kuntman H, Cicekoglu O. Supplementary all-pass sections with reduced number of passive elements using a single current conveyor. Int. Journal of Electronics 2001;88(9):969-76.

- [5] Pandey N, Paul SK. All-pass filters based on CCII- and CCCII-. Int. Journal of Electronics 2004;91(8):485-9.

- [6] Horng JW. Current conveyors based allpass filters and quadrature oscillators employing grounded capacitors and resistors. Computers and Electrical Engineering 2005;31:81-92.

- [7] Metin B, Pal K. Cascadable allpass filter with a single DO-CCII and a grounded capacitor. Analog Integrated Circuits and Signal Processing 2009;61(3):259-63.

- [8] Metin B, Cicekoglu O. Component reduced all-pass filter with a grounded capacitor and high impedance input. Int. Journal of Electronics 2009;96(5):445-55.

- [9] Biolek D, Biolkova V. All-pass filters employing differential Op-Amps. Electronics World 2010;116(1891):44-45.

- [10] Biolek D, Biolkova V. First-order voltage-mode all-pass filter employing one active element and one grounded capacitor. Analog Integrated Circuits and Signal Processing 2010;65(1):123-9.

- [11] Herencsar N, Minaei S, Koton J, Yuce E, Vrba K. New resistorless and electronically tunable realization of dual-output VM all-pass filter using VDIBA. Analog Integrated Circuits and Signal Processing 2013;74(1):141-54.

- [12] Sotner R, Jerabek J, Herencsar N, Petrzela J, Dostal T, Vrba K. First-order adjustable transfer sections for synthesis suitable for special purposes in constant phase block approximation. AEU-International Journal of Electronics and Communications 2015;69:1334-45.

- [13] Abaci A, Yuce E. Voltage-mode first-order universal filter realizations based on subtractors. AEU-International Journal of Electronics and Communications 2018;90:140-6.

- [14] Maundy BJ, Aronhime P. A novel CMOS first order all pass filter. Int. Journal of Electronics 2002;89(9):739-43.

- [15] Lahiri A. New CMOS-based resistor-less current-mode firstorder all-pass filter using only ten transistors and one external capacitor. Radioengineering 2011;20(3):638-43.

- [16] Minaei S, Yuce E. High input impedance NMOS-based phase shifter with minimum number of passive elements. Circuits, Systems, and Signal Processing 2012;31(1):51-60.

- [17] Tangsrirat W. On the realization of first-order current-mode AP/HP filter. Radioengineering 2013;22(4):1007-15.

- [18] Safari L, Minaei S, Yuce E. CMOS first-order current-mode all-pass filter with electronic tuning capability and its applications. Journal of Circuits, Systems, and Computers 2013;22(3):1350007-17.

- [19] Yildiz HA, Ozoguz S, Toker A, Cicekoglu O. On the realization of MOS-only allpass filter. Circuits, Systems, and Signal Processing 2013;32(3):1455-65.

- [20] Ahmadi P, Taghavi MH, Belostotski L, Madanayake A. A 0.13-\(\mu\)m CMOS current-mode all-pass filter for multi-GHz operation. IEEE Trans. on Very Large Scale Integration (VLSI) Systems 2015;23(12):2813-8.

- [21] Ozenli D, Yesil A, Arslan E, Kuntman H. Novel first order current mode MOS-C phase shifters. Elektronika ir Elektrotechnika 2018;24(1):31-5.

- [22] Arslan E, Metin B, Cicekoglu O. MOSFET-only multifunction biquad filter. AEU-International Journal of Electronics and Communications 2015;69(12):1737-40.

- [23] Uygur A, Metin B, Kuntman H, Cicekoglu O. Current mode MOSFET-only third order Butterworth low pass filter with DTMOS tuning technique. Analog Integrated Circuits and Signal Processing 2016;89:645-54.

- [24] Atasoyu M, Metin B, Kuntman H, Cicekoglu O. Simple realization of a third order Butterworth filter with MOSonly technique. AEU-International Journal of Electronics and Communications 2017;81:205-8.

- [25] Aydin O, Yildiz HA, Ozoguz S, Toker A. MOS-only complex filter design for dual-band GNSS receivers. AEU-International Journal of Electronics and Communications 2017;82:83-92.

- [26] Cicekoglu O, Herencsar N, Metin B. Supplementary MOSonly Butterworth LP BP filter circuits. In: 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Georgia, Batumi; 2017. p. 194-7.

- [27] Yesil A, Ozenli D, Arslan E, Kuntman H. Current mode single-input multi-output MOSFET-only filter. AEU-International Journal of Electronics and Communications 2017;80:157-64.

- [28] Yildiz HA. MOS-only polyphase filter with small chip area. Analog Integrated Circuits and Signal Processing 2018;97(1):59-68.

- [29] Ozenli D, Alaybeyoglu E, Kuntman H, Cicekoglu O. MOSFET-Only filter design automation based on polynomial regression with exemplary circuits. AEU-International Journal of Electronics and Communications 2018;84:342-54.

- [30] Metin B, Cicekoglu O, Ozoguz S. A class of MOSFET-C multifunction filters. Analog Integrated Circuits and Signal Processing 2018;97(1):5-13.

- [31] Pal A. Low-Power VLSI Circuits and Systems. Springer, New Delhi, 2015. ISBN 978-8132219361.