### **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

# DEPARTMENT OF POWER ELECTRICAL AND ELECTRONIC ENGINEERING

ÚSTAV VÝKONOVÉ ELEKTROTECHNIKY A ELEKTRONIKY

# COMPARISON AND OPTIMIZATION OF DC/DC POWER CONVERSION TOPOLOGIES USING GAN FET TECHNOLOGY FOR HIGH EFFICIENCY AND POWER DENSITY POWER CONVERTERS

SROVNÁNÍ A OPTIMALIZACE TOPOLOGIÍ PRO DC/DC KONVERZI ENERGIE S POUŽITÍM TECHNOLOGIE GAN FET PRO MĚNIČE S VYSOKOU ÚČINNOSTÍ A OBJEMOVOU HUSTOTOU VÝKONU

#### **DOCTORAL THESIS**

DIZERTAČNÍ PRÁCE

AUTHOR Ing. Michal Šír

**AUTOR PRÁCE**

SUPERVISOR doc. Ing. Pavel Vorel, Ph.D.

ŠKOLITEL

**BRNO 2021**

#### **Abstract**

Focus of this thesis is the analysis of the current state of GaN semiconductor technology in power electronics and its application on DC/DC converter, optimized for high efficiency and high power density with the intention to use it in server and telecom applications.

The theoretical part analyzes problems and challenges related to novel GaN technology, such as gate driving for various internal structures, layout optimization for cooling of minimized surface mount packages without constraining parasitic elements affecting switching performance. Precise losses calculation for totem-pole power factor correction converter using novel GaN technology is included. Results and ideas resulting from theoretical analysis of various problems are applied in the design of prototype and verified by series of measurements, proving the benefits of novel technology and its potential to impact power electronics applications around us. Deep description of current measurement technique with high bandwidth, control loop operation and its implementation in digital signal processor is included.

#### **Abstrakt**

Táto práca je zameraná na analýzu súčastného stavu GaN polovodičovej techniky vo výkonovej elektronike a jej aplikáciu v DC/DC meničoch, optimalizovaných na účinnosť a vysokú objemovú hustotu výkonu s cielom použitia v serveroch a telekomunikačných zariadeniach.

Teoretická časť analyzuje problémy a výzvy spojené s novou technológiou GaN, ako napríklad riadenie hradla pre rôzne vnútorné štruktúry dostupné na trhu, optimalizácia plošných spojov pre chladenie minimalizovaných púzdier pre povrchovú montáž s cielom minimalizovať parazitné prvky. V práci je zahrnutý presný výpočet strát pre aktívny usmerňovač realizovaný pomocou novej technológie GaN. Výsledky a nápady získané teoretickou analýzou rôznych problémov sú aplikované pri návrhu prototypu a overené sériou meraní, ktoré dokazujú výhody novej technológie a jej potenciál ovplyvniť aplikácie výkonovej elektroniky okolo nás. Zahrnutý je podrobný popis merania prúdu s veľkou šírkou pásma, fungovania regulačnej slučky a jej implementácie v digitálnom signálnom procesore.

#### Keywords

Gallium Nitride semiconductors, Cooling of minimized surface mount devices, Novel  $R_{DSon}$  Measurement method, Dynamic  $R_{DSon}$ , High Efficiency GaN half bridge, GaN Totem Pole converter

#### Kľúčové slová

GaN polovodiče, Chladenie minimalizovaných púzdier pre povrchovú montáž, Nová metóda merania dynamického  $R_{DSon}$ , Dynamický  $R_{DSon}$ , Vysoko účinný menič s GaN

#### **Bibliographic citation**

ŠÍR, Michal. Comparison and Optimization of DC/DC Power Conversion Topologies Using GaN FET Technology for High Efficiency and Power Density Power Converters. Brno, 2021. Available also at: <a href="https://www.vutbr.cz/studenti/zav-prace/detail/137332">https://www.vutbr.cz/studenti/zav-prace/detail/137332</a>. Doctoral Thesis. Vysoké učení technické v Brně, Fakulta elektrotechniky a komunikačních technologií, Department of Power Electrical and Electronic Engineering. Supervisor Pavel Vorel.

#### **Author's Declaration**

I declare that I have written this doctoral thesis "Comparison and optimization of DC/DC power conversion topologies using GaN FET technology for high efficiency and power density power converters" independently, under the guidance of the advisor and using exclusively the technical references and other sources of information cited in the project and listed in the comprehensive bibliography at the end of the project.

As the author, I furthermore declare that, with respect to the creation of this paper, I have not infringed any copyright or violated anyone's personal and/or ownership rights. In this context, I am fully aware of the consequences of breaking Regulation S 11 of the Copyright Act No. 121/2000 Coll. of the Czech Republic, as amended, and of any breach of rights related to intellectual property or introduced within amendments to relevant Acts such as the Intellectual Property Act or the Criminal Code, Act No. 40/2009 Coll., Section 2, Head VI, Part 4.

#### Prehlásenie

Prehlasujem, že svoju dizertačnú prácu na tému "Srovnání a optimalizace topologií pro DC/DC konverzi energie s použitím technologie GaN FET pro měniče s vysokou účinností a objemovou hustotou výkonu" som vypracoval samostatne pod vedením vedúceho dizertačnej práce a s použitím odbornej literatúry a dalších informačných zdrojov, ktoré sú citovane v práci a uvedené v zozname literatury na konci práce.

Ako autor uvedenej dizertačnej práce prehlasujem, že v súvislosti s vytvorením tejto dizertačnej práce som neporušil autorské práva tretích osôb, hlavne som nezasiahol nedovoleným spôsobom do cudzích autorských práv osobnostných a som si plne vedomý následkov porušenia ustanovení § 11 a nasledujúceho autorského zákona č. 121/2000 Sb., vrátane možných trestnoprávnych dôsledkov vyplývajúcich z ustanovenia druhej časti, hlavy VI. diel 4 Trestného zákonníka č. 40/2009 Sb.

| Brno, August 22, 2021    |                    |

|--------------------------|--------------------|

| 51110, 1 tagast 22, 2021 | author's signature |

| A | ckn  | owl    | led | gm | ents | ; |

|---|------|--------|-----|----|------|---|

|   | CILL | 0 11 2 |     | 5  |      | • |

I would like to thank supervisor of doctoral thesis doc. Pavel Vorel for methodological, pedagogical and professional help and valuable advice in the elaboration of my dissertation.

#### Poďakovanie

Ďakujem vedúcemu dizertačnej práce doc. Pavlovi Vorlovi za účinnú metodickú, pedagogickú a odbornú pomoc a dalšie cenné rady pri vypracovaní mojej dizertačnej práce.

author's signature

#### DEPARTMENT OF POWER ELECTRICAL AND ELECTRONIC ENGINEERING Faculty of Electrical Engineering and Communication Brno University of Technology

### **CONTENTS**

| LIST OF FIGURES                                                    | 3  |

|--------------------------------------------------------------------|----|

| LIST OF TABLES                                                     | 6  |

| INTRODUCTION                                                       | 7  |

| 1 PRESENT GAN TECHNOLOGY OVERVIEW                                  | 9  |

| 1.1 D-MODE GAN                                                     | 9  |

| 1.2 E-MODE GAN                                                     | 10 |

| 1.3 GAN CASCODE                                                    | 11 |

| 1.4 GATE INJECTION TRANSISTOR                                      | 13 |

| 1.5 ABSENCE OF AVALANCHE MODE                                      | 14 |

| 2 THESIS GOALS                                                     | 15 |

| 3 STUDY OF GATE DRIVER CONSIDERATIONS FOR VARIOUS TECHNOLOGIES     |    |

| 3.1 OVERCURRENT PROTECTION BY DRIVER                               | 16 |

| 3.2 VOLTAGE TRANSIENT IMMUNITY REQUIREMENTS – CMTI                 | 16 |

| 3.3 E-MODE                                                         | 17 |

| 3.4 GIT                                                            | 18 |

| 3.5 CASCODE                                                        | 19 |

| 4 COOLING OF MINIMIZED SURFACE MOUNT PACKAGES                      | 20 |

| 4.1 TOP SIDE COOLING                                               | 20 |

| 4.2 BOTTOM SIDE COOLING                                            | 21 |

| 4.3 PCB WITH COPPER INLAYS                                         | 22 |

| 4.4 PCB WITH THERMAL VIAS                                          | 24 |

| 4.5 IDEA OF PCB ON INSULATED METAL SUBSTRATE FOR POWER ELECTRONICS | 29 |

| 4.6 SUMMARY                                                        | 33 |

| 5 ASPECTS OF PCB CONSTRUCTION FOR HIGH OPERATING FREQUENCY         |    |

| CONVERTERS                                                         |    |

| 5.1 LOW INDUCTIVE LAYOUT                                           |    |

| 5.2 DIELECTRIC LOSSES AND PARASITIC CAPACITANCE                    |    |

| 5.3 UTILIZATION OF COPPER FOR LOW POWER LOSSES                     | 36 |

| 6 DYNAMIC R <sub>DS-ON</sub> OF GAN DEVICES                        | 38 |

| 6.1 THEORY OF MEASUREMENT                                          | 38 |

| 6.2 DESCRIPTION OF TEST SETUP                                      | 39 |

| 6.2.1 Power circuit                                                |    |

| 6.2.2 MEASUREMENT CIRCUIT                                          |    |

| 6.3 TEST RESULTS                                                   |    |

| 6.3.1 SHORT TRANSIENT INCREASE                                     |    |

| 6.3.2 Long transient increase                                      | 41 |

#### DEPARTMENT OF POWER ELECTRICAL AND ELECTRONIC ENGINEERING Faculty of Electrical Engineering and Communication Brno University of Technology

| 7 OPTIMIZATION OF DC/DC CONVERTER USING GAN SEMICONDUCTO SWITCHING APPLICATIONS |    |

|---------------------------------------------------------------------------------|----|

| 7.1 POWER STAGE DESIGN                                                          |    |

| 7.2 INDUCTOR OPTIMIZATION FOR HIGH EFFICIENCY AT HALF LOAD                      |    |

| 7.3 GAN POWER STAGE LOSSES EVALUATION                                           | 54 |

| 7.4 SYNCHRONOUS RECTIFIER                                                       | 59 |

| 7.5 ADDITIONAL LOSSES                                                           | 60 |

| 7.6 CONTROL LOOP DESIGN                                                         | 60 |

| 7.6.1 Transition mode power factor correction                                   |    |

| 7.6.2 CONTROL LOOP OF TOTEM POLE CONVERTER                                      |    |

| 7.6.3 DEBUG TOOL FOR DIGITALLY CONTROLLED SYSTEMS                               |    |

| 7.7 CURRENT SENSE TECHNIQUE                                                     |    |

| 7.8 DESIGN VERIFICATION                                                         | 74 |

| 8 RECUPERATING GATE DRIVE SOLUTION                                              | 85 |

| 9 CONCLUSION                                                                    | 90 |

| LITERATURE                                                                      | 92 |

| SYMBOLS AND ABBREVIATIONS                                                       | 95 |

| LIST OF APPENDICES                                                              | 97 |

| LIST OF AUTHOR'S PUBLICATIONS                                                   | 98 |

| CURRICULUM VITAE                                                                | 99 |

# DEPARTMENT OF POWER ELECTRICAL AND ELECTRONIC ENGINEERING Faculty of Electrical Engineering and Communication Brno University of Technology

### LIST OF FIGURES

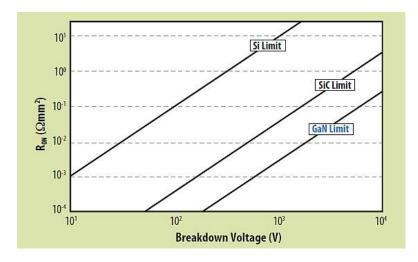

| Fig. | . 1: Theoretical limits of Si, SiC and GaN material, [7]                                                                                                         | 7  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

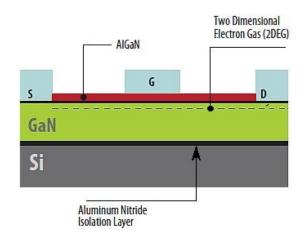

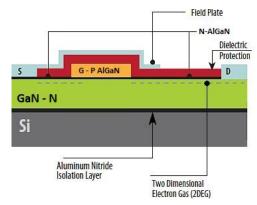

| Fig. | . 2: Depletion mode GaN transistor structure, [7]                                                                                                                | 9  |

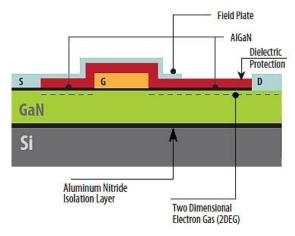

| Fig. | . 3: Enhanced mode GaN transistor structure, [7]                                                                                                                 | 10 |

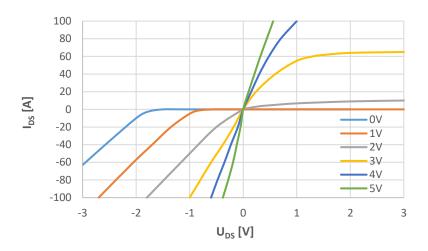

| Fig. | . 4: Enhanced mode GaN output characteristics                                                                                                                    | 11 |

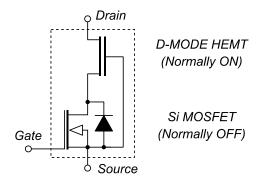

| Fig. | . 5: GaN Cascode power transistor                                                                                                                                | 11 |

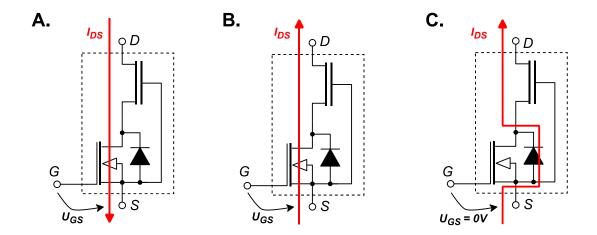

| Fig. | . 6: GaN Cascode operating modes                                                                                                                                 | 12 |

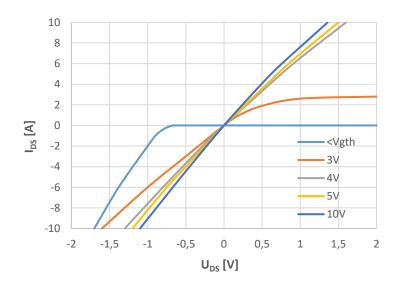

| Fig. | . 7: GaN Cascode output characteristics                                                                                                                          | 12 |

| Fig. | . 8: Gate injection transistor structure, [7]                                                                                                                    | 13 |

| Fig. | . 9: GIT transistor output characteristics                                                                                                                       | 13 |

| Fig. | . 10: Output characteristics and Avalanche mode of MOSFET                                                                                                        | 14 |

| Fig. | . 11: E-mode Gate Driving circuit with parasitic elements                                                                                                        | 17 |

| Fig. | . 12: Proper GIT driver with control diagram, [1EDF5673 Datasheet]                                                                                               | 18 |

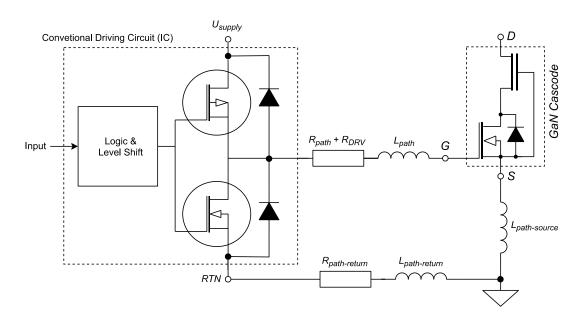

| Fig. | . 13: Cascode Gate Driving circuit with parasitic elements                                                                                                       | 19 |

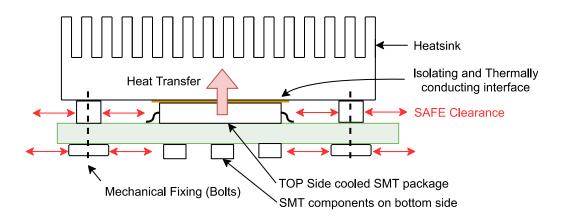

| Fig. | . 14: Top side cooling mechanical construction                                                                                                                   | 20 |

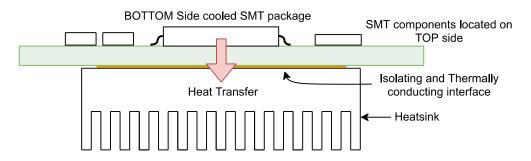

| Fig. | . 15: Bottom side cooling mechanical construction                                                                                                                | 21 |

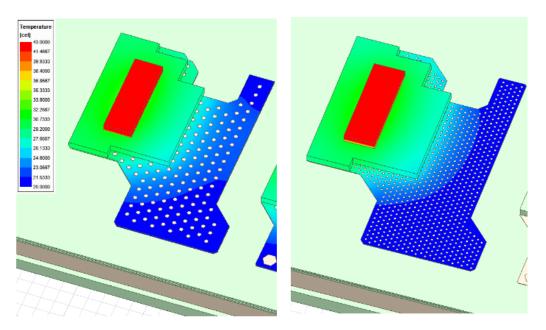

| Fig. | . 16: Copper inlay thermal simulation                                                                                                                            | 22 |

| Fig. | . 17: Copper fill factor                                                                                                                                         | 24 |

| Fig. | . 18: Plot of copper fill factor for three different via wall plating thicknesses, $k=0.25mm$                                                                    | 25 |

| Fig. | . 19: Plot of copper fill factor for three different drill hole distances, $c = 100 \mu m$                                                                       | 25 |

| Fig. | . 20: High resolution mesh of simulated thermal vias                                                                                                             | 26 |

| Fig. | . 21: Thermal Simulation of PCB variant A, k=0.3mm, D= 0.7mm, c= 100µm, PCB thickness= 2mm                                                                       | 27 |

| Fig. | . 22: Thermal Simulation of PCB variant B, k=0.25mm, D=0.5mm, c=100µm, PCB thickness= 1.5mm                                                                      | 27 |

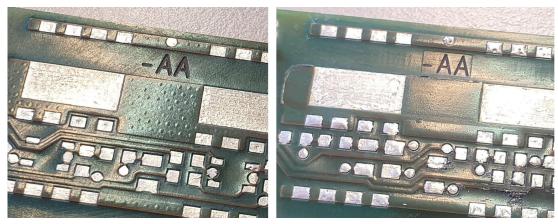

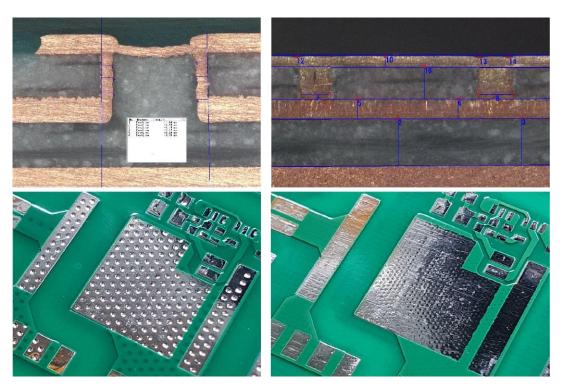

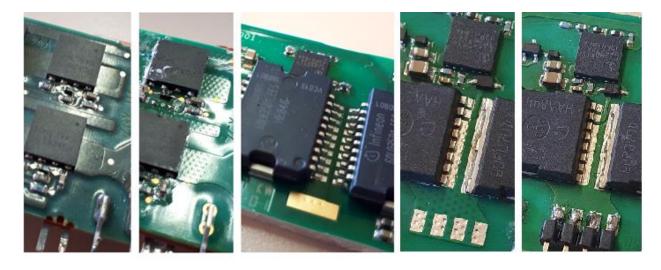

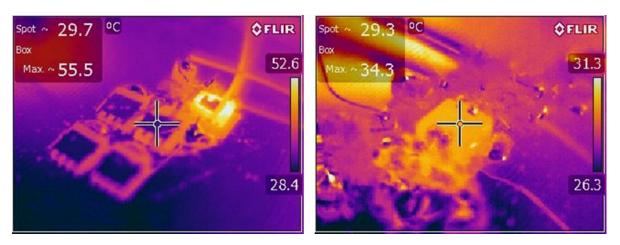

| Fig. | . 23: Pictures of prototypes – printed circuit board with thermal vias technology (left), PCB with copper inlay (riassembled prototype                           |    |

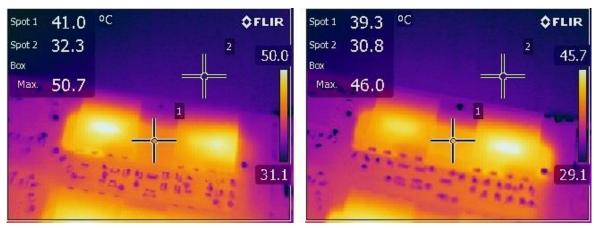

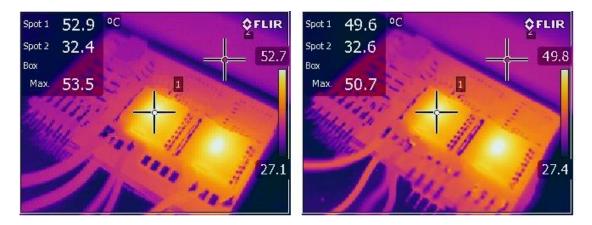

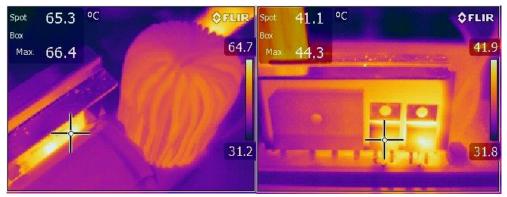

| Fig. | . 24: Thermal camera picture of FR4 based PCB – copper inlay (right), optimized thermal vias (left). Power loss 5V spot no.2 represents the heatsink temperature |    |

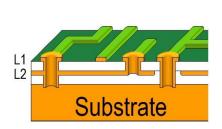

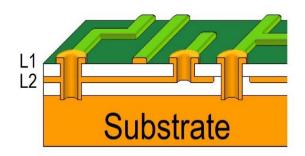

| Fig. | . 25: Cross section of dual layer IMS board, suitable for power electronics application                                                                          | 29 |

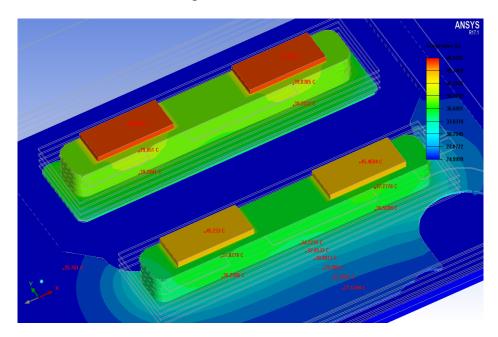

| Fig. | . 26: Thermal simulation of Insulated Metal Substrate PCB                                                                                                        | 29 |

| Fig. | . 27: Thermal simulation of Insulated Metal Substrate PCB                                                                                                        | 30 |

| Fig. | . 28: Micro-section analysis and surface photos of tested prototypes - variant A (left), variant B (right)                                                       | 31 |

| Fig. | . 29: Thermal camera picture of IMS PCB - variant A (left), variant B (right). Spot no.2 represents the heatsink temp                                            |    |

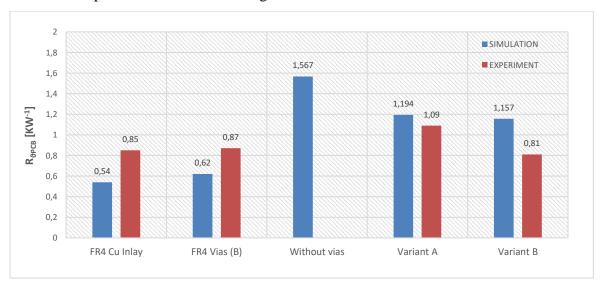

| Fig. | . 30: Summary of the temperature rise on the PCB (w/o insulating foil) for all simulated and tested solutions                                                    | 32 |

| _    | . 31: Physical construction of simulated samples (Copper Inlay, Thermal Vias B, IMS)                                                                             |    |

| Fig. | . 32: Stack up of IMS PCB ideal for reduction of loop inductance                                                                                                 | 35 |

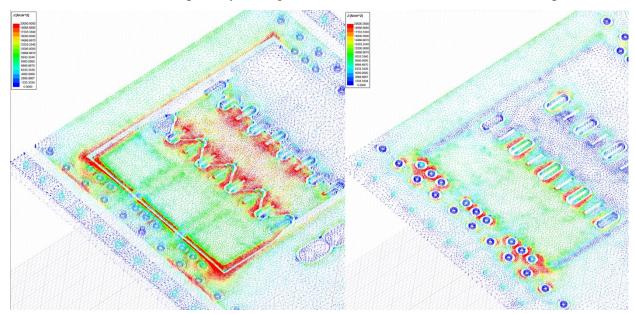

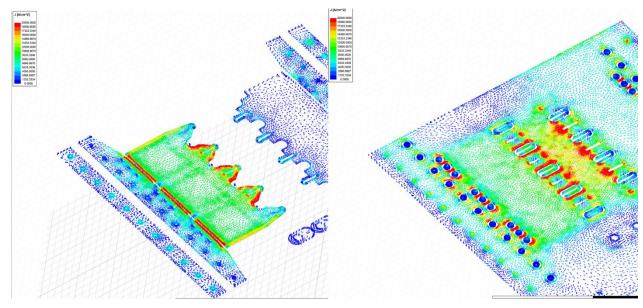

|      | . 33: Distribution of alternating current in PCB layers (before optimization)                                                                                    |    |

|      | . 34: Distribution of alternating current in PCB layers (after optimization)                                                                                     |    |

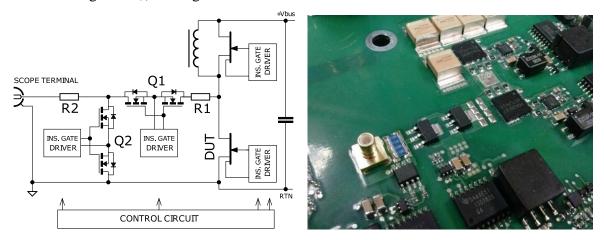

| Fig. | . 35: Block diagram of dynamic R <sub>DSon</sub> measurement setup                                                                                               | 39 |

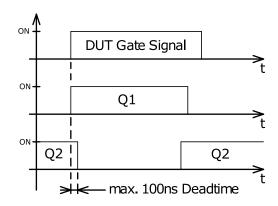

| Fig. | . 36: Switching diagram of Q1 and Q2 vs. DUT timing                                                                                                              | 40 |

# DEPARTMENT OF POWER ELECTRICAL AND ELECTRONIC ENGINEERING Faculty of Electrical Engineering and Communication Brno University of Technology

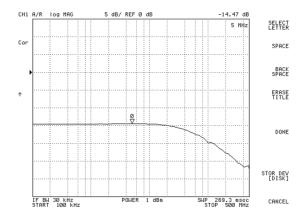

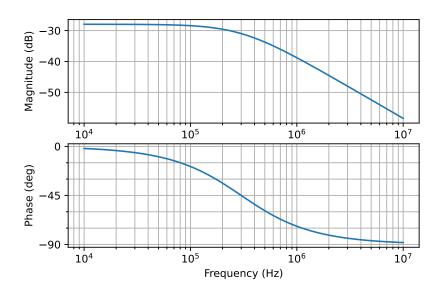

| Fig. | . 37: Transfer function of the measurement signal path                                                                                                                                                                                                                                    | . 40 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

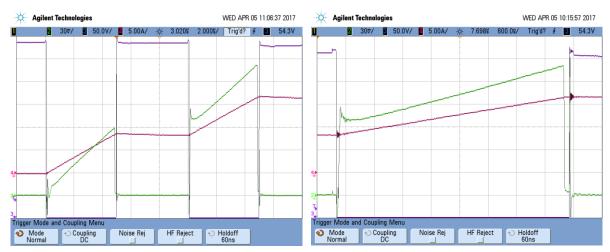

| Fig. | . 38: Scope snapshot of GaN R <sub>DSon</sub> tester operation                                                                                                                                                                                                                            | . 41 |

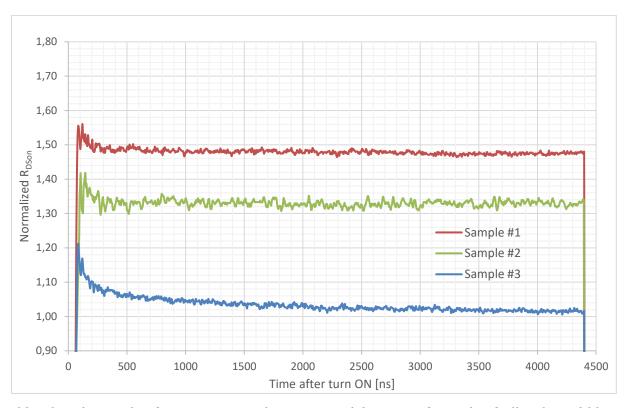

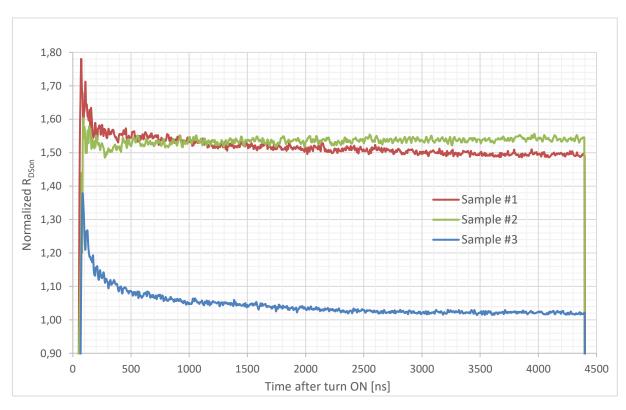

| Fig. | . 39: Plot of normalized R <sub>DSon</sub> vs. time after turn-on of three tested samples, bulk voltage 200V                                                                                                                                                                              | . 42 |

| Fig. | . 40: Plot of normalized R <sub>DSon</sub> vs. time after turn-on of three tested samples, bulk voltage 400V                                                                                                                                                                              | . 42 |

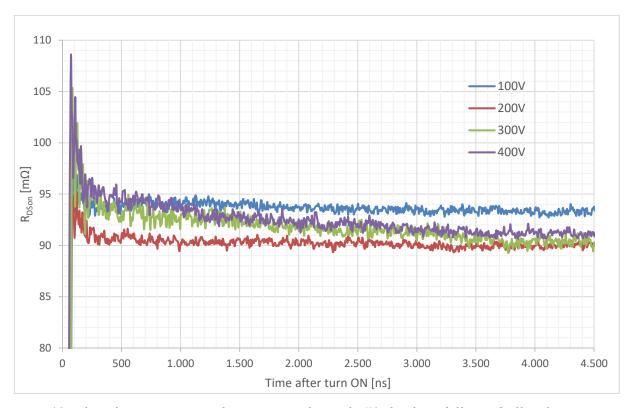

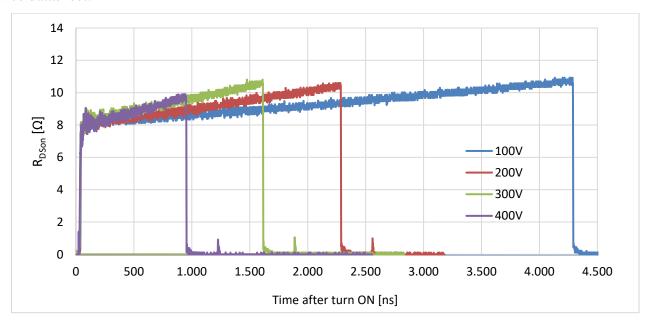

| Fig. | . 41: Plot of R <sub>DSon</sub> vs. time after turn-on of sample #1, for four different bulk voltages                                                                                                                                                                                     | . 43 |

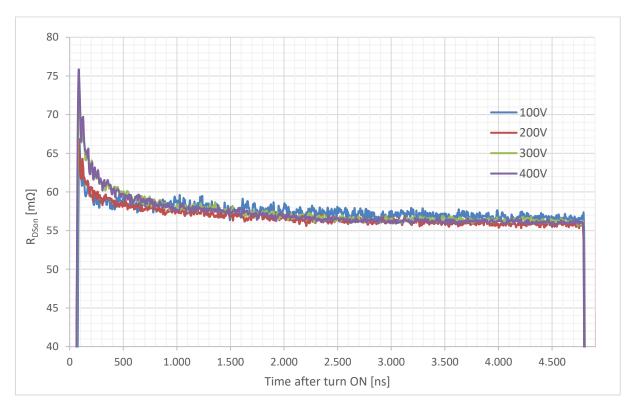

| Fig. | . 42: Plot of R <sub>DSon</sub> vs. time after turn-on of sample #3, for four different bulk voltages                                                                                                                                                                                     | . 43 |

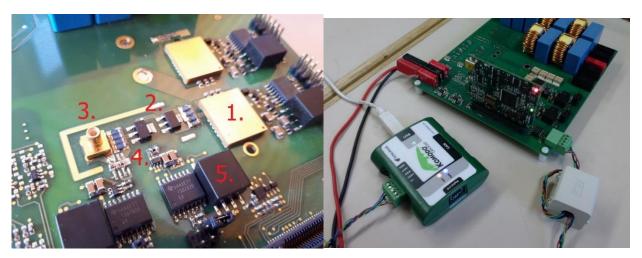

| Fig. | . 43: Detail of the proposed tester (during sample #2 test)                                                                                                                                                                                                                               | . 44 |

| Fig. | . 44: Plot of R <sub>DSon</sub> vs. time after turn-on of silicon transistor STD1NK60, for four different bulk voltages                                                                                                                                                                   | . 45 |

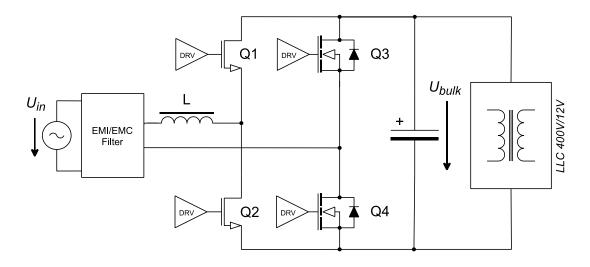

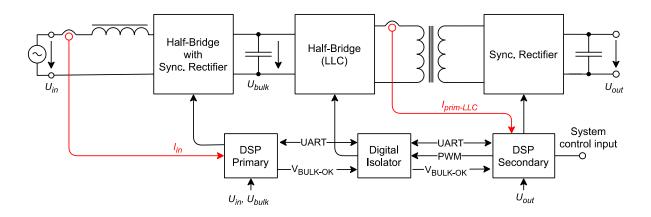

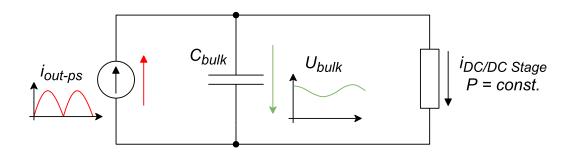

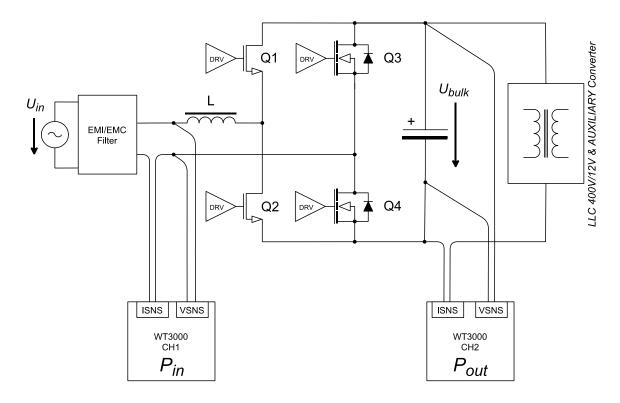

| Fig. | . 45: Simplified block diagram of totem pole power factor correction converter with a DC/DC converter on the output                                                                                                                                                                       | . 46 |

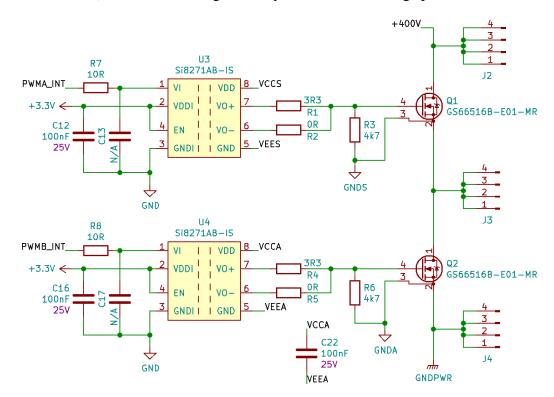

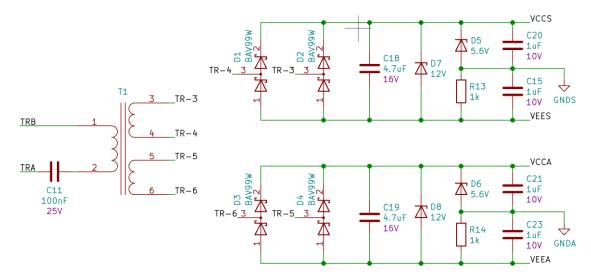

| Fig. | 46: Schematic of GS66516B gate driver                                                                                                                                                                                                                                                     | . 48 |

| Fig. | 47: Schematic of isolated driver power supply                                                                                                                                                                                                                                             | . 49 |

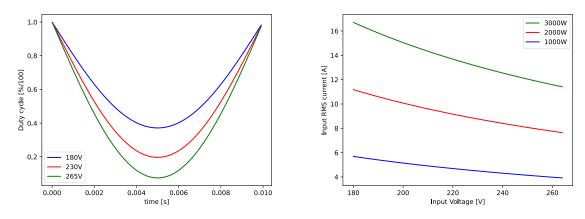

| Fig. | . 48: Plot of duty cycle of totem pole converter during half period of input voltage (left), plot of input current RMS valu various operating conditions (right)                                                                                                                          |      |

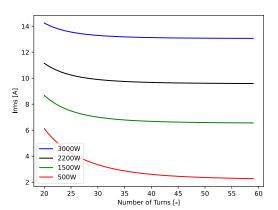

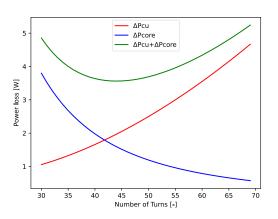

| Fig. | . 49: Plot of input RMS current versus number of turns and various output operating conditions (left), Plot of inductor to power losses versus number of turns at nominal operating condition (right)                                                                                     |      |

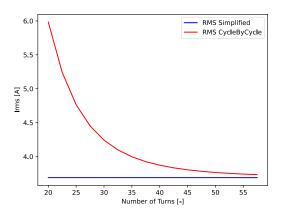

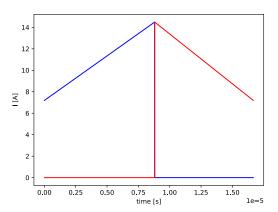

| Fig. | . 50: Difference in RMS current flowing through power switch versus number of turns calculated by simplified and cycle cycle calculation (left), Plot of current waveform in one switching cycle (T <sub>line</sub> =2ms, N=40, 230V <sub>in</sub> /3kW) (blue-high side, to side switch) | red- |

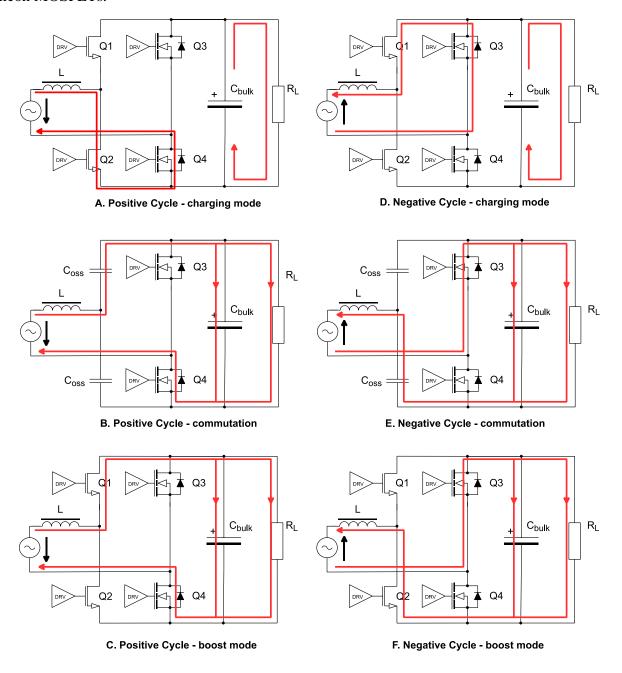

| Fig. | . 51: Totem pole converter operating states                                                                                                                                                                                                                                               | . 56 |

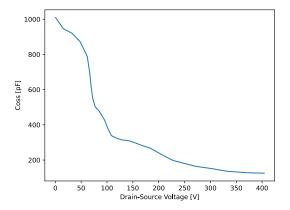

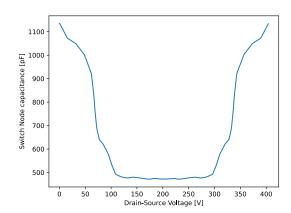

| Fig. | . 52: Digitalized Coss capacitance used for calculation (right), Switch node capacitance (excl. PCB layout, left)                                                                                                                                                                         | . 57 |

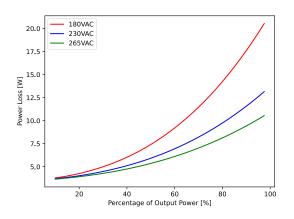

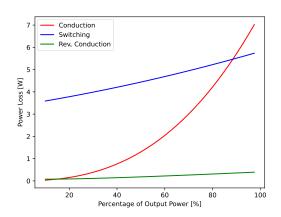

| Fig. | . 53: Results of power losses calculation of GaN MOSFETs in 3kW totem-pole converter, dependency on output power and in voltage (left), overview of power losses at nominal operating conditions (right)                                                                                  |      |

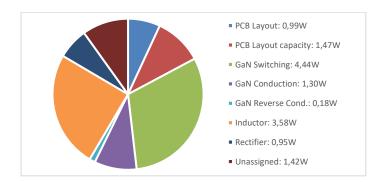

| Fig. | . 54: Power losses distribution at nominal operating conditions                                                                                                                                                                                                                           | . 60 |

| Fig. | . 55: Block diagram of digitally controlled power converter with galvanic isolation                                                                                                                                                                                                       | . 61 |

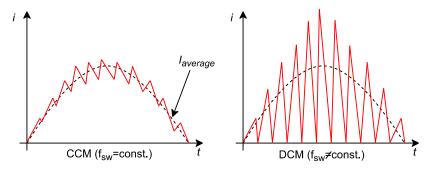

| Fig. | . 56: Comparison of PFC inductor current in CCM and DCM mode of operation                                                                                                                                                                                                                 | . 62 |

| Fig. | . 57: Scope snapshot of DSP in/out signals configured for DCM mode                                                                                                                                                                                                                        | . 62 |

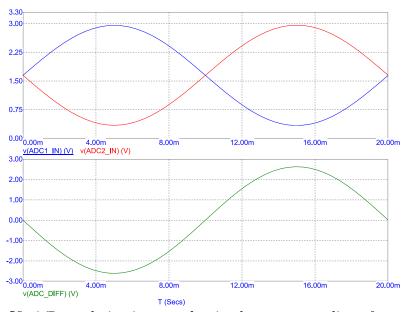

| Fig. | . 58: A/D resolution increase by simultaneous sampling of two channels                                                                                                                                                                                                                    | . 63 |

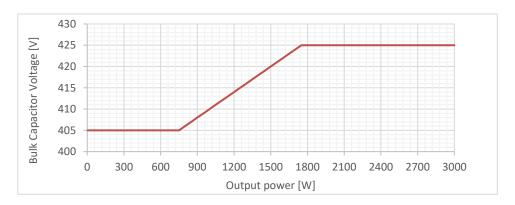

| Fig. | . 59: Adaptive bulk capacitor voltage curve                                                                                                                                                                                                                                               | . 64 |

| Fig. | . 60: Equivalent schematic of bulk voltage ripple estimator                                                                                                                                                                                                                               | . 65 |

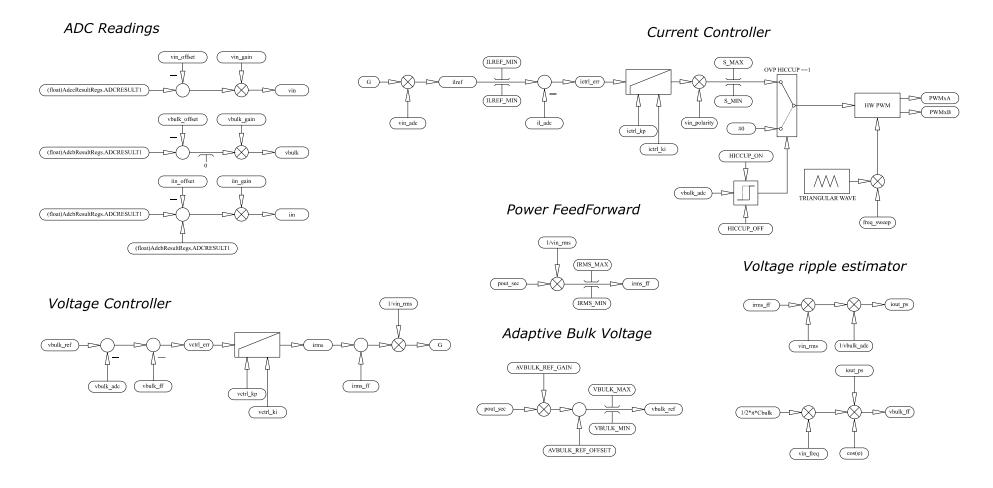

| Fig. | . 61: Totem Pole PFC Control loop block diagram                                                                                                                                                                                                                                           | . 66 |

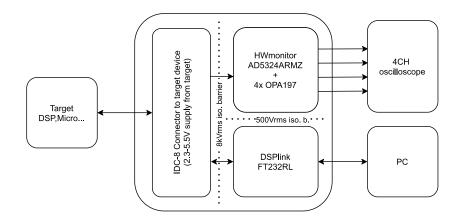

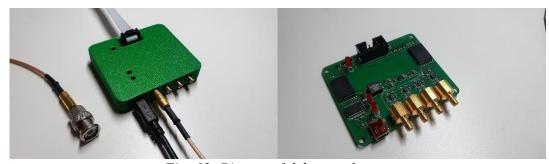

| Fig. | . 62: Block diagram of debug tool for digitally controlled systems                                                                                                                                                                                                                        | . 67 |

| Fig. | 63: Picture of debug tool prototype                                                                                                                                                                                                                                                       | . 67 |

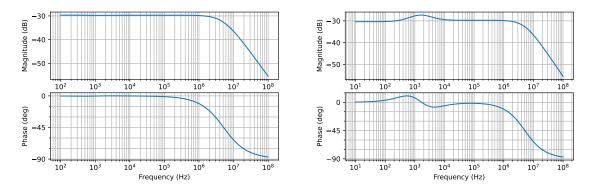

| Fig. | . 64. Amplitude and phase characteristic of hall effect sensor (approximated)                                                                                                                                                                                                             | . 68 |

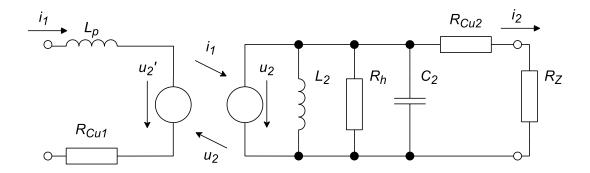

| Fig. | . 65. Equivalent circuit of current transformer, [11]                                                                                                                                                                                                                                     | . 69 |

| Fig. | . 66. Amplitude and phase characteristic of current transformer                                                                                                                                                                                                                           | . 70 |

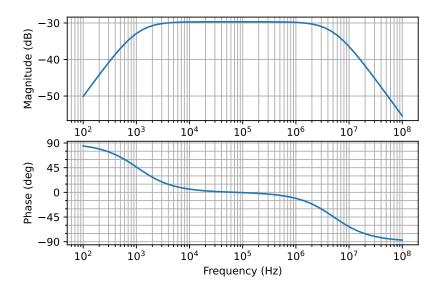

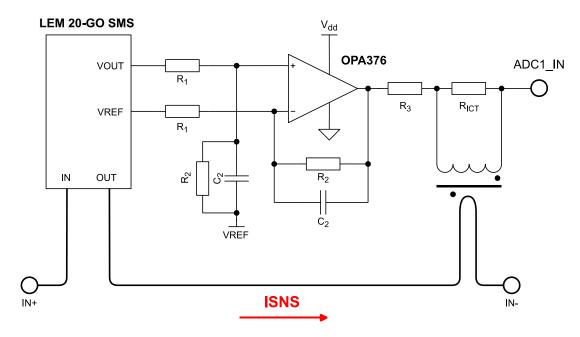

| Fig. | . 67. Simplified schematic of designed current sensor                                                                                                                                                                                                                                     | . 71 |

| Fig. | . 68. Amplitude and phase characteristic of designed current sensor using merged outputs of two measurement methors simulated tolerance of the feedback components (right)                                                                                                                |      |

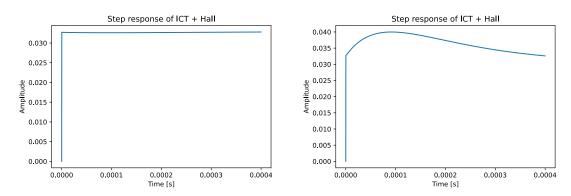

| Fig. | . 69. Step response of designed current sensor using merged outputs of two measurement methods, simulated tolerance of feedback components (right)                                                                                                                                        |      |

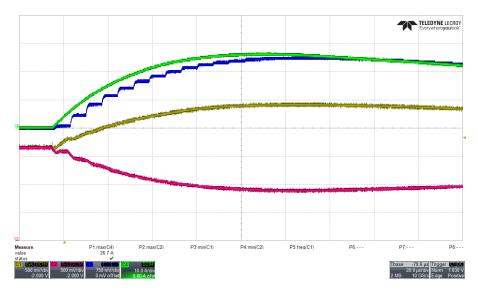

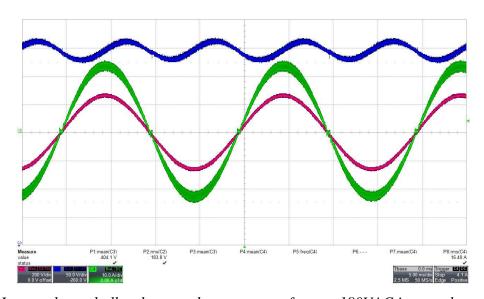

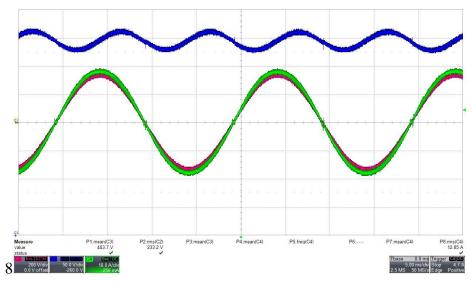

| Fig. | . 70: Operation of the current sensor prototype (DC current step), measured current (Green), Output of operational amplifit positive (Yellow), Output of operational amplifier - negative (Red), Digitalized current measured by DSP (Blue), timeb 20µs/div                               | base |

#### DEPARTMENT OF POWER ELECTRICAL AND ELECTRONIC ENGINEERING Faculty of Electrical Engineering and Communication Brno University of Technology

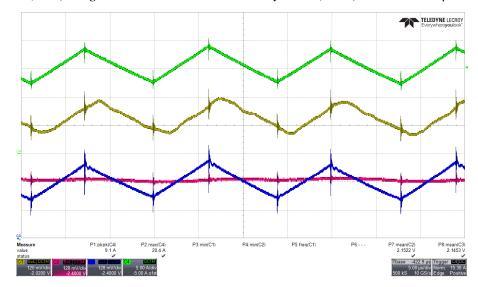

| Fig. | 71: Operation of the current sensor with GaN PFC converter (Blue), current measured with 50MHz current probe (Green) Output of operational amplifier (Red), Output of Hall effect sensor (Yellow), timebase 5µs/div |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

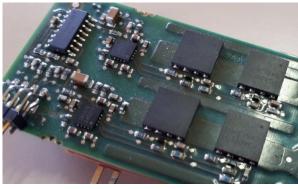

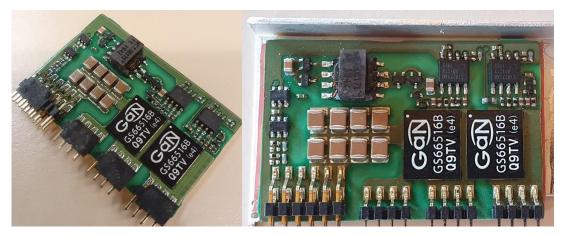

| Fig. | 72: Tested prototype – Insulated metal substrate board with GaN (GS66516B) half-bridge and insulated gate drivers after SML assembly (left), assembled to the aluminum heatsink (right)                             |

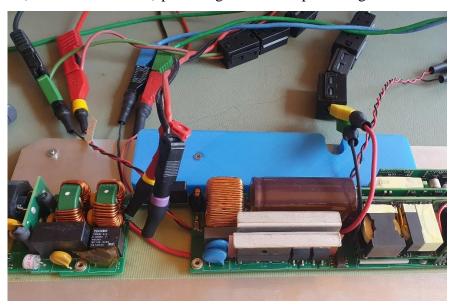

| Fig. | 73: Tested prototype – Efficiency measurement test setup                                                                                                                                                            |

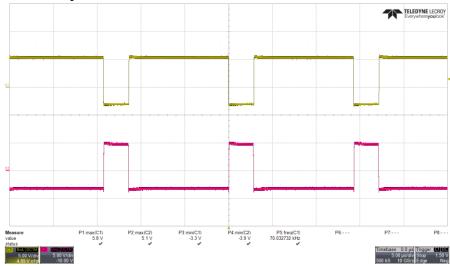

| Fig. | 74: Gate driving signal for High and Low side device in Half-Bridge at U <sub>DS</sub> =0V, timebase 5µs/div                                                                                                        |

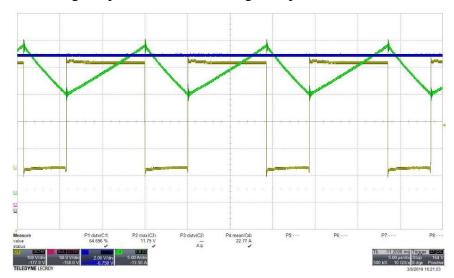

| Fig. | 75: Drain-Source voltage (Yellow) of GaN Half-Bridge at DC input voltage, green waveform is power stage current, timebase 5µs/div                                                                                   |

| Fig. | 76: Drain-Source voltage (Yellow) of GaN Half-Bridge at DC input voltage with detail on rising edge, green waveform i. power stage current, timebase 20ns/div                                                       |

| Fig. | 77: Drain-Source voltage (Yellow) of GaN Half-Bridge at DC input voltage with detail on falling edge, green waveform is power stage current, timebase 20ns/div                                                      |

| Fig. | 78: Drain-Source voltage (Yellow) of GaN Half-Bridge at DC input voltage with detail on rising edge, green waveform in power stage current, timebase 20ns/div                                                       |

| Fig. | 79: Drain-Source voltage (Yellow) of GaN Half-Bridge at DC input voltage with detail on falling edge, green waveform i. power stage current, timebase 20ns/div                                                      |

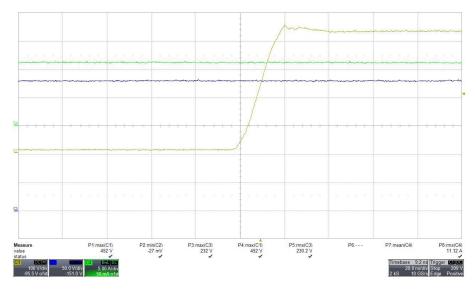

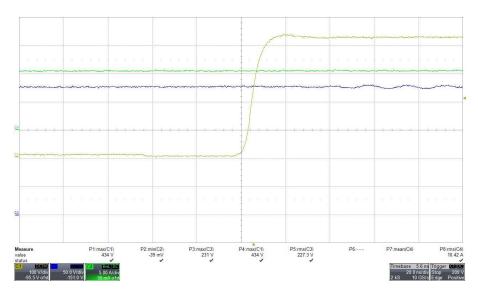

| Fig. | 80: Input voltage, bulk voltage and current waveform at 180VAC input voltage and 3kW output power (90kHz switching frequency), timebase 5ms/div                                                                     |

| Fig. | 81: Input voltage, bulk voltage and current waveform at 230VAC input voltage and 3kW output power (90kHz switching frequency), timebase 5ms/div                                                                     |

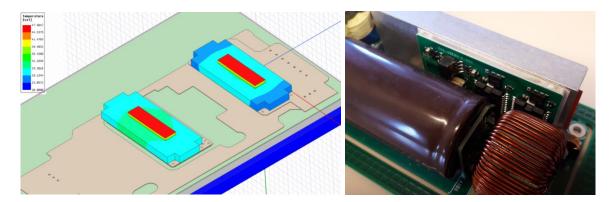

| Fig. | 82: Thermal camera picture of power stage during operation at full power 3kW – GaN half bridge on insulated metal substrate board (left), synchronous rectifiers (right)                                            |

| Fig. | 83: Pictures of prototype with optimized inductor – reference for thermal camera picture                                                                                                                            |

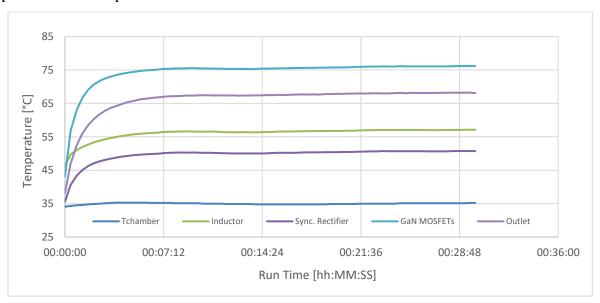

| Fig. | 84: Verification of thermal performance at corner operating conditions (180VAC,3kW)                                                                                                                                 |

| Fig. | 85: WT3000 power analyzer connection for efficiency measurement                                                                                                                                                     |

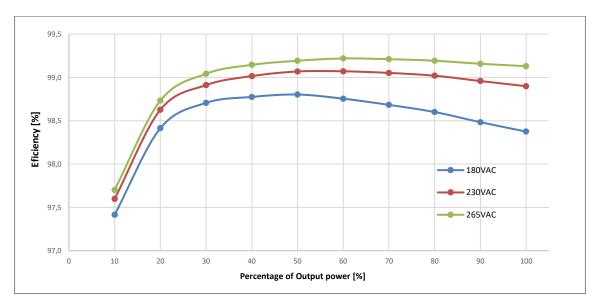

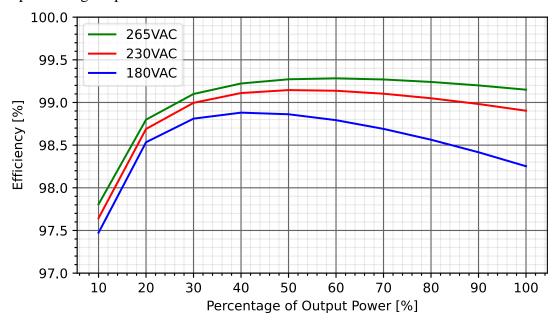

| Fig. | 86: Measured efficiency curves of tested prototype for various input voltage and output power conditions (at 60kHz)                                                                                                 |

| Fig. | 87: Calculated efficiency curves of tested prototype for various input voltage and output power conditions (at 60kHz) 82                                                                                            |

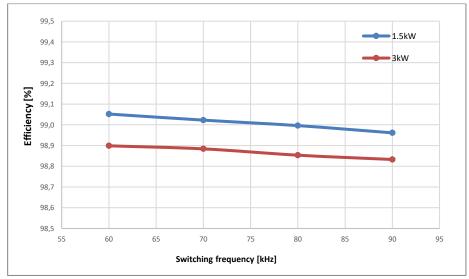

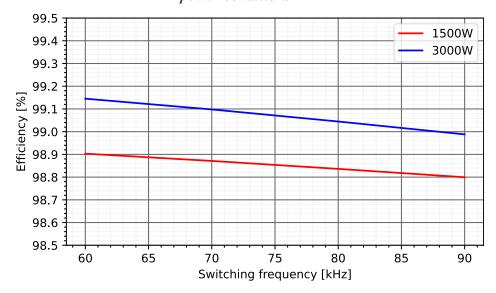

| Fig. | 88: Measured efficiency curves of tested prototype for switching frequency and output power conditions                                                                                                              |

| Fig. | 89: Calculated efficiency curves of tested prototype for switching frequency and output power conditions                                                                                                            |

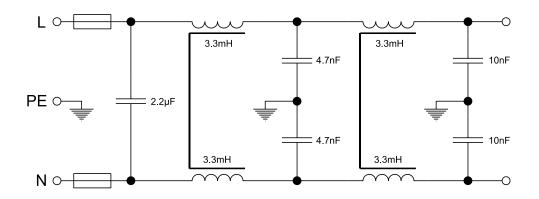

| Fig. | 90: Schematic of EMC filter used                                                                                                                                                                                    |

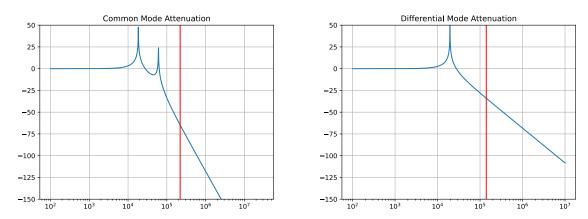

| Fig. | 91: Calculated attenuation of EMC filter                                                                                                                                                                            |

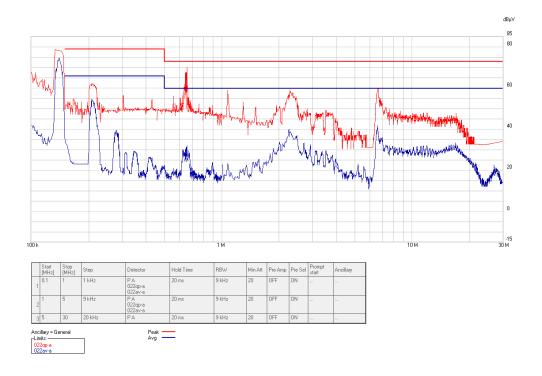

| Fig. | 92: Conducted emission spectrum of GaN totem pole PFC operating with LLC converter, measured at Line input, nomina input voltage 230VAC (70kHz switching frequency)                                                 |

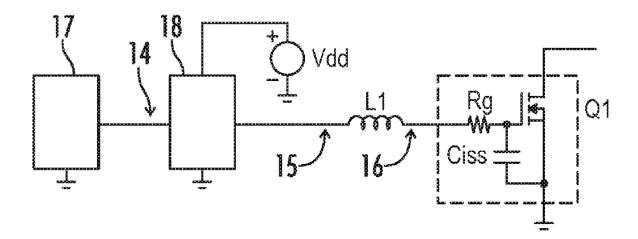

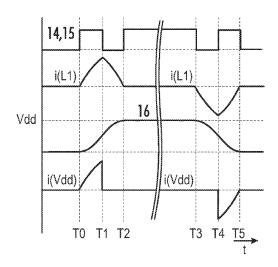

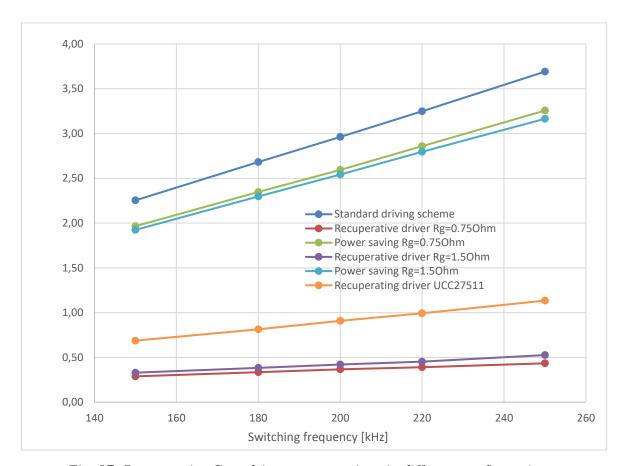

| Fig. | 93: Recuperative Gate driver for high current synchronous rectifier                                                                                                                                                 |

| Fig. | 94: Recuperative Gate driver control diagram                                                                                                                                                                        |

| Fig. | 95: Scope snapshot of recuperative gate driver during operation (left), Detuning effect of Miller capacitance (right)                                                                                               |

| Fig. | 96: Obvious difference in gate driver efficiency – conventional (left) and recuperative driver solution (right)                                                                                                     |

| Fig. | 97: Recuperative Gate driver power savings in different configuration                                                                                                                                               |

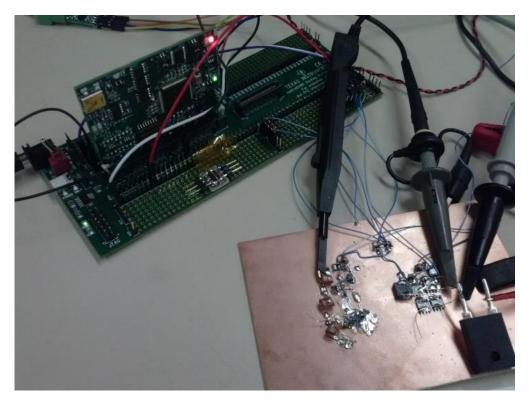

| Fig. | 98: Evaluation of recuperative gate driver                                                                                                                                                                          |

# DEPARTMENT OF POWER ELECTRICAL AND ELECTRONIC ENGINEERING Faculty of Electrical Engineering and Communication Brno University of Technology

### **LIST OF TABLES**

| Table 1: Part numbers and catalogue $R_{DSon}$ of tested samples        | .44 |

|-------------------------------------------------------------------------|-----|

| Table 2: 80plus efficiency limits, 80plus titanium applicable from 2026 | .47 |

| Table 3: Available GaN parts suitable for 3kW PFC                       | .48 |

#### **INTRODUCTION**

After years of evolution and domination on the power electronics market, the Silicon semiconductors are reaching their physical limit, which opens space for the new technologies. In the last few years, amount of available GaN switching devices for power electronic applications has significantly increased. The number of emerging devices with a different internal structure has a growing tendency. Devices are offered not only by small/startup companies but also by well-known manufacturers of semiconductors (Infineon, Panasonic). The higher bandgap of Gallium Nitride (3.4eV) material offers potentially higher operating temperatures, fast switching capability and therefore generates less power loss than widely used Silicon or SiC devices.

Fig. 1: Theoretical limits of Si, SiC and GaN material, [7]

GaN Transistors are well-known from low voltage, high frequency (MHz, GHz Range) applications (RF amplifiers in cell phones, *consumer* electronics, and many more). Improved manufacturing technology allows to use GaN in power electronics, which sets a brand-new benchmark in power converters' parameters. Nowadays markets provide relatively narrow portfolio of GaN devices with 600V rating focused on power supply applications (consumer electronics, server and telecom applications...). First transistors with 1200V rating exist too, which makes them usable in electric drives and automotive applications. General requirements on power conversion systems are moving to smaller, higher dense solutions (60-100W/inch³) to reduce the overall size of the system and overall cost of the power supply.

In following chapters the structure and parameters of currently available GaN transistor part numbers will be described. As the manufacturers are choosing different way how to proceed in the development of new devices in terms of internal semiconductor structure, closer look will be taken onto analysis of those structures with intention to compare.

MOSFET Gate driving principles are well known in power electronics. With new absolute maximum ratings for Gallium Nitride semiconductors, new challenges and possibilities are being introduced into design. This thesis aims to analyze and name these problems, with intention to propose solutions applicable to power converters design for various applications with GaN.

Roadmap in packages development is leading into size minimized packages, designed for surface mount technology. This style of packaging fixes problem with gate driving and improves switching performance of the device, on the other hand makes cooling design of the power chip challenging. Finite element method simulations together with measurement on prototypes of printed circuit boards designed for high performance cooling of small packages, which give a reference for industrial designs, are included.

Introduction of innovative devices, with brand new production technology and semiconductor structure should have different qualification process, comparing to settled Silicon MOSFETs used nowadays. The reason is simple, new phenomena might be present and might affect device performance in different operating conditions, which are not included in qualification process for semiconductors nowadays. This might affect long term reliability, which poses a high risk for pioneers introducing new technology into their commercial products. One of these phenomena is dynamic on-channel resistance, varying with time and various conditions. Analysis of this particular problem and collection of results measured on existing, commercially available samples, is one of base topics of this thesis.

Main result of this thesis is supposed to be the application of gained knowledge into prototype of DC/DC converter using Gallium Nitride devices, optimized for high efficiency and high-power density. This converter is operated as power factor correction in totem pole configuration with output power 3kW at output voltage 400V. Results show real benefits of this new technology, with immediate introduction into industrial application possible.

Study and analysis of certain topics related to GaN in this thesis, resulted in potential application of integrated circuit used primarily for this technology in different field. Penultimate chapter shows example of recuperative gate driver for silicon MOSFETs in synchronous rectifier for high efficiency resonant converter. This shows, that using novel/high-speed integrated circuit originally designed for GaN transistors, might bring significant improvements in various electronic problem categories.

#### 1 Present Gan Technology overview

Nearly every manufacturer on the market is presenting his own GaN technology, with a different internal structure on a semiconductor level and with different performance. Internal structures of the transistors promoted for a usage in power electronics are - Cascode (Transphorm, VisIC), Enhanced mode (GaN systems, EPC) and Gate insulated transistors (Panasonic, Infineon). Different internal structures have different levels of complexity of the chip and different driving requirements. As per documentation of the aforementioned manufacturers, it is clear, that current common production technology is creating GaN structures on a silicon wafer. This technology is borrowed from manufacturers of optoelectronic components (LED, low wavelength lasers), where it has a long tradition and provides a good start point for GaN development. In this sector, two major companies (Veeco U.S., Aixtron Germany) are well known, providing automated solutions for manufacturing of GaN on Si structures.

#### 1.1 D-mode GaN

The basic GaN HFET (Heterostructure Field Effect Transistors) functional structure is grown on the silicon substrate with thin layer of Aluminum Nitride (Fig. 2), in some sources this type of transistor is also called depletion or d-mode transistor. As in every power Field Effect Transistor, there are Gate, Source and Drain contacts. Due the Gate electrode placed on the top of the AlGaN, we need to apply negative voltage bias on Gate-Source to turn the device OFF. This is caused by Schottky contact on the top of the surface, which becomes reverse biased by negative voltage and the electrons underneath are depleted. This device is "normally ON".

Fig. 2: Depletion mode GaN transistor structure, [7]

In power conversion applications this device obviously could not be used. The negative bias voltage on Gate-Source contact must be present before the power bus voltage. This may be hard to achieve in many applications and can result in driver circuit complexity, which affects the system reliability. To make GaN transistor useful in real application, manufacturers were forced to deal with the mentioned problem by developing new structures while maintaining the performance.

#### 1.2 E-mode GaN

GaN Systems, EPC works with enhancement mode field effect transistor (FET) structure. Basic enhanced mode manufacturing process starts with silicon wafers with thin aluminum layer (AlN) growth on it. This thin layer allows the growth of gallium nitride heterostructures (AlGaN) and creation of the whole transistor structure. The result is the structure shown on picture below, which is similar to silicon metal oxide semiconductor FET (MOSFET) with some exceptions. To enhance this FET, positive voltage must be applied between Gate and Source contact, same as in standard power MOSFET transistor.

Fig. 3: Enhanced mode GaN transistor structure, [7]

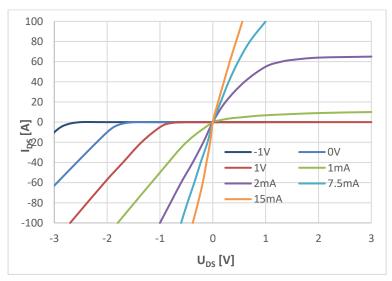

With voltage present on the gate electrode, device can operate in two quadrants (forward and reverse current), with voltage drop equivalent to product of channel resistance in open state and drain-source current. Important difference between Si MOSFET and the GaN is the absence of natural body diode, which was causing serious problem with its reverse recovery charge in hard-switched topologies. In reverse mode (U<sub>GS</sub>=0 V), the voltage drop is defined by the channel resistance in reverse mode plus voltage on fictive inner diode, the forward voltage of which is the same as the one of the gate threshold voltage (1.1-1.5 V) (the situation is properly described in Fig. 4). In case of reverse conduction with negative bias on Gate electrode (U<sub>GS</sub><0 V), this diode voltage is increased to the value of negative bias. This will result in significantly increased conduction losses in reverse operation mode. As it will be further described in Chapter 3, due to the low gate threshold voltage and the impossibility of operation in reverse mode, special requirements are needed for gate driver loop impedance.

Absence of diode reverse recovery charge known from silicon MOSFETs in thousands of nano-coulombs (nC), has only decreased on few dozens of nC, while this effect was caused by capacitive charge of semiconductor junction capacitance. This fact together with reduced Coss capacitance brings theoretical assumptions to operate at higher frequency with low switching losses also in hard-switched topologies.

Fig. 4: Enhanced mode GaN output characteristics

#### 1.3 GaN Cascode

Transphorm, ON Semi, VisIC are developing the cascode GaN transistors. Cascode is combination of low voltage fast silicon transistor (typically N-MOSFET) with "normally ON" GaN transistor (d-mode) connected as in picture below.

Fig. 5: GaN Cascode power transistor

Main benefit of the GaN cascode is the higher Gate-Source threshold voltage (3-4.5 V) – as the gate drive parameters are defined by silicon MOSFET in "bottom" part. GaN cascode can conduct reverse/forward current with voltage present on the Si MOSFET Gate electrode (Fig. 6, case a. and b.). Voltage drop is then defined by the forward current and the sum of the low voltage Si MOSFET and the depletion mode GaN channel ON resistance. In reverse operation mode with no voltage on Gate ( $U_{GS}$ =0V) the current is flowing through intrinsic body diode of silicon MOSFET and depletion mode GaN transistor – reverse voltage is then equal to reverse body diode voltage plus product of reverse resistance of d-mode transistor and flowing current (Fig. 6, case c.). There is no difference between reverse conduction with zero gate voltage, and negative bias on gate electrode ( $U_{GS}$ <0V) – using negative Gate voltage during device driving is possible, but has no effect on an overall drain-source performance.

Fig. 6: GaN Cascode operating modes

Accurate control of drain voltage slope during turn-on and turn-off is not possible with Cascode structure. By changing Gate resistance, the control of du<sub>DS</sub>/dt is only possible in limited extent. Output characteristic of GaN transistor is the conjunction of two independent output characteristic of low voltage Si MOSFET and d-mode GaN, and correlation between them. Example of the cascode output characteristic is on picture below, where sharp edge around Si MOSFET Gate threshold voltage can be seen.

Fig. 7: GaN Cascode output characteristics

Israel manufacturer VisIC is promoting GaN cascode with the best parameters at the time in terms of on-state resistance (22 m $\Omega$ ), outstanding peak forward (180A) and reverse current capability in 650V class of transistors. This manufacturer also provides first GaN 1200V 40m $\Omega$  cascode transistor. Disadvantage of cascode devices is a need of two chips in one device (d-mode GaN and Silicon MOSFET), which can influence reliability and have negative price impact.

#### 1.4 Gate injection transistor

GIT transistor promoted by Panasonic, Infineon is normally off transistor based on high electron mobility principle, similar as d-mode using two-dimensional electron gas forming at an AlGaN-GaN layer. The transistor is being produced in the same way as the other structures on silicon substrate, with a buffer layer to allow reliable creation of GaN structures.

Fig. 8: Gate injection transistor structure, [7]

Same as e-mode transistor, GIT is forced to conducting state by increasing gate-source voltage above threshold voltage, typically around 1-1.3V. Major difference between e-mode and GIT is the on state behavior of Gate – while e-mode acts similarly to unipolar MOSFET transistor, GIT is above threshold voltage acting as a diode (P type Gate), therefore requires on state current (typically dozens of mA) which is defining the on state channel resistance of the Drain-Source. Thanks to the diode behavior in the on-state is gate electrode rugged (up to the current rating) against high dv/dt transients on drain-source. As transistor does not have a parasitic body diode, the current is flowing in reverse conduction mode through the channel – reverse drain-source voltage is dependent on gate-source voltage, minimum corresponding with the threshold voltage and increasing with a negative gate bias. The transistor therefore acts as a combination of bipolar transistor (in forward mode) and e-mode unipolar transistor (in reverse mode). As the reverse current is conducted over the channel, the reverse recovery charge minimized – key feature of GaN technology.

Fig. 9: GIT transistor output characteristics

#### 1.5 Absence of avalanche mode

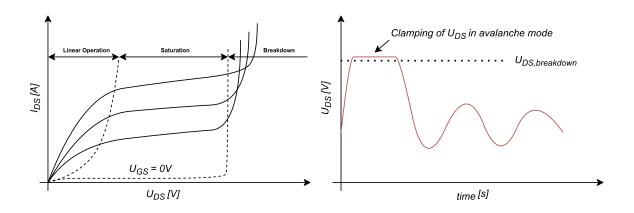

In general, high electron mobility GaN transistor does not have an avalanche mode, or in other words, nondestructive breakdown in overvoltage. Avalanche mode means ability to clamp voltage above certain drain-source voltage in non-conducting state, known from MOSFET devices. MOSFET breakdown of the channel is nondestructive up to certain time defined by robustness/thermal capacity of the chip and operating conditions (specified avalanche energy). The transistor typically enters this mode during switching in high current condition (FAULT) and not well designed, highly inductive layout. Up to some extent, this behavior might be considered as a self-protection of device in circuit.

Fig. 10: Output characteristics and Avalanche mode of MOSFET

Applying the same conditions on GaN transistor will result in failure. Exceeding the voltage rating is in case of GaN wide bandgap devices (WBG) leading to immediate channel breakdown, although this voltage is from practical experiences much higher, than rated voltage. Manufacturers claim that devices are able to withstand transients 20-40% above specified rating. Therefore, for reliable operation it is not recommended to use any type of GaNs in topologies, which principally allows overvoltage in case of control circuit failure (e.g. single switch flyback). Non inductive layout with proper drain-source rating check in all operating conditions is mandatory, to avoid random failures during product lifetime.

Another aspect of the overvoltage effect on GaN is reduction of mean time to failure. This problem is well described in JEDEC JEP180 (Global Standards for the Microelectronics industry) where part of the qualification includes lifecycle testing with elevated drain-source voltage in combination with temperature.

#### 2 THESIS GOALS

### 1.) Study of Gate driver requirements analysis of nowadays available GaN semiconductors

With rise of novel technology, several different structures of Gallium Nitride power chip exist. While some of the parts are manufacturers developing based on combination of two independent chips in one package, others are investing effort into advanced single chip solutions, with different layout and production technologies. Different principle of operation means different parameters and requirements for driving and its application in power converter, which is a target of the analysis.

## 2.) Design and optimization of innovative cooling solutions for minimized surface mount packages, used for novel GaN devices

Voltage driving levels and fast switching performance of the GaN high electron mobility transistor are a motion for packaging style change, as large lead packages are no longer suitable and are limiting the performance of a chip. Goal of this chapter is to develop innovative solutions for cooling of minimized surface mount packages without constraints related to increased inductance of input terminals.

### 3.) Characterization of dynamic $R_{dson}$ problem related to certain production technologies

Based on published articles of different authors, electron trapping under Gate contact of high electron mobility transistor exists. As this misbehavior might significantly affect performance of switch in final application, further analysis and characterization of this problem is crucial. Special experimental test setup is being built, and test results will be compared.

# 4.) Application of gained sub-results in practical case of innovative DC/DC power converter and its optimization for high efficiency while maintaining high power density

Multiple of partial improvements gained within this thesis are being verified in totem pole power factor correction converter. Detailed steps of optimization for high efficiency at certain operating conditions are explained, to comply with 80plus certification required by the European Union regulations for computer and server appliances. Goal of this section is to present gained results with all the improvements applied.

#### 5.) Application of novel GaN integrated circuits in various applications

Evolution in production of Gallium Nitride based semiconductors results in development of novel integrated circuit, capable of parameters never seen before. This chapter shows application of integrated driving circuit in special application of recuperative Gate driver of high Current synchronous rectifier in resonant converter, resulting in US patent.

# 3 STUDY OF GATE DRIVER CONSIDERATIONS FOR VARIOUS TECHNOLOGIES

Successful implementation of GaN transistors into power conversion topology requires reliable driver circuit, while fulfilling requirements of driven chip. As mentioned in previous chapter, gate structures of available transistors are different in terms of construction, therefore various requirements for the driver design exist.

#### 3.1 Overcurrent protection by Driver

The saturation protection known from the IGBT driver technology is in theory possible with every transistor as with rising current across the conducting channel, at some point, voltage starts to rise too. To gain maximum reliability, it would be nice to construct driver of the device, which is able to protect the device in case of short circuit. Detectable voltage increase over the channel will appear for available GaN transistors only at high current, exceeding the peak rating of the device. In addition, during short circuit we can assume full voltage of the voltage bus across the device. Power loss is in this condition extreme, comparing to transistor parameters. To prevent the thermal failure, protection circuit must act in range of nano-seconds, which is nowadays not possible to achieve – when using circuit which consists from available integrated circuits placed on printed circuit board.

In terms of protection, innovative solution is presented by Texas Instruments LMG3410 device, where the driver of the power transistor is integrated together with overcurrent, overtemperature protection in single package. Manufacturer claims, that this protection is capable of acting in 20ns range and is able to protect device in case of low ohmic short at input. This part foresees a future of integrated driver on chip, and shows its impressive possibilities.

#### 3.2 Voltage transient immunity requirements – CMTI

Fast transients from on to off state and vice versa are the key benefit of GaN semiconductors, leading to improved efficiency of power converter. In most of the power electronic topologies is the base stone half-bridge, where top side switch is "floating" and requires isolation against power ground. Assuming high dv/dt across this isolation barrier, any capacitance of the driver against ground is resulting in significant currents, being pushed over kelvin node of driven device, which might lead to false turn-on and oscillations. Low inter- winding capacitance of supply path for floating driver (transformer) is necessary.

As the GaN might be considered with designs operating at high frequency, deadtimes need to be optimized up to last nano-second, gate command signal is transferred typically by digital isolator with very low propagation delay (light or planar transformer principle). The path of the control signal isolation must be designed to withstand fast transient voltage – common mode transient immunity (CMTI) must be higher than expected dv/dt in designed application. High performance digital signal insulators are providing  $100-150kV/\mu S$  (TI's ISO78XX) and are already on the limit comparing to GaNs switching performance. Further development is necessary.

#### **3.3** E-mode

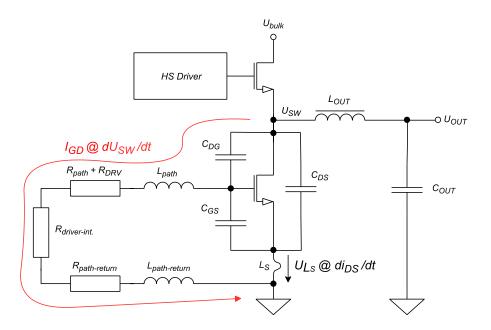

High electron mobility, enhancement mode transistor can be in terms of control compared to a silicon unipolar transistor. Major difference to commonly used MOSFETs is lower Gate threshold voltage (typ. 1.3V, Miller Plateau 3.0V) and different behavior in reverse conduction. With intention to minimize switching losses, it is important to speed up the transitions from on to off state and vice versa. With high di/dt in drain source path the voltage on common driving inductance (gate-source loop) is easily reaching threshold voltage, which can lead into positive voltage present on Gate electrode.

Transistor is exposed to voltage transient  $du_{DS}/dt$  at conduction state change of opposite device in half bridge configuration. While the voltage is rising steeply, inductance in driving path act as a high impedance element. Gate is charged via miller capacitance and channel might become open. Voltage transients might be caused by external events, like input surge of power supply. In this state driver should keep gate electrode shorted to kelvin contact with low impedance during normal operation and even if it's not powered, which is not true for many nowadays available integrated drivers. Mentioned parasitic elements are further explained in the picture below – transients might lead into cross conduction in half bridge topologies, which with high probability will result in permanent damage.

Fig. 11: E-mode Gate Driving circuit with parasitic elements

Gate charge ( $C_{GD}$ ) is for WBG transistors significantly smaller; therefore, the driving is faster and efficient. Drain-Gate capacitance ( $C_{DG}$ ) is present, and pushes current ( $I_{GD}$ ) to gate during high dv/dt transients on drain. As the e-mode transistors have typically low absolute maximum voltage rating for a Gate electrode (max. 7V), long term reliability might be affected if spikes are present on Gate drive loop impedance. Stability of driving voltage over temperature and time is necessary, typically a precise linear regulator is used. Another major difference to the Silicon MOSFET drivers is undervoltage lockout, which is for most of the commercially available GaN drivers set to 4V. Usage of high current capable gate driver compatible with e-mode voltage driving levels is recommended (e.g. UCC27511 from Texas Instruments).

Common inductance in driving path is problem which does not allow to use lead packages for driving devices anymore and explains why properly designed GaN power chips are packaged into size optimized surface mount packages with kelvin node connection. While one problem is fixed by proper packaging, gate loop impedance is fully in hands of the designer. Design techniques for low inductive layout should be applied.

#### **3.4 GIT**

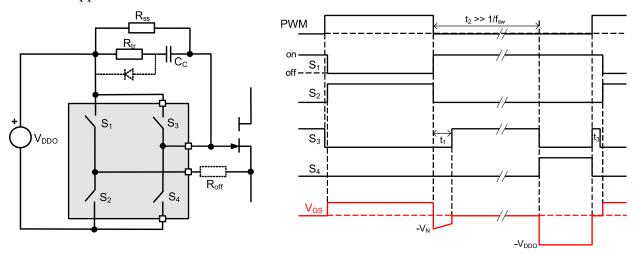

For best switching performance of a Gate Injection Transistor it is important to provide positive/negative current pulse (3-7 times higher than steady state gate current) during turn-on/off. From test experiences and manufacturers documentation, the higher the current peak is, the faster is the transition. Channel resistance in conducting state is defined by Gate current (20-50mA), disadvantage is additional power loss in the driver, as it is acting as linear regulator with small output voltage while transistor is conducting. Same as for e-mode transistors, the gate threshold voltage is small but requires certain power to activate as the input can be represented by diode (from Gate do Source) - ruggedness against false trigger is higher when compared to e-mode technology. To avoid device false turn on during voltage transient on drain-source it is recommended to keep gate voltage negative. As generation of positive and negative pulses together with precise steady state current limitation are relative complex for embedded solution, the manufacturers are providing integrated circuit fulfilling requirements of specific power chip (e.g. 1EDF5673 + IGO60R070D1). Integrated driver uses H-bridge configuration and external ceramic capacitors to generate positive and negative current pulse, set by series resistors (picture below). Negative bias for driver is not needed, as it is equipped with capacitive charge pump. From operation of the driver it is clear, that isolated power supply from power ground of the transistor must be used in any case, as the driver is reversing the bias voltage. This might be considered as complication with cost impact for budget sensitive applications. Transistor is sold together with the driver, no second sourcing is possible – solution is strongly dependent on designer relationship with the supplier.

Fig. 12: Proper GIT driver with control diagram, [1EDF5673 Datasheet]

Negative Gate bias voltage can be present during whole off state of switching period, or can be present only temporarily (Fig. 12, time  $t_1$ ), during switch on/off of opposite transistor in a half-bridge – time of the deadtime + maximum length of transition. "Negative bias time" is - according to datasheet of existing parts - programmed by external resistor, which is convenient. In terms of PCB layout, same recommendations are applied for GIT, as described for e-mode.

#### 3.5 Cascode

GaN cascode power transistor - from driving requirements point of view - is basically the same as silicon MOSFET (typ. +/- 20V max. from Transphorm specification), as only low voltage normally off MOSFET is driven and controlling the d-mode GaN in internal structure. One of the major advantages is high peak voltage rating for Gate, which makes cascode most rugged GaN technology. Total gate charge is significantly smaller, comparing to silicon transistor with same drain source capability. From cascode internal structure it can be seen, that drain-source voltage dv/dt can be controlled over gate drive only in limited range, which is acceptable.

Fig. 13: Cascode Gate Driving circuit with parasitic elements

Thanks to the series combination of low voltage MOSFET and d-mode GaN, is the Coss higher and more nonlinear at low voltages, comparing to other GaN transistor structures, which has negative impact on switching performance and control complexity in resonant converters.

Same packaging style and driving levels allow the use of GaN cascode as a substitution in existing designs of power converters, which might improve efficiency parameters without significant redesigning effort.

### 4 COOLING OF MINIMIZED SURFACE MOUNT PACKAGES

Reducing parasitic elements is leading to size minimized, surface mount packages. On the one hand improved switching performance helps to reduce power loss of the device, on the other hand it makes cooling of the device much more challenging. Comparing to standard lead packages (TO-220, TO-247), which were in most of the cases directly attached to the heatsink over insulating thermal interface. With minimized surface mount packages it is necessary to design more sophisticated structure, in special case as a part of the printed circuit board itself. If we take a look at the current portfolio of GaN devices available on the market, we can split it into two groups -TOP and BOTTOM cooled surface mount packages. Several manufacturers are designing semiconductors packages in a mirrorable way, only shape of electrical connections is defining cooling requirements (for example Infineon's PDSO package). Both solutions provide pros and cons, which will be analyzed in this chapter.

#### 4.1 Top side cooling

For a package where a cooling plate is located on the top side (opposite to soldering pads), the heatsink is a part of the PCB assembly, or the opposite way, the PCB is mounted to the heatsink. Problem seems too obvious and easy to resolve. But, for long term reliability in certain pollution degree (2-3) it must be taken into account, that for high voltage (typical bus voltage 400V DC) the creepage and clearance distance defined by IPC9595 are relatively high (>3mm), comparing to device size itself. This distance must be maintained between all electrical poles, mechanical fixings of the heatsink to the PCB tracks and connectors. To get stable results in production, tolerances of package dimensions same as soldering process itself need to be considered as well. Mechanical assembly to support heatsink mounted to the PCB requires at the end bigger area than needed by cooled component itself – benefit of the possibly high-power density disappears. In any cases, heat is transferred over the thermal conductive material directly to heatsink. If the heatsink is galvanically connected with a cooling pad, highly conducting material can be used as a gap filler. For this configuration the top side cooling is the most efficient way – nearly no temperature difference on Cooling Pad-Heatsink thermal resistance.

Fig. 14: Top side cooling mechanical construction

VisIC company producing GaN Cascodes is promoting very special hybrid package, most probably with military background, which has insulated cooling pad from other contacts of the device (part number V22TC65S1A). Manufacturer claims that part provides basic isolation up to 2.5kV which might bring significant benefits for Top cooling approach. Disadvantage is a package height (approx. 3mm), which is not compliant with IPC9592 recommended distances for advertised isolation voltage level.

#### 4.2 Bottom side cooling

Second group of devices is manufactured with bottom side cooling pad, on the same side as electrical connection. Heat transfer is performed over PCB to the heatsink attached over thermal interface/foil on opposite side of the device. Mechanical interface is in this case not needed, PCB is assembled in simple single sided SMT assembly process and afterwards assembled over sticky/insulating interface to the heatsink. Bottom side solution is possible, in case the thermal resistance over the PCB thickness is minimized to acceptable value – power loss of the cooled device will create temperature rise, which together with temperature of the heatsink (ambient temperature) have to stay below maximum ratings of the chip.

Fig. 15: Bottom side cooling mechanical construction

Heat transfer over PCB can be done over base/core material and over tracks and vias – copper part. In case of standard printed circuit board made from FR4 the core contribution to cooling is very low (0,35Wm<sup>-1</sup>K<sup>-1</sup>). On the opposite side is the ceramic material base - Aluminium Nitride ceramic (140Wm<sup>-1</sup>K<sup>-1</sup>), which has other disadvantages as brittleness, cost and only single layer PCB is supported by manufacturers. In case of low thermal conductivity of core material the right strategy is to bridge the PCB by conductive material and add additional insulating layer, which can provide fixing of the PCB to the heatsink at the same time (e.g. Sticky foil Arlon Secure 1500KT2). Thermal conductivity for a thermally conductive and electrically insulating foil (functional insulation, at least 30kV/mm) is in high performance material reaching 3Wm<sup>-1</sup>K<sup>-1</sup>, which is hardly comparable with non-insulating phase changing materials or thermal conductive pastes. Contribution of layers and vias to the cooling is mainly in Z direction, but can be extended to heat distribution in planar (X, Y) direction too, which increases area of heat transfer over insulating interface with lower thermal conductivity. In high frequency switching applications one has to keep the capacitance of cooling pad to the ground in mind (typ. Heatsink), as it is affecting device performance and adding switching losses, described in Chapter 3. Therefore, increase of cooling pad area is possible only in limited extent.

All of these assumptions can be considered as a start point for a successful cooling design and are based on well-known formula:

$$R_{\vartheta} = \frac{1}{\lambda} \cdot \frac{l}{S} \tag{1}$$

In following lines, several bottom side cooling solutions will be presented, using different printed circuit board manufacturing techniques with their performance evaluation.

#### 4.3 PCB with copper inlays

Using standard core material FR4 should be the target for all designs, as the technology of PCB manufacturing on fiberglass is well developed and cost effective. Therefore, we are looking for a way how to create area of higher thermal conductivity from top side of the PCB to the bottom, to the isolating thermal interface/heatsink. These requirements are well fulfilled by Copper inlay technology - which is a copper element protruded over pre-milled opening in standard, several layer PCB. This design style is ideal for carrying high currents over PCB, seen in automotive applications nowadays, but ideally fits for this case, as the copper is a good heat conductor (400Wm<sup>-1</sup>K<sup>-1</sup>).

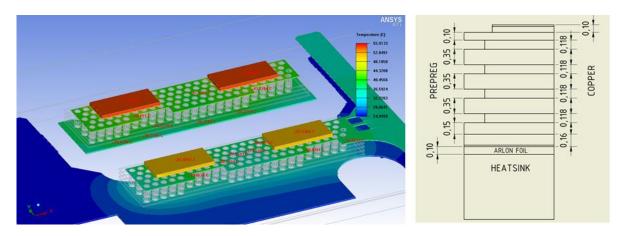

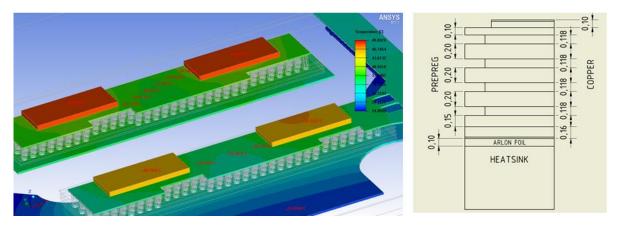

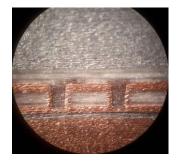

Before proceeding to prototype phase and testing, solution is to be verified by Finite Element Method simulation in ANSYS ICEPAK. In simulated case the cooled surface mount device is directly soldered to the copper inlay and the heat is transferred through the foil (Arlon Secure 1500KT2) to the heatsink over copper block. Simulated model contains layers of FR4 and bottom copper pour, with intention to spread heat in X/Y direction – increase area of heat transfer over isolating interface. Simulation result is displayed in picture below, FR4 layers are turned off for better visibility (Fig. 31). Power losses assigned to the four devices are 20W, assuming two transistors in parallel in a half bridge application (5W for every transistor chip). Ambient temperature is 25 °C, overall temperature increase is 23 °C – including isolation between heatsink and device thermal resistance between chip and case.

Fig. 16: Copper inlay thermal simulation

Improving of heat flow over insulating interface is possible by increasing copper on bottom layer, which is in contact with insulating foil. As the copper is good thermally conductive material, the heat will "travel" more far away from copper inlay, therefore lower temperature increase is expected. Situation can be analyzed by formula for thermal resistance, modified for situation of two electrodes on thermally isolated metal plate with concentrated power loss:

$$R_{\vartheta A-B} = \frac{1}{2.\pi.\lambda_{Cu}.d}.\ln\frac{r_B}{r_A}$$

(2)

Where  $\lambda_{Cu}$  is thermal resistivity of copper and  $r_a$  and  $r_b$  are radius of two virtual electrodes in certain distance from centralized power loss. As the surface is not fully isolated, but surrounded by thermal conductive material, exponential drop of temperature with rising distance from edge of the copper inlay is expected:

$$\Delta T(r) = T_M \cdot e^{-\frac{r}{r_0}} \tag{3}$$

Where r is certain distance from copper inlay,  $T_M$  is temperature increase at the edge of copper inlay vs. ambient and constant  $r_0$  is defined as:

$$r_0 = \sqrt{\frac{\lambda_{Cu} \cdot d}{\alpha}} \tag{4}$$

And means a distance, where the temperature drops to 1/e of its original value. In formula the thickness of copper is - d (approx.  $70\mu m$ ) and  $\alpha$  is a heat transfer coefficient, depended on surrounding materials. As the copper is in this case surrounded by FR4 from one side and high voltage insulating foil from the other side, estimation of this coefficient is complex. From FEM simulation results it (Fig. 16) is assumed, that distance  $r_0$  where temperature drops to half of original value is approximately 3mm. Therefore, it does not make sense to enlarge bottom copper pour over this value, as there is a negative effect of increased capacitance of switching node to the heatsink, described in details in Chapter 2.

Overall  $\Delta \vartheta$  from surface of printed circuit board to the heatsink temperature is  $12.3^{\circ}C$  – thermal resistance is calculated with power 10W is  $R_{\vartheta} = 1.23$  KW<sup>-1</sup>. Majority of the temperature increase is on the thermal insulating foil, while PCB is bridged with temperature difference  $5.4^{\circ}C$  ( $R_{\vartheta PCB} = 0.54$  KW<sup>-1</sup>). This result shows major disadvantage - high tech PCB technology used, but overall performance is lost on high voltage insulating layer. Simulated case and tested prototype are representing primary power stage of 3kW resonant converter (LLC). Prototype using copper inlay technology was produced, and results were evaluated (Fig. 23). Power losses assigned to the four devices are 20W (5W for every transistor chip) – same situation as ICEPAK simulation on previous page. Heatsink temperature is  $30.8^{\circ}C$ , PCB surface temperature is  $39.3^{\circ}C$ , resulting in thermal resistance from PCB surface to the heatsink side  $R_{\vartheta PCB} = 0.85$  KW<sup>-1</sup> (without insulating foil).

Measured increase is worse on prototype comparing to simulation, which might be explained by measurement error (different emissivity of materials) together with temperature increase on thermal conducting paste, which was used to attach bear PCB to the heatsink. Experiment was conducted without foil, as pressure during application of insulating foil is hard to control, variances of Arlon material properties and PCB by itself are present. Some of the produced prototypes were randomly showing significantly higher thermal resistance, which was caused by air bubbles, trapped in foil during application. Root cause of this problem seems to be copper inlay production tolerance (flatness of area), as the PCB production process contains materials with different height – copper shape and FR4 thickness defined by pressure during lamination of layers. This phenomenon can lead to problems in mass production, and potential unit failure by insufficient cooling of power semiconductor.

#### 4.4 PCB with thermal vias

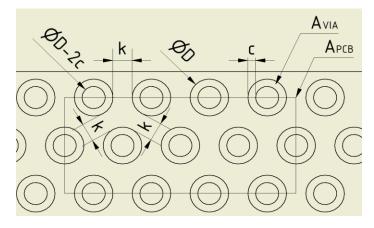

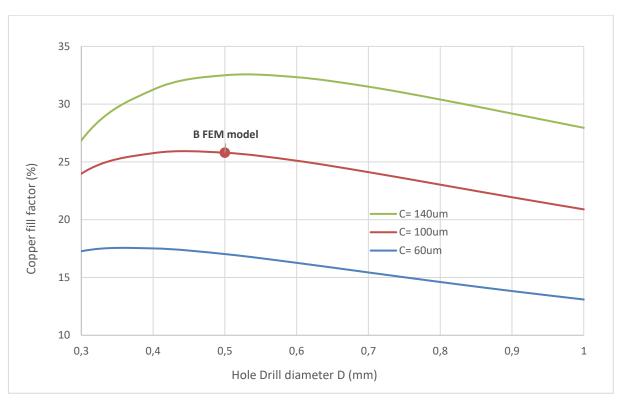

Alternate solution to copper inlays is the PCB with high amount of vias, with an intention to transfer heat efficiently to the heatsink. Design and effectivity of this solutions are hardly dependent on printed circuit board manufacturer capabilities – especially maximum hole/via plating thickness (Fig. 17 - c), distance between drilled holes (Fig. 17 - k) and the hole diameter itself (Fig. 17 - D). Considering dimensions displayed in the drawing below (Fig. 17) - for lowest thermal resistance of the PCB in Z direction, highest area of copper should be achieved (1). Triangular organization of vias is using manufacturing capabilities in the most effective way. Comparing to frequently seen square pattern [18][26], brings triangular pattern 15.5% more copper vs. area ratio, which is directly reflected in performance. By comparing area of the "useful" copper transferring heat to the total PCB area, following formula can be constructed (5). Derivation (=0) of this equation shows the optimum for a defined via plating thickness and drilled hole distance, which is feasible by standard manufacturing process – point A and B displayed in Fig. 19 and Fig. 18. As centralized power losses are expected (transistor assembled on PCB), thickness of top layer is not negligible, as it is distributing heat in X/Y axis and making vias on a side effectively contributing to heat transfer.

Fig. 17: Copper fill factor

Fig. 18: Plot of copper fill factor for three different via wall plating thicknesses, k = 0.25mm

Fig. 19: Plot of copper fill factor for three different drill hole distances,  $c = 100 \mu m$

Ratio between the area of thermal conducting copper versus total PCB area:

$$\frac{A_{Cu}}{A_{PCB}} = \frac{8 x A_{VIA}}{A_{PCB}} = \frac{2 \cdot \pi \cdot (D \cdot c - c^2)}{\sqrt{3} \cdot (D + k)^2}$$

(5)

If the thickness of the top layer is sufficient (>50µm) and parameter k is in optimal range, the thermal resistance of across PCB can be calculated using following formula:

$$R_{\vartheta} = \frac{1}{\lambda_{Cu}} \cdot \frac{l_Z}{N \cdot \pi \cdot (D \cdot c - c^2)} \tag{6}$$

Where N is the total amount of vias in cooled area,  $l_z$  is the overall PCB thickness – the vias length.

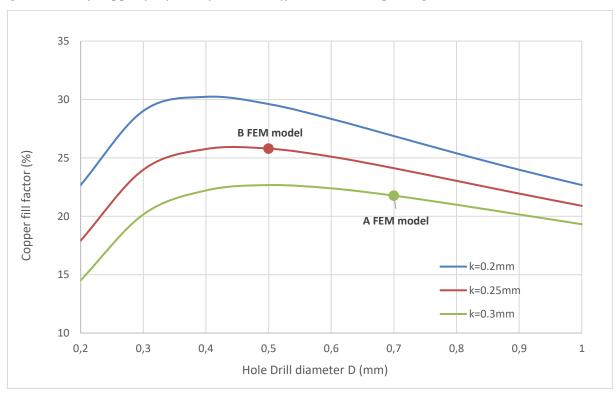

Same as for copper inlays, development started with thermal simulation of solution in ICEPAK. Simulation of model requires significant amount of mesh elements and computation power. Certain simplification had to be taken to make simulation possible – vias as a "barrel shape" were replaced by simple hexagons. Conductivity of material for simplified vias was recalculated over area of new hexagon and parameters of "real via" and its smaller than conduction of electroplated copper. Extra care was taken to make sure, that the mesh settings are set optimally and that the mesh follows the surface of objects (Fig. 20). "Mesh leak" - Overlapping of mesh assigned to object with low thermal conductivity (e.g. insulation foil) with copper element might lead to incorrect results.

Fig. 20: High resolution mesh of simulated thermal vias

For simplification of the model special software was used, as manual replacement of vias by hexagonal shape can take a while. Raw data for simulation have been exported in ODB format, and brought to 3D by Artwork NETEX and 3DVu, which makes the job easy. After these operations it is necessary to clean model from small objects and objects which are not necessary for simulation.