# VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

BRNO UNIVERSITY OF TECHNOLOGY

FAKULTA INFORMAČNÍCH TECHNOLOGIÍ ÚSTAV POČÍTAČOVÝCH SYSTÉMŮ

FACULTY OF INFORMATION TECHNOLOGY DEPARTMENT OF COMPUTER SYSTEMS

NEW METHODS FOR INCREASING EFFICIENCY AND SPEED OF FUNCTIONAL VERIFICATION

DIZERTAČNÍ PRÁCE

PHD THESIS

AUTOR PRÁCE AUTHOR

Ing. MARCELA ŠIMKOVÁ

**BRNO 2015**

# VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

BRNO UNIVERSITY OF TECHNOLOGY

# FAKULTA INFORMAČNÍCH TECHNOLOGIÍ ÚSTAV POČÍTAČOVÝCH SYSTÉMŮ

FACULTY OF INFORMATION TECHNOLOGY DEPARTMENT OF COMPUTER SYSTEMS

# METODY AKCELERACE VERIFIKACE LOGICKÝCH OBVODŮ

NEW METHODS FOR INCREASING EFFICIENCY AND SPEED OF FUNCTIONAL VERIFICATION

DIZERTAČNÍ PRÁCE

PHD THESIS

AUTOR PRÁCE

Ing. MARCELA ŠIMKOVÁ

AUTHOR

VEDOUCÍ PRÁCE

Doc. Ing. ZDENĚK KOTÁSEK, CSc.

SUPERVISOR

**BRNO 2015**

### **Abstrakt**

Při vývoji současných číslicových systémů, např. vestavěných systému a počítačového hardware, je nutné hledat postupy, jak zvýšit jejich spolehlivost. Jednou z možností je zvyšování efektivity a rychlosti verifikačních procesů, které se provádějí v raných fázích návrhu. V této dizertační práci se pozornost věnuje verifikačnímu přístupu s názvem funkční verifikace. Je identifikováno několik výzev a problému týkajících se efektivity a rychlosti funkční verifikace a ty jsou následně řešeny v cílech dizertační práce. První cíl se zaměřuje na redukci simulačního času v průběhu verifikace komplexních systémů. Důvodem je, že simulace inherentně paralelního hardwarového systému trvá velmi dlouho v porovnání s během v skutečném hardware. Je proto navrhnuta optimalizační technika, která umisťuje verifikovaný systém do FPGA akcelerátoru, zatím co část verifikačního prostředí stále běží v simulaci. Tímto přemístěním je možné výrazně zredukovat simulační režii. Druhý cíl se zabývá ručně připravovanými verifikačními prostředími, která představují výrazné omezení ve verifikační produktivitě. Tato režie však není nutná, protože většina verifikačních prostředí má velice podobnou strukturu, jelikož využívají komponenty standardních verifikačních metodik. Tyto komponenty se jen upravují s ohledem na verifikovaný systém. Proto druhá optimalizační technika analyzuje popis systému na vyšší úrovni abstrakce a automatizuje tvorbu verifikačních prostředí tím, že je automaticky generuje z tohoto vysoko-úrovňového popisu. Třetí cíl zkoumá, jak je možné docílit úplnost verifikace pomocí inteligentní automatizace. Úplnost verifikace se typicky měří pomocí různých metrik pokrytí a verifikace je ukončena, když je dosažena právě vysoká úroveň pokrytí. Proto je navržena třetí optimalizační technika, která řídí generování vstupů pro verifikovaný systém tak, aby tyto vstupy aktivovali současně co nejvíc bodů pokrytí a aby byla rychlost konvergence k maximálnímu pokrytí co nejvyšší. Jako hlavní optimalizační prostředek se používá genetický algoritmus, který je přizpůsoben pro funkční verifikaci a jeho parametry jsou vyladěny pro tuto doménu. Běží na pozadí verifikačního procesu, analyzuje dosažené pokrytí a na základě toho dynamicky upravuje omezující podmínky pro generátor vstupů. Tyto podmínky jsou reprezentovány pravděpodobnostmi, které určují výběr vhodných hodnot ze vstupní domény. Čtvrtý cíl diskutuje, zda je možné znovu použít vstupy z funkční verifikace pro účely regresního testování a optimalizovat je tak, aby byla rychlost testování co nejvyšší. Ve funkční verifikaci je totiž běžné, že vstupy jsou značně redundantní, jelikož jsou produkovány generátorem. Pro regresní testy ale tato redundance není potřebná a proto může být eliminována. Zároveň je ale nutné dbát na to, aby úroveň pokrytí dosáhnutá optimalizovanou sadou byla stejná, jako u té původní. Čtvrtá optimalizační technika toto reflektuje a opět používá genetický algoritmus jako optimalizační prostředek. Tentokrát ale není integrován do procesu verifikace, ale je použit až po její ukončení. Velmi rychle odstraňuje redundanci z původní sady vstupů a výsledná doba simulace je tak značně optimalizována.

### Klíčová slova

Funční verifikace, verifikace založená na simulaci, Universal Verification Methodology, System-Verilog, optimalizace, automatizace, genetický algoritmus, verifikace řízená pokrytím, metriky pokrytí.

### Citace

Marcela Šimková: New Methods for Increasing Efficiency and Speed of Functional Verification [dizertační práce], Ústav počítačových systémů FIT VUT v Brně, Brno, CZ, 2015

### **Abstract**

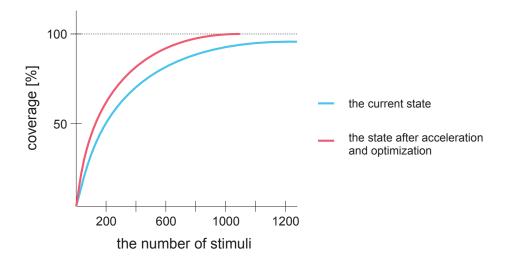

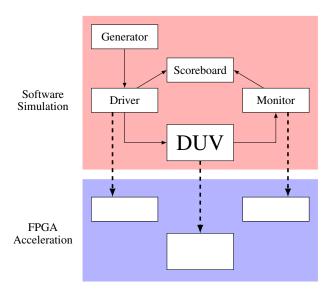

In the development of current hardware systems, e.g. embedded systems or computer hardware, new ways how to increase their reliability are highly investigated. One way how to tackle the issue of reliability is to increase the efficiency and the speed of verification processes that are performed in the early phases of the design cycle. In this Ph.D. thesis, the attention is focused on the verification approach called *functional verification*. Several challenges and problems connected with the efficiency and the speed of functional verification are identified and reflected in the goals of the Ph.D. thesis. The first goal focuses on the reduction of the simulation runtime when verifying complex hardware systems. The reason is that the simulation of inherently parallel hardware systems is very slow in comparison to the speed of real hardware. The optimization technique is proposed that moves the verified system into the FPGA acceleration board while the rest of the verification environment runs in simulation. By this single move, the simulation overhead can be significantly reduced. The second goal deals with manually written verification environments which represent a huge bottleneck in the verification productivity. However, it is not reasonable, because almost all verification environments have the same structure as they utilize libraries of basic components from the standard verification methodologies. They are only adjusted to the system that is verified. Therefore, the second optimization technique takes the high-level specification of the system and then automatically generates a comprehensive verification environment for this system. The third goal elaborates how the completeness of the verification process can be achieved using the intelligent automation. The completeness is measured by different coverage metrics and the verification is usually ended when a satisfying level of coverage is achieved. Therefore, the third optimization technique drives generation of input stimuli in order to activate multiple coverage points in the verified system and to enhance the overall coverage rate. As the main optimization tool the genetic algorithm is used, which is adopted for the functional verification purposes and its parameters are well-tuned for this domain. It is running in the background of the verification process, it analyses the coverage and it dynamically changes constraints of the stimuli generator. Constraints are represented by the probabilities using which particular values from the input domain are selected. The fourth goal discusses the re-usability of verification stimuli for regression testing and how these stimuli can be further optimized in order to speed-up the testing. It is quite common in verification that until a satisfying level of coverage is achieved, many redundant stimuli are evaluated as they are produced by pseudo-random generators. However, when creating optimal regression suites, redundancy is not needed anymore and can be removed. At the same time, it is important to retain the same level of coverage in order to check all the key properties of the system. The fourth optimization technique is also based on the genetic algorithm, but it is not integrated into the verification process but works offline after the verification is ended. It removes the redundancy from the original suite of stimuli very fast and effectively so the resulting verification runtime of the regression suite is significantly improved.

# **Keywords**

Functional verification, simulation-based verification, Universal Verification Methodology, SystemVerilog, optimization, automation, genetic algorithm, coverage-driven verification, coverage metrics.

# **Bibliographic Citation**

Marcela Šimková: New Methods for Increasing Efficiency and Speed of Functional Verification, Ph.D. thesis, Department of Computer Systems FIT BUT, Brno, CZ, 2015

## Prohlášení

Prohlašuji, že jsem tuto dizertační práci vypracovala samostatně pod vedením svého školitele Doc. Ing. Zdeňka Kotáska, CSc., a že jsem uvedla všechny literární prameny, ze kterých jsem v průběhu své práce čerpala.

Marcela Šimková 14. září 2015

## Poděkování

Děkuji všem, kteří mi byli oporou při sepisování této práce a byli mi cennými rádci v průběhu celého mého studia. Jmenovitě děkuji mému školiteli, panu Doc. Zdeňkovi Kotáskovi za vedení. Děkuji mému budoucímu manželovi Michalovi za lásku, podporu a povzbuzení. Také děkuji Ondrějovi Lengálovi, Michalovi Kajanovi a Liborovi Polčákovi za výběr tématu diplomové práce, který mně nasměroval i k tématu dizertační práce a za všechny jejich rady a čas, který mi věnovali. Děkuji mým kolegům z UPSY a z Codasipu, kteří se mnou spolupracovali.

© Marcela Šimková, 2015.

Tato práce vznikla jako školní dílo na Vysokém učení technickém v Brně, Fakultě informačních technologií. Práce je chráněna autorským zákonem a její užití bez udělení oprávnění autorem je nezákonné, s výjimkou zákonem definovaných případů.

# **Contents**

| 1 | Intr | oduction                                         |

|---|------|--------------------------------------------------|

|   | 1.1  | Motivation                                       |

|   | 1.2  | Problem Statement                                |

|   | 1.3  | Thesis Contribution                              |

|   | 1.4  | Thesis Organization                              |

| 2 | Veri | fication Approaches                              |

|   | 2.1  | Brief History of Design and Verification Methods |

|   | 2.2  | Current Verification Approaches                  |

|   | 2.3  | RTL Verification                                 |

|   |      | 2.3.1 Logic Simulation and Testing               |

|   |      | 2.3.2 Static Analysis and Formal Verification    |

|   |      | 2.3.3 Functional Verification                    |

| 3 | Fun  | ctional Verification in SystemVerilog            |

|   | 3.1  | Verification Process                             |

|   |      | 3.1.1 Specification and Requirements             |

|   |      | 3.1.2 Verification Plan                          |

|   |      | 3.1.3 Building Testbench                         |

|   |      | 3.1.4 Writing Verification Tests                 |

|   |      | 3.1.5 Analysis of Coverage                       |

|   | 3.2  | Verification Methodologies                       |

|   | 3.3  | Chapter Overview                                 |

| 4 | Evol | lutionary Computing                              |

|   | 4.1  | Main Principles of Evolutionary Computing        |

|   | 4.2  | Brief History                                    |

|   | 4.3  | Main Components of Evolutionary Algorithms       |

|   |      | 4.3.1 Representation (Definition of Individuals) |

|   |      | 4.3.2 Evaluation Function (Fitness Function)     |

|   |      | 4.3.3 Population                                 |

|   |      | 4.3.4 Parent Selection Mechanism                 |

|   |      | 4.3.5 Variation Operators                        |

|   |      | 4.3.6 Survivor Selection Mechanism (Replacement) |

|   |      | 4.3.7 Initialization                             |

|   |      | 4.3.8 Termination Condition                      |

|   | 4.4  | Evolutionary Computing and Global Optimization   |

|   | 4.5  | Genetic Algorithms                               |

|   | 4.6        | Parameter Control in Genetic Algorithms                                             | 38 |

|---|------------|-------------------------------------------------------------------------------------|----|

|   | 4.7        | Chapter Overview                                                                    | 39 |

| 5 | Fun        | ctional Verification State-of-the-art and Related Work                              | 40 |

|   | 5.1        | Conferences and Published Work                                                      | 40 |

|   | 5.2        | Related Work                                                                        | 42 |

|   |            | 5.2.1 Acceleration of RTL Simulation using FPGA Accelerators and Emulators .        | 42 |

|   |            | 5.2.2 Automated Generation and Reuse of Verification Environments and IPs           | 44 |

|   |            | 5.2.3 Coverage Improvement Techniques                                               | 45 |

|   |            | 5.2.4 Building Effective Regression Suites                                          | 47 |

|   | 5.3        | Chapter Overview                                                                    | 47 |

| 6 | Goa        | ds of the Ph.D. Thesis                                                              | 48 |

| U | 6.1        | Expected Theoretical Results                                                        | 48 |

|   | 0.1        | Expected Theoretical Results                                                        | 70 |

| 7 |            | GA-based Acceleration of Functional Verification                                    | 50 |

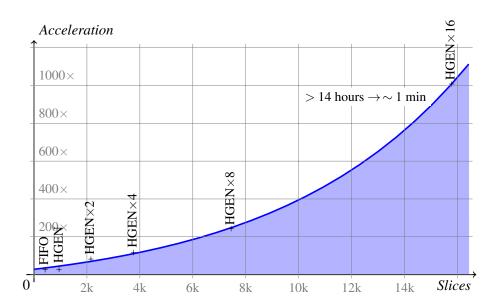

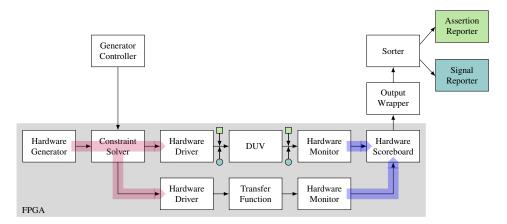

|   | 7.1        | First Version of HAVEN                                                              | 50 |

|   |            | 7.1.1 Design of Acceleration Framework                                              | 50 |

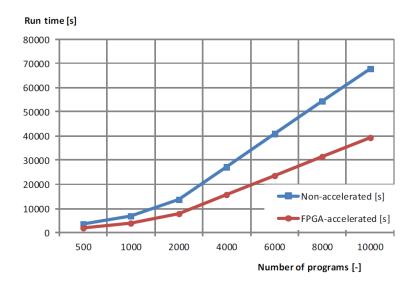

|   |            | 7.1.2 Experimental Results                                                          | 55 |

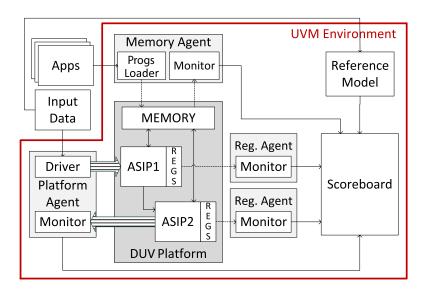

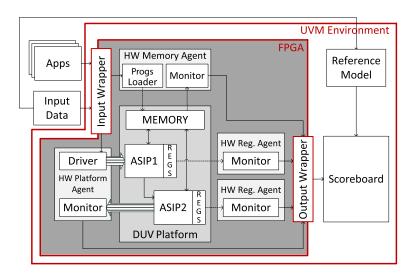

|   | 7.2        | Second Version of HAVEN                                                             | 59 |

|   |            | 7.2.1 Design of Acceleration Framework                                              | 60 |

|   |            | 7.2.2 Testbed Architectures of HAVEN                                                | 61 |

|   |            | 7.2.3 Experimental Results                                                          | 62 |

|   | 7.3        | Use-cases of HAVEN                                                                  | 63 |

|   |            | 7.3.1 FPGA Prototyping and Accelerated Verification of ASIPs                        | 63 |

|   | 7.4        | Evaluation Platform for Testing Fault-Tolerance Methodologies in Electro-mechanical |    |

|   |            | Applications                                                                        | 66 |

|   | 7.5        | Main Contributions of HAVEN                                                         | 69 |

| 8 | Auto       | omated Generation of UVM Verification Environments                                  | 70 |

|   | 8.1        | Codasip Studio                                                                      | 70 |

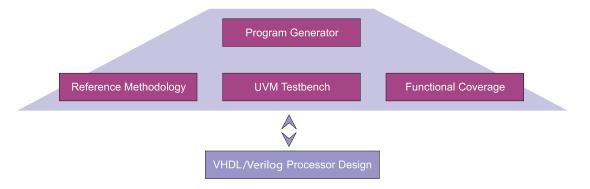

|   | 8.2        | Functional Verification Environments for Processors                                 | 71 |

|   | 8.3        | Experimental Results                                                                | 73 |

|   | 8.4        | Main Contributions of Automated Generation                                          | 74 |

| 9 | Anta       | omation and Optimization of Coverage-driven Verification                            | 75 |

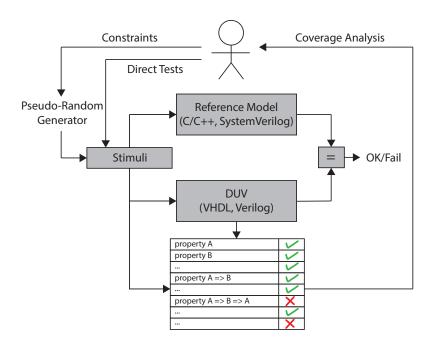

|   | 9.1        | Manual CDV                                                                          | 75 |

|   | 9.2        | Automated CDV                                                                       | 75 |

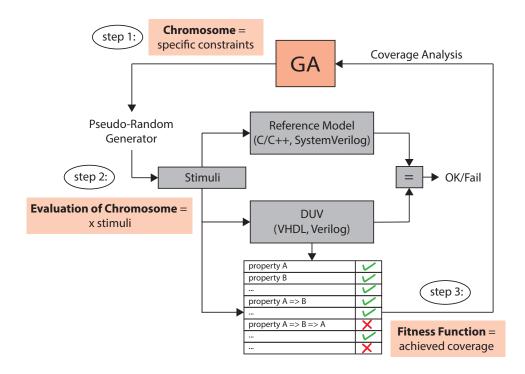

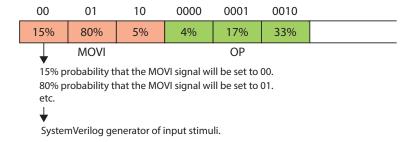

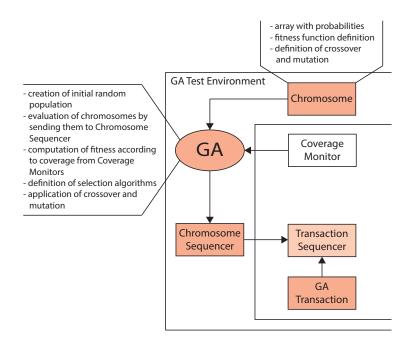

|   | 7.2        | 9.2.1 Automated CDV Driven by Genetic Algorithm                                     | 76 |

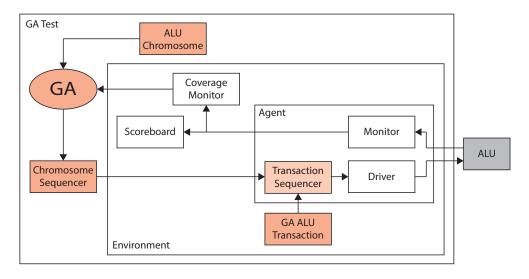

|   | 9.3        | Integration into UVM                                                                | 78 |

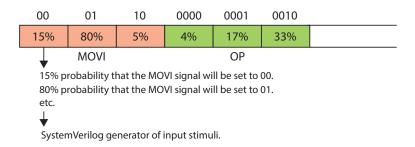

|   | 9.3<br>9.4 | Tuning Parameters                                                                   | 79 |

|   | 9.4        | Experimental Results                                                                | 81 |

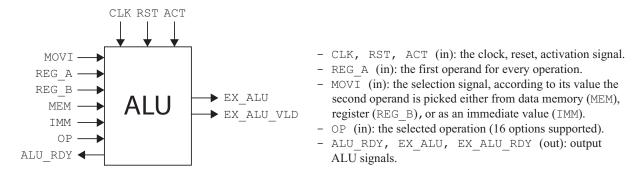

|   | 7.3        | 9.5.1 Arithmetic-logic Unit                                                         | 81 |

|   |            | <u> </u>                                                                            | 84 |

|   | 0.6        |                                                                                     |    |

|   | 9.6        | Main Contributions of GA Automation and Optimization                                | 88 |

| 10 | Optimization of Regression Suites                         | 89  |  |  |  |

|----|-----------------------------------------------------------|-----|--|--|--|

|    | 10.1 Optimization Problem                                 | 89  |  |  |  |

|    | 10.2 Evolutionary Optimization of Regression Test Suites  | 90  |  |  |  |

|    | 10.2.1 Core of the Optimization Technique                 | 90  |  |  |  |

|    | 10.2.2 GA Parameters                                      | 94  |  |  |  |

|    | 10.3 Experimental Results - ALU Case Study                | 94  |  |  |  |

|    | 10.4 Main Contributions of Regression Suites Optimization |     |  |  |  |

| 11 | Conclusions                                               |     |  |  |  |

|    | 11.1 Future Work                                          | 98  |  |  |  |

| 12 |                                                           | 100 |  |  |  |

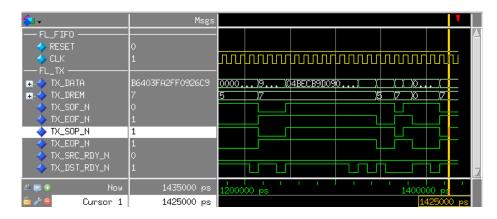

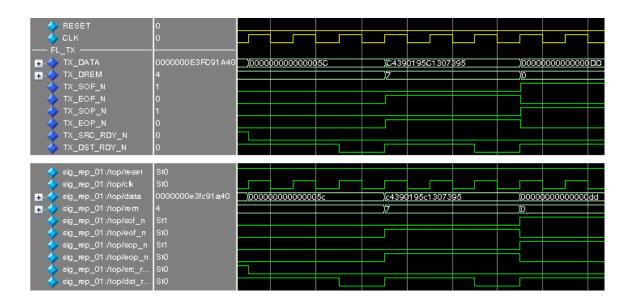

|    | 12.1 FrameLink                                            | 100 |  |  |  |

| 13 | Appendix B                                                | 101 |  |  |  |

|    | 13.1 Publications and Products                            | 101 |  |  |  |

|    | 13.2 Research Projects and Grants                         | 103 |  |  |  |

# **Acronyms**

ABV Assertion-Based Verification. 18

ALU Arithmetic-Logic Unit. 82

ASIC Application-Specific Integrated Circuit. 7

ASIPs Application Specific Instruction-set Processors. 44, 71

**BDDs** Binary Decision Diagrams. 46

CDV Coverage-Driven Verification. 18, 76

CTL Computation Tree Logic. 12

**DPI** Direct Programming Interface. 18

**DRC** Design Rule Checking. 13

**DUV** Design Under Verification. 7

**EA** Evolutionary Algorithms. 28

EC Evolutionary Computing. 28

FIFO First In First Out. 55

**FPGA** Field Programmable Gate Array. 7

**FSM** Finite State Machine. 45

GA Genetic Algorithm. 28, 37, 77

GPPs General Purpose Processors. 44

HDLs Hardware Description Languages. 11

**HGEN** Hash Generator. 55

HVLs Hardware Verification Languages. 11

IC Integrated Circuit. 12

IoT Internet of Things. 44

LLVM Low Level Virtual Machine. 71

LTL Linear Temporal Logic. 12

LVS Layout Versus Schematic. 13

MPSoCs Multi-Processor Systems-on-Chip. 44

NFL No Free Lunch. 37

**OOP** Object-Oriented Programming. 17

**OVM** Open Verification Methodology. 8, 26

PSL Property Specification Language. 18

**RTL** Register-Transfer Level. 11

SoCs Systems-on-Chip. 44

**SVA** SystemVerilog Assertions. 18

UVM Universal Verification Methodology. 8, 26

VCD Value Change Dump. 53

VMM Verification Methodology Manual. 25

# Chapter 1

# Introduction

## 1.1 Motivation

Computer systems play nowadays very important role in human everyday lives. They are everywhere and they help people in many ways: they assist them in their working lives, they help them in their households and they even entertain them. To cover these tasks perfectly, the most important property of these systems is their correctness with respect to their specification (i.e. ensuring that they do not behave in a faulty way). However, the complexity of modern computer systems is rising rapidly so achieving high degree of correctness is a difficult challenge. The discipline dealing with this issue is called *verification*.

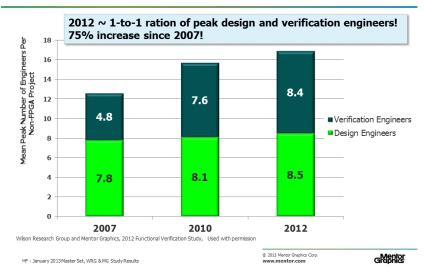

According to The 2012 Wilson Research Group Functional Verification Study [37], which is a blind study supported by Mentor Graphics and conducted regularly by Wilson Research Group, verification became a very important part in the development of computer systems, as the ratio of the design and verification engineers is almost 1:1 and increased by 75 % since 2007 (see Figure 1.1).

# **Effort and Results** *Mean peak number of design vs. verification engineer trends*

Figure 1.1: Source: The 2012 Wilson Research Group Functional Verification Study: The mean peak number of design vs. verification engineer trends.

For verification of computer hardware, a variety of options is available to engineers: (i) simulation and testing, (ii) functional verification, and (iii) formal analysis and verification.

Although simulation and testing might be seen as old-fashioned methods, they are still highly effective especially in the early phase of implementation and debugging of base system functions. The benefits of testing real hardware (either in the form of an Application-Specific Integrated Circuit (ASIC) or a configuration of a Field Programmable Gate Array (FPGA)) is the speed of testing (as it is performed in real time) and also the possibility to cover faults arising from the technology used for physical implementation of the logical circuit. Software simulation of hardware allows the developer to check that base system functions conform to system specification even before the circuit is physically assembled. This aspect plays more and more important role nowadays when the physical implementation of the systems into hardware is becoming critically expensive.

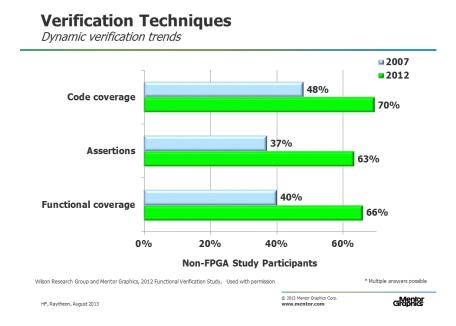

Functional verification can be seen as a more efficient approach to verification of systems before they are taped-out. This approach is based on simulation of the environment of the system, of the system itself being called a Design Under Verification (DUV), and uses *coverage-driven verification*, *constrained-random stimulus generation*, *assertion-based verification*, and other techniques to check the system correctness and maximize the efficiency of the overall verification process. The adaptation of functional verification techniques is illustrated in Figure 1.2.

Figure 1.2: Source: The 2012 Wilson Research Group Functional Verification Study: Dynamic Verification Trends.

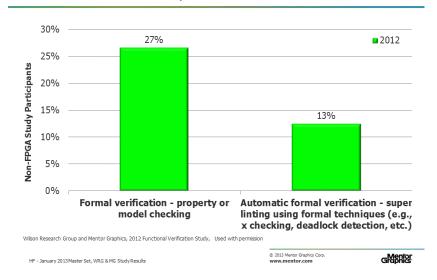

In order to achieve *completeness* (i.e. a certainty that the system does not violate its specification) of the process of verification, some formal techniques and tools can be used. They are adequate for detecting errors in highly concurrent and complex designs where traditional ways mentioned before are not sufficient. The adaptation of formal verification techniques is depicted in Figure 1.3.

As can be seen, a lot of different verification approaches with their own advantages and disadvantages exist. However, it is worth deciding carefully which of them is suitable for a specific scenario. Therefore, one of the goals of this thesis is to analyze and compare existing techniques for verification of hardware circuits and provide a simple guideline for verification engineers.

### **Verification Techniques**

Static verification technique trends

Figure 1.3: Source: The 2012 Wilson Research Group Functional Verification Study: Static Verification Techniques Trends.

#### 1.2 Problem Statement

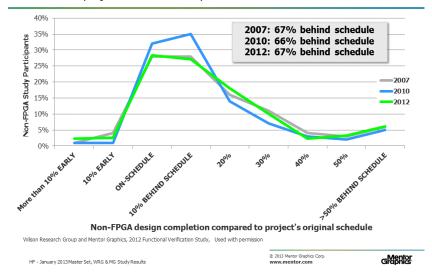

Today's highly competitive market of consumer electronics is very sensitive to the time it takes to introduce a new product (the so-called *time to market*). Figure 1.4 illustrates how many participants of the Wilson Research Group Functional Verification Study can handle the original time schedule of their projects. Unfortunately, it can be seen that for several years the trend is stable, around 67 % of projects are behind the schedule.

This has driven the demand for fast, efficient and cost-effective methods of verification of hardware systems. They must tackle several challenges:

- defining the appropriate metrics to measure the progress in verification,

- restricting the time needed to discover a next error,

- restricting the time to isolate and resolve the error,

- creating sufficient tests to verify the whole design and manage the verification process.

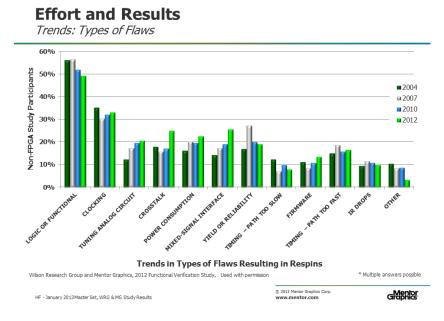

In Figure 1.5, the overview of errors that are most commonly discovered by verification is illustrated. It can be seen that logic and functional errors take the biggest portion of them, but the good news is that they can be effectively handled by pre-silicon verification approaches.

#### 1.3 Thesis Contribution

We decided to focus our research on functional verification as it is extensively used in industry nowadays. It utilizes sophisticated programming languages for hardware verification, such as SystemVerilog [1], and standardized verification methodologies (e.g. Open Verification Methodology (OVM) [31], Universal Verification Methodology (UVM) [69]).

### **Effort and Results**

Non-FPGA project's schedule completion trends

Figure 1.4: Source: The 2012 Wilson Research Group Functional Verification Study: Project's Schedule Completion Trends.

Figure 1.5: Source: The 2012 Wilson Research Group Functional Verification Study: Types of flaws.

In the thesis, every of the challenges mentioned in Section 1.2 is taken into account. It is believed that the main contributions of this thesis are as follows.

• Various coverage metrics are discussed, how they capture design specifications and functionalities and how they allow to measure the progress in verification. It is outlined, how the functional coverage points (monitors) must be defined as it is quite tricky and a non-trivial

problem.

- The bottleneck concerning generation of suitable stimuli for the DUV that can adequately

activate all coverage points and achieve high coverage rate is also targeted in the thesis. An

optimization technique is proposed that works in the background of the verification process

and automatically without the human intervention drives generation of stimuli so the uncovered properties of the system are checked.

- The time bottleneck is eliminated by accelerating functional verification runs in the FPGA

accelerator and by automated generation of verification environments with respect to the

UVM methodology.

- The verification process must be successfully managed also in the later phases of the development of hardware systems, when the functionality is slightly modified or some optimizations to the design are made. Therefore, an optimization technique is proposed that helps to create small but coverage-effective regression suites from the stimuli already used in functional verification.

## 1.4 Thesis Organization

The text of the thesis is divided into thirteen chapters. Chapter 2 introduces the history of techniques and tools for hardware design and verification. The history overview is followed by theoretical principles of widely used verification approaches: simulation and testing, functional verification and formal verification. Chapter 3 describes the functional verification in more details as well as the SystemVerilog language, its features and steps to build effective and reusable verification environments. Chapter 4 describes evolutionary computing, especially the genetic algorithm, its parameters and applications in practice. The reason for mentioning evolutionary computing and algorithms is that the genetic algorithm is used as the main optimization tool in the techniques proposed in this thesis. Chapter 5 discusses the functional verification state-of-the-art and the available related work in the field of optimization of functional verification. Many literature and research papers are examined and evaluated. In Chapter 6, the main goals of this Ph.D. thesis are outlined. With respect to these goals, four chapters follow, each of them is devoted to one optimization technique that is uniquely proposed in this thesis and targets one of the goals. A detailed description of each technique is included as well as the experimental work. The first optimization technique in Chapter 7 targets acceleration of functional verification using the FPGA technology. The optimization technique presented in Chapter 8 automates generation of the UVM-based verification environments. In Chapter 9, automation and optimization of coverage-driven verification is described. The optimization technique used in this chapter utilizes the genetic algorithm as the main optimization tool. Also in the optimization technique proposed in Chapter 10 the genetic algorithm is used, but this time for finding optimal regression suites that are built from stimuli used in functional verification. Chapter 11 summarizes the work and outlines its possible further enhancements. Finally, Chapters 12 and 13 contain additional information related to the thesis, mainly the list of author's publications and research projects.

# Chapter 2

# **Verification Approaches**

The discipline dealing with checking whether a hardware system satisfies a given correctness specification is called *verification*. The main purpose of verification is to find as many design errors as possible before the system is deployed or even produced. This chapter presents the history of various design and verification techniques in the last four decades and also verification approaches that are currently mostly used at different stages of the hardware development. Furthermore, the Register-Transfer Level (RTL) verification approaches are presented in more details because they are used to discover most of the functional and logical errors in the pre-silicon debugging. Moreover, a simple comparison of these approaches is included, so the verification engineers can get an opinion which of them is suitable for specific verification issues and scenarios.

## 2.1 Brief History of Design and Verification Methods

Over the years, as technology progressed and the complexity of hardware designs increased, new verification methods were needed and developed. During the last 40 years many advanced and effective techniques and tools for verification appeared (the history overview is taken from [19]).

In the 70's, hardware was designed by drawing schematics on the paper, later electronically, but verification was mainly performed by detailed review of the schematics. During the 80's, simulation tools became popular, but they were predominantly proprietary. Testbenches were hard to build with non-standardized tools, and verification relied on manual assessment of simulation results. In 1987, VHDL became a standard and Hardware Description Languages (HDLs) were generally accepted as means of design and verification. *Static verification tools* also started to emerge around this time in order to help in static analysis determining whether designs conform to design rules. As the density of designs increased, the use of more intelligent testbenches became a common practice. Self-checking testbenches with direct testing were then followed by testbenches that used *constrained-random stimulus generation* and finally *transaction-based* testbenches. The implementation of advanced testbenches along with the introduction of better tools (coverage checkers, faster RTL simulators) increased rapidly the popularity of simulation. However, as designs became even more complex, HDLs of that time were not sufficient for effective verification, since only very restricted functions and data types could be defined.

To overcome these deficiencies, Hardware Verification Languages (HVLs) were introduced. These HVLs were tailored for simulation and integration with HDLs. HVLs introduced the concept of *functional coverage* and helped in tracking the progress of verification. Evolution of verification methodologies and languages led towards standardization of the SystemVerilog language (its current standard being IEEE 1800-2009 [1]).

Assertion-based verification is a concept originally introduced in the scope of formal (static) verification. This approach uses a simple language based on a temporal logic (such as Linear Temporal Logic (LTL) or Computation Tree Logic (CTL)) to describe specifications of parts of a system in the form of a set of temporal formula. In the case of formal verification tools, the state space of the system is then exhaustively searched to check whether all specified temporal formula are valid in all accessible states of the verified system. In case a state that invalidates some formula is found, a counter-example (also called a witness) is provided in the form of a waveform of a sequence of input and internal signals that leads to the failing state. In case of dynamic verification tools, in each clock cycle of the simulation all formulas are checked for validity and in the case of a failure the simulation is stopped with an error message.

# 2.2 Current Verification Approaches

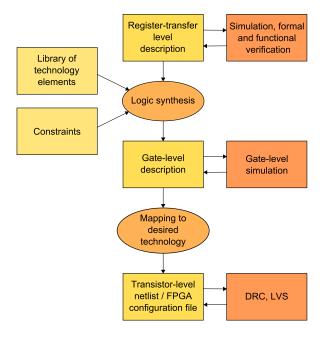

With the growing complexity of hardware systems, verification became a bottleneck in the development cycle and therefore, it was and still is typically divided into several stages. Every representation of the system at varying levels of abstraction (register-transfer level, gate-level, hardware-level) should be verified independently as is depicted in Figure 2.1 and described in the following text.

Figure 2.1: Verification stages.

- RTL is a design abstraction level which models a synchronous digital circuit in terms of the flow of digital signals (data) between hardware registers and the logical operations performed on those signals. RTL represents a high-level description of a circuit and is implemented in HDLs like VHDL, Verilog, SystemC, or SystemVerilog. At this level, several verification approaches running in RTL simulators can be applied, with *logic simulation*, *static analysis*, *model checking* and *functional verification* being the most popular.

- Gate-level netlist is a description of a circuit which is derived from the RTL representation in the process of logic synthesis. During the logic synthesis, a library of logic elements of a given technology (Integrated Circuit (IC), ASIC, FPGA) and user constraints for timing,

power or area are considered. Among techniques that are used for verification of gate-level netlist belongs the *gate-level simulation*.

• Hardware-level description can be represented by the transistor-level netlist for IC/ASIC or by the bitstream configuration file for FPGAs. These descriptions are created by specific tools while utilizing concrete physical elements of a target technology. In the case of FPGAs, logic elements are mapped and placed onto physical FPGA elements and interconnections are built in the process of routing. Similar steps are performed in case of ICs/ASICs and as a result, specific physical layout is created. For the verification purposes, Design Rule Checking (DRC) or Layout Versus Schematic (LVS) techniques can be utilized.

Except of the design faults, many defects can arise during the production phase. Therefore, a few techniques have been developed in order to allow the application of manufacturing tests. They are labeled as *Design for Test* and in most cases they insert some specific logic into a tested circuit in order to explore and test all important parts of the circuit properly.

### 2.3 RTL Verification

Verification approaches working at the behavioral level or register-transfer level of abstraction typically use the HDL description of a circuit for the construction of the simulation model (in the case of the simulation-based approaches), the mathematical model (in the case of the formal approaches) or they simply work only with the source code (in the case of the static analysis). They are described thoroughly in the following subsections.

#### 2.3.1 Logic Simulation and Testing

Logic simulation and testing are often called bug hunting methods as their main purpose is to find as many errors as possible in a hardware design during the early (pre-silicon) stages of the development cycle.

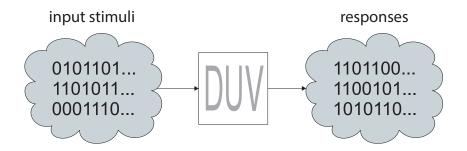

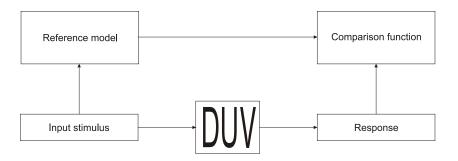

A designer typically prepares a simple testbench with a sample of input stimuli and manually checks responses of the system to these stimuli in RTL simulation. This scenario is demonstrated in Figure 2.2. In such a way, a designer can check basic system functions properly. However, the overall behavior can be explored only in a limited number of situations (because of the non-complex testbench). Therefore, the logic simulation provides only a *partial* guarantee of the system correctness.

One of the main strengths of simulations is that software simulators working at the RTL level provide a perfect debugging environment with many functions. All signals of the simulated design are readily accessible. Once an error has been reproduced in this environment, the process of debugging can be performed extremely efficiently. For this reason, it is convenient to have the capability of executing the same tests in order to reproduce the failing scenarios.

The disadvantage of simulation is its low performance which directly depends on the complexity of the simulated design. The reason is that processes are running one after another in the simulator, while in a real hardware, the are running concurrently. Practically, simulation is so computationally intensive that it can take days or even weeks to simulate a large design. For this reason, detailed software simulation can be often performed only on small portions of a complex design and cannot be interconnected to real hardware environment [59].

Figure 2.2: A simple testbench architecture.

#### 2.3.2 Static Analysis and Formal Verification

Static Analysis is an approach with a high level of automation. Static analysis tries to avoid execution of the system being examined by analyzing its source code instead. It also gathers some approximate information about the system from its source code. Various forms of static analysis exist, like type analysis, bug pattern searching, equational data-flow analysis, constrained-based analysis, and abstract interpretation. Static analysis is not exclusively intended for checking correctness of systems only, it is used also for optimization, code generation, etc. The main advantages are that it can handle very large systems and does not need a model of the environment of a system. However, it can produce many false alarms and various analysis are specialized just for certain specific tasks.

Formal verification is an approach based on an exhaustive exploration of the state space of a system, hence it is potentially able to formally prove the correctness of the given system according to its specification. Formal methods are mainly based on formal mathematical roots. As the task of formal verification is in general undecidable, formal verification methods may not guarantee termination. A typical reason is the so called state space explosion problem for the real-world systems. Some methods deal with the issue of termination using abstraction through upper-approximation which may in turn introduce false alarms. Alternatively, a method is allowed to stop with a don't know answer or it may become not fully automated (some human intervention is required). If the formal verification run of a system fails, it may be still useful as it can find some errors in the meantime. Another disadvantage is the need to provide formal specifications of the behavior of the system, which makes this approach often hard to use.

There are several distinct verification techniques used in the formal field. The most important and the best known are described here:

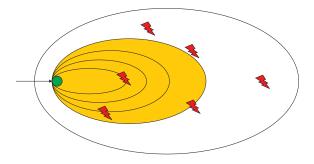

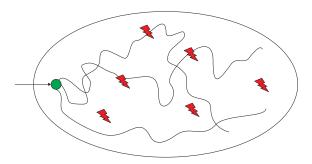

• Model checking is an algorithmic approach of checking whether a given system satisfies a given property through systematic exploration of the state space of the system. This principle is illustrated in Figure 2.3 where the green circle represents the initial state, yellow circles the progress in the state space exploration and the red flashes stand for errors hidden in the system. System properties are specified using temporal logics like CTL, CTL\*, LTL, PLTL or by using assertions. Model checking is regarded as a successful method frequently used to uncover well-hidden errors.

The ultimate goal of this technique is to answer the question: "Does the model A satisfy the

property Q?". A positive reply guarantees that the underlying property holds for all behaviors of the model (at the level of the mathematical proof). A negative reply is usually accompanied by a counter-example that represents a particular run of the system which leads to a violation of the desired property.

The main obstacle encountered by the model checking algorithms is the state space explosion problem. A system easily handled by a simulator, a compiler or an interpreter may be unable to be verified in a reasonable time and by using reasonable resources by a model checker. In practice, model checking requires a good expertise from the user, especially to deal with formulation of properties.

Figure 2.3: Exploration of the state space by model checking.

- *Theorem proving* represents a deductive verification method. It is similar to the classical mathematical way of proving theorems starting with axioms and inferring further facts using rules of the correct inference. This approach is very general but semi-automated as it requires a significant manual intervention of users.

- Equivalence checking proves that two representations of a circuit exhibit exactly the same behavior (they are logically equivalent). This approach uses mainly the RTL description of a circuit as a golden reference model. The behavior of the same circuit but described at different level of abstraction (typically the gate-level netlist), is then compared to this reference model. The initial netlist usually undergoes a number of modifications, optimizations or replacements of logic elements during synthesis. Throughout this process, the original functionality and the behavior described by the original code must be maintained.

To conclude, no ideal formal technique that would provide fully automated proofs for all types of systems exists. The choice of the best suited approach strongly depends on the concrete verification problem. Currently in practice, mainly critical system parts are formally verified, e.g. pipeline behavior in processors or dedicated controllers.

#### 2.3.3 Functional Verification

*Functional verification* is based on simulation (therefore, it also cannot prove the correctness of a system) but uses more sophisticated testbenches with additional features.

First of all, it generates a suite of constrained-random input stimuli and compares the behavior of DUV with the behavior specified by a provided reference model. The reference model is prepared according to the specification in HVL, C/C++ or other languages that are supported. The progress in verification is measured using coverage metrics which express different measurable properties of DUV (functions, source code, instructions, etc.). To facilitate the process of verification and to

formally express the intended behavior of a system, *assertions* may be used. All these functional verification techniques will be described in detail in Chapter 3.

Unlike model-checking, functional verification explores the state space of a system in different manner, more to the depth (as can be seen in Figure 2.4). In this way, also states of the system that were not covered by model-checking (because of the state-space explosion problem) can be reached.

Figure 2.4: Exploration of the state space in functional verification.

Further, this approach is based more on the following idea: the longer the verification run is, the higher is the chance that there are no errors left in the state space (or, at least, the most critical and reachable errors have been found and removed). In Chapter 3, functional verification is elaborated in more details.

# Chapter 3

# **Functional Verification in SystemVerilog**

In the rest of this Ph.D. thesis, the attention is paid to functional verification as it is one of the most dominant verification approaches used in industry [90, 77, 7] for the pre-silicon checking of hardware systems. The focus is taken on identifying problems that need to be solved, especially those connected with the speed, the automation and the completeness of functional verification. Verification environments for functional verification are implemented in the SystemVerilog language usually with respect to some well-known verification methodology. Afterwards, they are running in some RTL simulator, e.g. , QuestaSim from Mentor Graphics, Riviera-PRO from Aldec, VCS from Synopsys or Incisive Enterprise Simulator from Cadence.

SystemVerilog is a complex programming language for hardware design and especially for functional verification. While created as the next generation of the Verilog language, it has adopted features from many other programming languages with great impact on its simulation and verification capabilities. SystemVerilog provides a basis for building techniques that increase the efficiency of verification processes. The description of some of these techniques follows:

- Object-Oriented Programming (OOP). This approach allows easier design of large systems with support of common design patterns or reusable components. Verification environments are more modular and thus easier to develop and debug. The mechanisms of encapsulation, inheritance and polymorphism support the reuse of verification components, which leads to an increase in productivity. Several orders of re-usability are possible. The first order is when the same verification environment is used across multiple test cases on the same project. The second order occurs when some verification components are used several times in the same project environment. The third order is when some verification components are used across different verification environments for different systems. The reuse was significantly improved when verification methodologies that are introduced in Section 3.2 were incorporated into functional verification. They provide libraries of freely available and reusable components that are just modified for particular use, mostly in terms of interfaces and reference models.

- Constrained-random stimuli generation. For checking full functionality of a larger design it becomes more difficult to create a complete set of stimuli. A suitable solution is to create test cases automatically using constrained-random stimuli generation to target corner cases and stress conditions. Test scenarios are restricted to be valid using constraints. Constraints define the correct form of the generated data and can be also used to guide verification tests to interesting DUV states. Due to randomly generated stimuli, it is necessary to use coverage mechanisms to explore the DUV state space evenly.

- Assertion-Based Verification (ABV). This is a technique used to formally express the intended design behaviour, internal synchronization, and expected operations, using assertions (i.e. properties that must hold at all times). Assertions can be expressed at many levels of the device including internal and external interfaces (to detect critical protocol violations), clock-domain crossings and state machines. Assertions create monitors at critical points of the design without having to create separate testbenches where these points would be externally visible. ABV also guides the verification task and accelerates the verification because it provides feedback at the internal level of the device as it is possible to locate the cause of a problem faster than from the output of a simulation. Two examples of assertion languages are Property Specification Language (PSL) and SystemVerilog Assertions (SVA).

- Cooperation with other programming languages. Direct Programming Interface (DPI) allows SystemVerilog code to call functions in other programming languages as if they were native SystemVerilog functions. Data can be passed between the two domains through function arguments and results. Inter-operable environments and components may be used to reduce the effort required to verify a complete product in case some parts of the product are already prepared in other programming languages.

- Coverage-Driven Verification (CDV). Coverage is an important part in functional verification [60]. Let us define a terminology connected with the coverage at first.

**Coverage metric** is one measurable attribute of a circuit, e.g. the number of executed lines of code or the number of checked arithmetical operations. In general, it is possible to specify different coverage metrics in functional verification which are connected either with the source code or with the intended functionality.

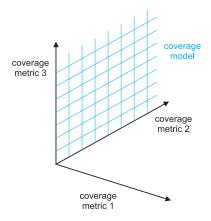

Coverage space represents an *n*-dimensional region defined by *n* coverage metrics.

**Coverage model** is an abstract representation of a circuit composed of selected  $i \le n$  coverage metrics and their relationship. It forms an *i*-dimensional subspace of the *n*-dimensional coverage space.

A 3-dimensional coverage space is illustrated in Figure 3.1. The dimensions of this coverage space are built by 3 different coverage metrics. A 2-dimensional subspace forms one coverage model.

Figure 3.1: The 3-dimensional coverage space.

Coverage models create a basis for measuring the quality and completeness of functional verification. In other words, coverage models allows to measure how well input stimuli cover

the most of the possible behaviors (measurable properties) of DUV. It became also a part of various industrial standards like DO-178B, DO-178C, and ISO 26262.

Achieving *coverage closure* means provoking the occurrence of each (or some threshold) of the measurable properties [60]. RTL simulators offer coverage analysis and produce statistics about which coverage items were covered during the verification runs. If there are holes (unexplored areas) in the coverage analysis, the verification effort is directed to the preparation of suitable test scenarios which will be able to cover these holes. That is the reason why this approach is called coverage-driven verification. One option is to manually change the constraints of the pseudo-random generator, the second option is to prepare direct tests.

The list of supported coverage metrics follows, some of them are generated automatically in a simulator, other must be written by hand.

- Functional coverage is specified manually; it measures how well input stimuli cover the functional specification of DUV. It focuses mostly on the semantics, e.g.: Did the test cover all possible commands or did the simulation trigger a buffer overflow? For more precise definition and examples, see Chapter 4 in [60] or Chapter 18 in IEEE SystemVerilog standard [1].

- Structural coverage is generated automatically by a simulation tool, so no extra HVL code needs to be written because the code coverage tool included in many simulators instruments the design automatically by analyzing the source code and adding hidden code to gather statistics. In general, structural coverage measures how well input stimuli cover the implementation (the source code) of DUV. For more precise definition and examples, see Chapter 5 in [60] or Chapter 29 in IEEE SystemVerilog standard [1]. Typical structural coverage metrics are defined below.

- \* Toggle coverage measures how many times signals and latches in the HDL model of a hardware system changed their logic values during the simulation. The absence of signal change activity indicates that any input stimulus did not target a specific corner area of the verified system. It considers mainly the block-level structure of the design not its functional significance.

- \* Code coverage takes the syntactical structure of an HDL specification and measures which HDL lines were executed by a verification run. The limitation of code coverage is the missing semantic insight; there is no knowledge about the correctness of the system in the case of coverage holes. Code coverage metric can be concretized to statement coverage, branch coverage, condition coverage and expression coverage.

- \* Finite State Machine coverage associates the state-machine structures in HDL designs and measures visited states (state coverage) and transitions between these states (transition coverage).

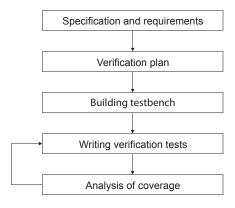

#### 3.1 Verification Process

Verification is a complex task, therefore, a lot of effort should go into specifying when a DUV can be considered as fully verified. Inspired by [8] we introduce the main steps of a verification process (Figure 3.2):

Figure 3.2: Steps of the verification process.

#### 3.1.1 Specification and Requirements

In order to check a new implementation of DUV for its functional correctness, we need a reference description, either a text specification or a previous *golden model* reference implementation which represents the intention of the design. In many cases, the specification is given on a higher level of abstraction so it does not capture the detailed behaviour of the design.

The requirements for the appropriate verification process are built according to the specification of the functionality of the device. The requirements should be defined as soon as possible in the project life cycle, ideally while the architectural design is in progress. It is recommended that the requirements are identified by all members of the project team: hardware and software developers as well as verification engineers. A few examples of requirements are: definition of legal input and output patterns according to the protocols of used interfaces, description of incorrect behaviour of the device, identification of potential corner cases, supported configurations, errors from which the design can or cannot recover and how the system responses and behaves in such cases.

### 3.1.2 Verification Plan

A verification plan helps verification engineers to understand how verification should be done. It is closely tied to the specification and requirements and contains a description of which features need to be exercised and which techniques and tools should be used to achieve the specific goals so that the progress in verification could be easily measured.

Moreover, it should contain a precise definition of all the resources that will be needed and not only the computational resources but also human and financial resources.

- The stimuli generation plan chooses the character of input sequences:

- a) Direct tests each test contains direct sequences of stimuli which are targeted at a very specific set of design elements. The DUV is stimulated with these sequences and the resulting log files and waveforms are then manually reviewed to make sure that the design behaves according to the specification. Direct tests typically find errors that are expected to be in the design and cover the state space very slowly. Creating complex stimuli set is a very time-consuming and challenging task because this approach requires a verification engineer to write many tests in order to achieve high coverage.

- b) Constrained-random stimuli generation tests as designs become more complex it is impossible to use only direct tests. A more efficient way to verify complex designs thoroughly is with constrained-random stimuli generation. The widest possible range of stimuli can help to find bugs which were not anticipated. Random tests explore the space much faster than direct tests, reduce the number of required tests, and increase productivity and quality of the verification process.

- *The coverage plan* specifies which coverage metrics will be used to track the progress in verification and what is the level of coverage that should be achieved in every such metric.

- *The checker plan* uses mechanisms for predicting the expected response and for comparing the observed response (typically from external outputs of DUV) against the expected one. These checks should be intelligent and independent of test cases. The following list introduces several means of predicting expected responses.

- a) Assertions these are used to verify the response of the device based on internal signals. Any detected discrepancy in the observed behaviour results in an error which is reported near to the origin of the functional defect. Assertions work well for verifying local signal relationships; they can detect errors in handshaking, state transitions and protocol rules. On the other hand, they are not well suited for detecting data transformations, computation and ordering errors. Despite the effectiveness of assertions, they are limited to the types of properties that can be expressed only using expressions in a clock temporal logic.

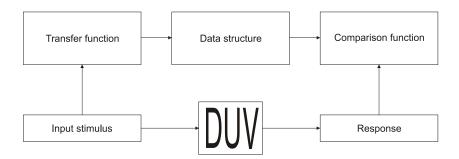

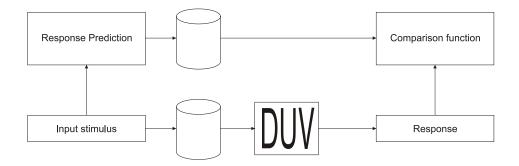

- b) Scoreboarding a scoreboard is used to dynamically predict the response of the device. Stimulus applied to the device is also passed to the transfer function which performs all transformations on the stimulus to produce the form of the final response. Modified stimulus is inserted into a data structure called transaction. The observed response from the DUV in the form of the transaction is forwarded to the comparison function which verifies whether it reflects the expected response or not (Figure 3.3).

Figure 3.3: Scoreboarding.

The transfer function may be implemented using a reference (golden) model, even e.g. in the C, C++ language (and integrated into the testbench through the DPI). The data structure stores the expected response until it can be compared against the observed output. It means that DUV and the reference model can run asynchronously to each other. Scoreboarding works well for verifying the end-to-end response of a design and the integrity of the output data. It can efficiently detect errors in data computations, transformations and ordering. It can also easily identify missing or spurious data.

c) Reference model — like a scoreboard, it is used to dynamically predict the response of the device. The stimulus applied to the design is also passed to the reference model. The output of the reference model is compared against the observed response (Figure 3.4). The reference model mechanism has the same capabilities and challenges as the use of scoreboards. Unlike a scoreboard, the comparison function works directly from the output of the reference model so that it has to produce outputs in the same order as the design itself. However, there is no need to produce the output with the same latency or cycle accuracy. The comparison of the observed response is performed at the transaction-level, not at cycle-by-cycle level. The use of reference models depends heavily on their availability. If they are not available, scoreboard techniques are more efficient to be used. Reference models are often written in the C, C++ language and therefore easily exploitable by a SystemVerilog testbench using the mechanism of the DPI.

Figure 3.4: Reference model.

- d) **Accuracy** the simplest comparison function compares the observed output of the design with the predicted output on a cycle-by-cycle basis, so synchronously. This approach requires the response to be accurately predicted down to the cycle level.

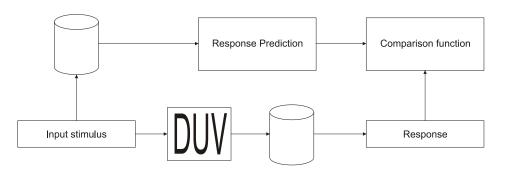

- e) Offline checking used to predict responses of the design before or after a simulation of the design is done. In pre-simulation prediction, the offline checker produces a description of expected responses, which are dynamically verified against the observed responses during the simulation (Figure 3.5). Some utilities can perform post-simulation comparison (Figure 3.6). In both cases the response can be checked at the cycle-by-cycle or the transaction level with reordering. Off-line checkers work well for verifying the end-to-end response of a design and the integrity of the output data based on executable system-level specifications or mathematical models. Although offline checkers are usually used with a reference model, they can be used also with scoreboard techniques implemented as a separate offline program.

#### 3.1.3 Building Testbench

Verification environments (also called testbenches) determine the correctness of the DUV. This is accomplished in general by:

- 1. generating stimuli,

- 2. applying stimuli to the DUV,

- 3. capturing the response,

Figure 3.5: Pre-simulation offline checking.

Figure 3.6: Post-simulation offline checking.

- 4. checking correctness of the response,

- 5. measuring progress against the overall verification goals.

The continuous growth in the complexity of hardware designs requires a modern, systematic and automated approach to creating verification environments. One of the big challenges in developing verification environments is to make effective use of the OOP paradigm. When used properly, these features can greatly enhance the re-usability of testbench components.

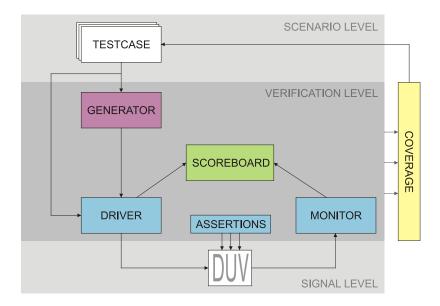

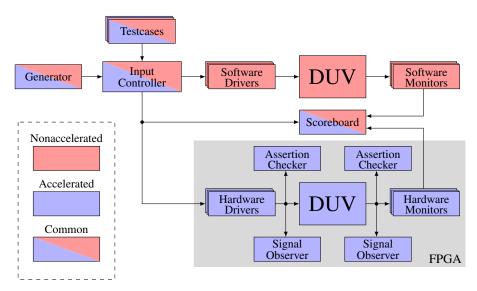

Functional verification environments are usually complex so it is highly desirable to divide the code into smaller pieces that can be developed separately. Some general components can be recognized in Figure 3.7

#### • Scenario level:

Testcases are situated on the top of the verification environment. They are implemented

as a combination of additional constraints for generators, new random scenario definitions, synchronization mechanisms between stimuli, or by direct stimuli.

#### • Verification level:

- The generator produces constrained random stimuli and passes them to the driver.

- The driver receives high-level direct stimuli, usually in the form of data structures called transactions, from the generator, breaks them down into individual signal changes, supplies them on the input interfaces of the DUV, and sends their copies to the scoreboard.

The driver may also inject errors or add delay parts.

Figure 3.7: A verification environment.

- The monitor drives the output interfaces of DUV, observes signal transitions, groups them together into high-level transactions and passes them to the scoreboard.

- The scoreboard compares transactions received from the driver and from the monitor and in the case they do not match, an error is reported.

- Assertions check the validity of protocols on interfaces of the DUV. In the case of violation they directly report the failing assertion.

#### • Signal level:

DUV is connected to the verification level components through a set of signals. This

layer provides pin name abstraction to enable the whole verification environment to be

used unmodified with different implementations of the same DUV.

Verification environments and test cases should access the design only through the verification level and never access the signal level unless absolutely necessary.

#### 3.1.4 Writing Verification Tests

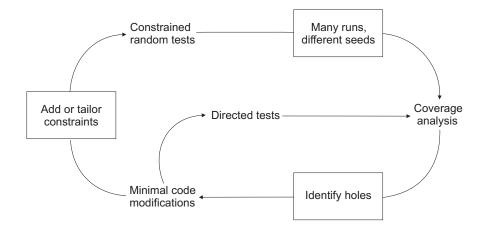

After the testbench is applied to the DUV it is the time for validating the DUV. By analyzing coverage reports, new tests are written to cover holes in coverage using two different approaches. The first method captures a new run of the simulation with a different seed of the generator or tailors constraints on input stimuli (creating many unique input sequences with constrained-random stimuli generation). The other approach represents creating direct tests. This iterative process can be seen in Figure 3.8.

#### 3.1.5 Analysis of Coverage

Coverage tools gather information during a simulation and post-process them in order to produce a coverage report. After analyzing both functional and structural coverage reports, new tests are written to reach uncovered areas of the design until a sufficient level of coverage is achieved.

Figure 3.8: Analysis of coverage.

## 3.2 Verification Methodologies

The success of verification does not depend only on the verification language. The target is to create an applicable verification methodology that uses common approach and creates highly inter-operable verification environments and components. An effective methodology must address the main verification challenges: productivity and quality. Coverage-driven verification coupled with constrained-random stimuli generation are currently becoming the main principles of verification methodologies.

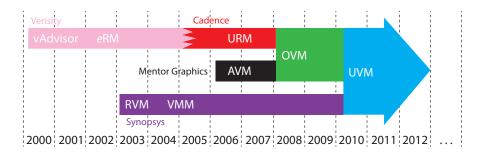

Various methodologies were developed with collaboration of different companies as shown in Figure 3.9, a description of three most popular follows.

Figure 3.9: The evolution of verification methodologies.

• Verification Methodology Manual (VMM) [8] — was co-authored by verification experts from ARM and Synopsys. VMM's techniques were originally developed for use with the OpenVera language and were extended in 2005 for SystemVerilog. VMM has been successfully used to verify a wide range of hardware designs, from networking devices to processors. It describes how to build scalable, predictable and reusable verification environments. Very useful is the set of base classes for data, environment and utilities for managing log files and interprocess communication. VMM is focused on the principles of coverage-driven verification and follows the layered testbench architecture to take full advantage of the automation

when each layer provides a set of services to the upper layers while abstracting them from lower-level details.

- Open Verification Methodology (OVM) [31] this methodology is the result of a joint development between Cadence and Mentor Graphics to facilitate true SystemVerilog interoperability with a standard library and a proven methodology. The class library provides building blocks which are helpful for fast development of well-constructed and reusable verification components and test environments in SystemVerilog. The OVM class library contains:

- component classes for building testbench components,

- reporting classes for logging,

- factory for object substitution,

- synchronization classes for managing concurrent processes,

- sequencer and sequence classes for generating realistic stimuli.

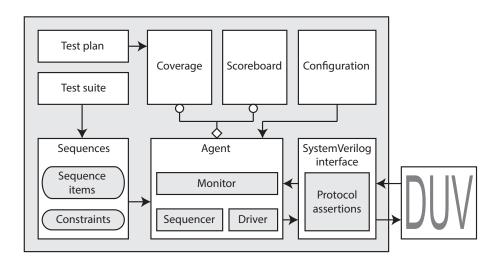

- Universal Verification Methodology (UVM) [69] is a state of the art methodology that extends OVM. In Figure 3.10, the architecture of the UVM testbench is shown. The basic components that were presented in Section 3.1.3 are recognizable and some additional components are present.

Figure 3.10: The UVM verification environment.

The *Test plan* contains all the test cases that will be evaluated during verification. Every test case (*Test suite*) consists of several *Sequences* that encapsulate input stimuli (*Sequence items*). There, the generator of pseudo-random stimuli can be utilized. Therefore, *Constraints* can be present here which restrict the generated data. Sequence items are propagated to the unit called *Sequencer* and from this unit to the *Driver* that drives input ports of DUV. Output ports of DUV are monitored by the *Monitor* unit. Sequencer, Driver and Monitor are grouped together in the structure called *Agent*. The purpose of Agents is to tie the components that are logically bounded to some *SystemVerilog virtual interface* which corresponds to one or more real interfaces of DUV (a virtual interface logically encapsulates input and output signals of DUV). If the DUV contains several interfaces of the same type, more Agents of the same type

are instantiated in the verification environment as well as more virtual interfaces. *Assertions* that check the validity of protocols are also present here. Furthermore, *Coverage* monitors are instantiated in the verification environment and they measure user-defined functional properties. Of course, the most important part of testbenches is *Scoreboard* which implements the reference functionality. It can be either implemented in SystemVerilog or can contain a reference model in C/C++. UVM also adds advanced *Configuration* options to the verification environments, so all components are configured systematically and hierarchically.

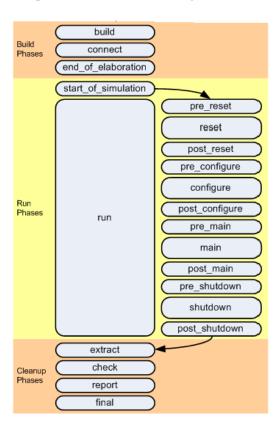

*Phasing* is another very important part of UVM. Despite phasing was firstly introduced in OVM, UVM moves it to the next level as it is more elaborated and more efficient. The common phases are the set of functions and tasks that all UVM components execute together. In other words, all UVM components are always synchronized with respect to the common phases. All the common phases are illustrated in Figure 3.11.

Figure 3.11: The UVM common phases. Source: http://www.soccentral.com/

# 3.3 Chapter Overview

In this chapter, the functional verification approach was introduced as it is the main topic of this Ph.D. thesis. Functional verification environments are mostly written in the SystemVerilog language, therefore, features of this language were described as well as the steps how to build effective and reusable verification environments according to the verification methodologies (OVM, UVM).

# **Chapter 4**

# **Evolutionary Computing**

This chapter familiarizes the reader with the basics about Evolutionary Computing (EC). The reason for incorporating this chapter is that EC will be used as an optimization tool in the techniques proposed in this Ph.D. thesis and therefore, it is reasonable to understand the essential terms.

The main principles of EC and a brief history of this field are presented. Afterwards, a general scheme that forms the common basis for all the variants of Evolutionary Algorithms (EA) is outlined and the main components of EAs are discussed, explaining their role and relating issues of terminology. Further, general issues concerning operation of EAs are discussed, they are placed in a broader context and their relationship with other global optimization techniques is explained. An important part is the description of the most widely known type of EA: the Genetic Algorithm (GA), because it will be frequently referred in the thesis. Finally, the issue of setting the values of various parameters of GA is discussed as it is crucial for good performance. The theoretical background for this chapter is taken from [26, 73, 67].

# 4.1 Main Principles of Evolutionary Computing

Evolutionary computing is a computer science research area. As the name indicates, it is a special way of computing, which draws inspiration from the process of Darwin's natural evolution [21]. Let us consider natural evolution simply as follows. A given environment is filled with a population of individuals that compete for survival and reproduction. The *fitness* of these individuals - determined by the environment - relates to how well they succeed in achieving these goals, i.e., it represents their chances of survival and multiplying. In the context of a stochastic problem solving process, we have a collection of candidate solutions. Their quality (that is how well they solve the problem) determines the chance that they will be kept and used as seeds for constructing further candidate solutions (Table 4.1). This phenomenon is also known as the **survival of the fittest**.

Table 4.1: The basic evolutionary computing metaphor linking natural evolution to problem solving (source [26]).

| Evolution   |                   | Problem solving    |

|-------------|-------------------|--------------------|

| Environment | $\longrightarrow$ | Problem            |

| Individual  | $\longrightarrow$ | Candidate solution |

| Fitness     | $\longrightarrow$ | Quality            |

## 4.2 Brief History

Surprisingly enough, the idea of applying Darwinian principles to automated problem solving dates back to the forties, long before the breakthrough of computers [29]. As early as 1948, Turing proposed "genetical or evolutionary search", and by 1962 Bremermann had actually executed computer experiments on "optimizing through evolution and recombination". During the 1960s, three different implementations of the basic idea were developed in different places. In the USA, Fogel, Owens, and Walsh introduced *evolutionary programming* [30], while Holland called his method a *genetic algorithm* [43, 44]. Meanwhile, in Germany, Rechenberg and Schwefel invented *evolution strategies* [66, 72]. For about 15 years, these areas were developing separately; but since the early 1990s they have been viewed as different representatives of one technology that has come to be known as *evolutionary computing* [4, 5]. In the early 1990s a fourth stream following the general ideas emerged. It was called the *genetic programming* [52, 53] and was introduced by Koza. The contemporary terminology denotes the whole field by evolutionary computing, the algorithms evolved are termed as *evolutionary algorithms*, and it considers evolutionary programming, evolution strategies, genetic algorithms, and genetic programming as sub-areas belonging to the corresponding algorithm variants.

Computation in the second half of the 20th century has created a rapidly growing demand for problem solving automation. The growth rate of the research and development capacity has not kept pace with these needs. Hence, the time available for thorough problem analysis and tailored algorithm design has been, and still is, decreasing. A parallel trend has been the increase in the complexity of problems to be solved. These two trends, and the constraint of limited capacity, imply an urgent need for robust algorithms with satisfactory performance. That is, there is a need for algorithms that are applicable to a wide range of problems, do not need much tailoring for specific problems, and deliver good (not necessarily optimal but acceptable) solutions within acceptable time. Evolutionary algorithms do all this, and therefore, provide an answer to the challenge of deploying automated solution methods for more and more problems, which are more and more complex, in less and less time.

## 4.3 Main Components of Evolutionary Algorithms

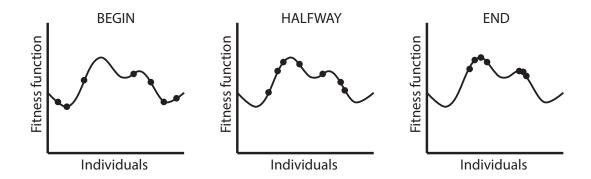

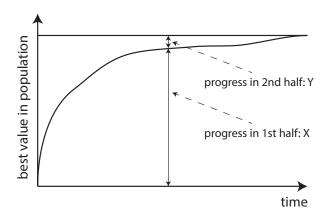

As the history of the field indicates, many different variants of evolutionary algorithms exist. The common underlying idea behind all these variants is the same: given a population of individuals within some environment that has limited resources, competition for those resources caused by natural selection and the survival of the fittest. During evolution, this is reflected by continuous improvement of the fitness in the population.

There are two fundamental forces that form the basis of evolutionary systems:

- Variation operators (*recombination* and *mutation*) create necessary diversity within the population, and thereby facilitate novelty.

- Selection acts as a force increasing the mean quality of solutions in the population.

It should be noted that many components of the evolutionary process are *stochastic*. It means that randomness plays a considerable role here. Thus, although during selection fitter individuals have a higher chance of being selected as parents than the less fit ones, there is a chance that even the weak individuals can become parents or can survive. During the recombination process, the choice of which pieces from the parents will be recombined is made at random. Similarly for mutation, the

choice of which pieces will be changed within a candidate solution and of the new pieces to replace them is made randomly.

The general pseudo-code of an evolutionary algorithm is given in Algorithm 1.

#### **Algorithm 1:** The pseudo-code of EA.

#### **Function** EA:

INITIALIZE population with random candidate solutions;

EVALUATE each candidate;

while termination condition is not satisfied do

SELECT parents;

*RECOMBINE* pairs of parents;

*MUTATE* the resulting offspring;

EVALUATE new candidates;

SELECT individuals for the next generation;

end

The various dialects of EAs that were mentioned previously all follow these general steps, differing only in technical details. In particular, the representation of a candidate solution is often used to characterize different streams. Typically the representation (i.e. the data structure encoding a candidate solution) has the form of: string over a finite alphabet in genetic algorithms, real-values vectors in evolution strategies, finite state machines in classical evolutionary programming, and trees in genetic programing. The origin of these differences is mainly historical. Technically, one representation might be preferable to others if it matches the given problem better; that is, it makes the encoding of candidate solutions easier or more natural. For instance, when solving a satisfiability problem with n logical variables, the straightforward choice is to use the bit-strings of length n, hence the appropriate EA would be the genetic algorithm. To evolve a computer program that can play checkers, trees are well suited, thus a genetic programing approach is likely. It is important to note that the recombination and mutation operators must match the given representation. Thus, for instance, in genetic programing the recombination operator works on trees, while in GAs it operates on strings. In contrast to variation operators, the selection process only takes fitness information into account, and so it works independently from the choice of representation. Therefore, differences between the selection mechanism commonly applied in each stream are a matter of tradition rather than of technical necessity.

The most important components of EAs are:

- Representation (definition of individuals).

- Evaluation function (or fitness function).

- Population.

- Parent selection mechanism.

- Variation operators, recombination and mutation.

- Survivor selection mechanism (replacement).

To create a complete algorithm it is necessary to specify each of these components and to define the initialization procedure and a termination condition.

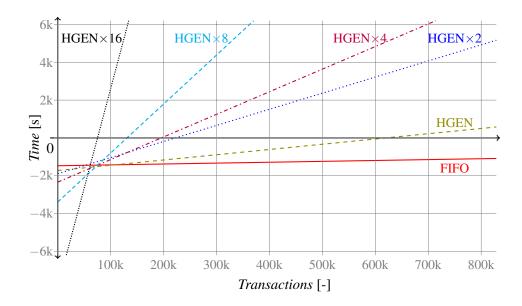

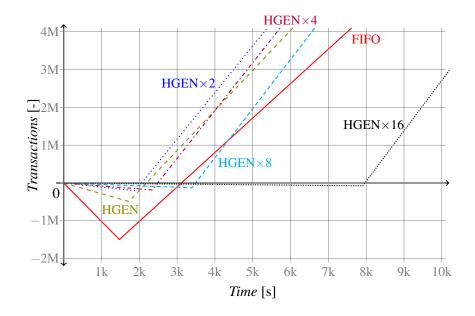

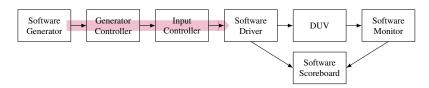

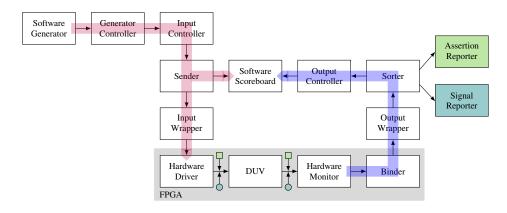

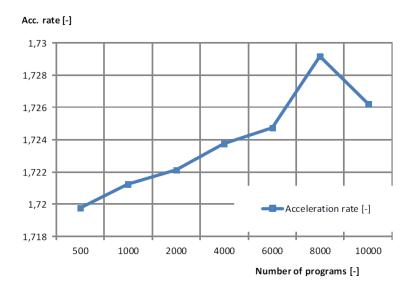

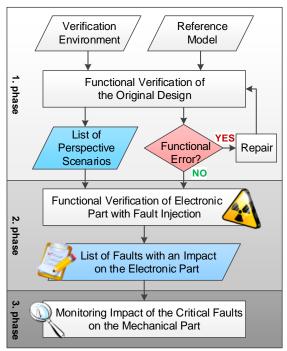

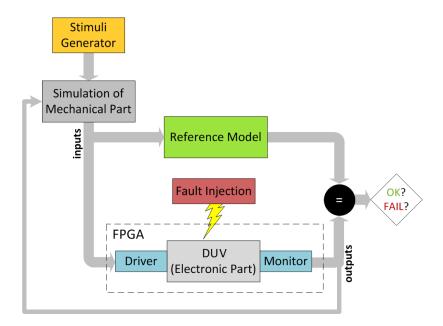

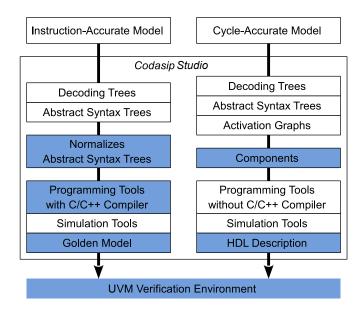

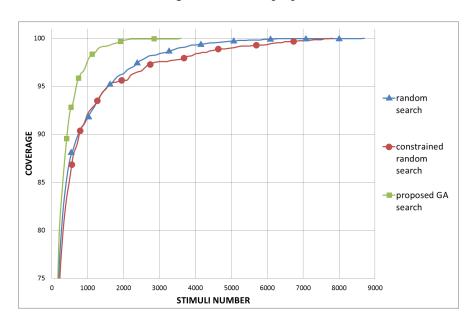

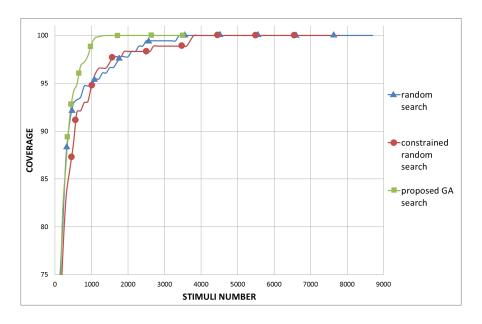

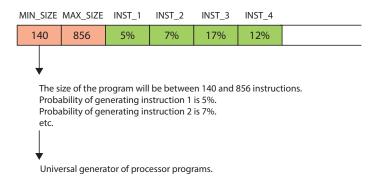

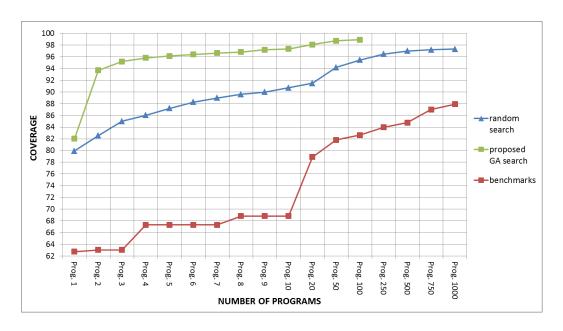

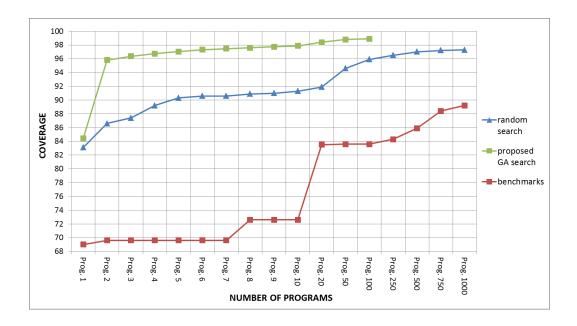

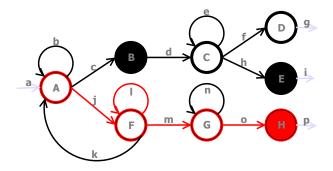

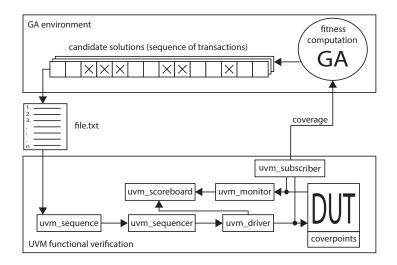

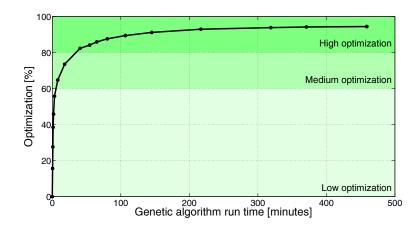

#### **4.3.1** Representation (Definition of Individuals)