# BRNO UNIVERSITY OF TECHNOLOGY

# Faculty of Electrical Engineering and Communication

# MASTER'S THESIS

Brno, 2022

Bc. Vojtěch Král

# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

## **DEPARTMENT OF RADIO ELECTRONICS**

ÚSTAV RADIOELEKTRONIKY

# SAVING POWER AND AREA WITH MULTI-BIT PULSED LATCHES

ÚSPORA SPOTŘEBY A PLOCHY PŘI POUŽITÍ MULTI-BITOVÝCH PULSNÍCH KLOPNÝCH OBVODŮ

#### MASTER'S THESIS DIPLOMOVÁ PRÁCE

AUTHOR AUTOR PRÁCE Bc. Vojtěch Král

### SUPERVISOR VEDOUCÍ PRÁCE

Ing. Jiří Dřínovský, Ph.D.

## **BRNO 2022**

## **Master's Thesis**

Master's study program Electronics and Communication Technologies

Department of Radio Electronics

Student: Bc. Vojtěch Král Year of study: **ID:** 195671

Academic year: 2021/22

TITLE OF THESIS:

#### Saving power and area with multi-bit pulsed latches

#### INSTRUCTION:

Study the possibilities of reducing the consumption of digital parts in ASIC design. Especially pulse generator topologies driving latches study in more details. Such design can replace broadly used sequential circuits. During the study of the open literature, focus done on topology with low consumption and low area. Also, take into an account the balance between the simplicity of design and the reliability at conditions stated in the assignment. Choose the most appropriate topology and design a multi-bit pulsed latch. Required operating parameters of the multi-bit pulsed latch in onsemi 65 nm technology are: the presence of scan input, a version without reset pin and with reset pin, supply voltage 1.2 V  $\pm$  10% and temperature range from -40 ° C to 150 °C. Also, determine the frequency range in which the multi-bit pulsed latches can operate.

Follow up on the results from your semester project and create a complete design of a multi-bit pulsed latch circuit in onsemi 65 nm technology, including simulations using the Specter simulator. Optimize the design for power consumption and for minimum layout area. In the next step create layouts of basic types of multi-bit pulsed latches and perform simulations with netlists extracted from the layout, including parasitic elements. Try to prove the positive impact on consumption and area in a simple design by replacing classic multi-bit flip-flops with multi-bit pulsed latches.

#### RECOMMENDED LITERATURE:

[1] E. Consoli, G. Palumbo, J. M. Rabaey and M. Alioto, "Novel Class of Energy-Efficient Very High-Speed Conditional Push–Pull Pulsed Latches," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 22, no. 7, pp. 1593-1605, July 2014, doi: 10.1109/TVLSI.2013.2276100.

[2] V. Ahuja, P. T. Karule and U. S. Ghodeswar, "Design of high speed conditional push pull pulsed latch," 2016 International Conference on Communication and Signal Processing (ICCSP), 2016, pp. 1374-1378, doi: 10.1109/ICCSP.2016.7754378.

Date of project specification: 11.2.2022 Deadline for 25.5.2022 submission:

Supervisor:Ing. Jiří Dřínovský, Ph.D.Consultant:Ing. Jiří Šolc

**prof. Dr. Ing. Zbyněk Raida** Chair of study program board

Faculty of Electrical Engineering and Communication, Brno University of Technology / Technická 3058/10 / 616 00 / Brno

#### WARNING:

The author of the Master's Thesis claims that by creating this thesis he/she did not infringe the rights of third persons and the personal and/or property rights of third persons were not subjected to derogatory treatment. The author is fully aware of the legal consequences of an infringement of provisions as per Section 11 and following of Act No 121/2000 Coll. on copyright and rights related to copyright and on amendments to some other laws (the Copyright Act) in the wording of subsequent directives including the possible criminal consequences as resulting from provisions of Part 2, Chapter VI, Article 4 of Criminal Code 40/2009 Coll.

Faculty of Electrical Engineering and Communication, Brno University of Technology / Technická 3058/10 / 616 00 / Brno

## Abstract

This thesis describes types of power consumption in CMOS technology and low power techniques that can be used in application-specific integrated circuits. It describes a multibit pulsed latch as one of the low power techniques that can be used as a better replacement for a standard multi-bit master-slave flip flop. The multi-bit pulsed latch is composed of two parts: a pulse generator and a pulsed latch. Different useful topologies are mentioned. Topologies are chosen for their optimized area and power consumption. A schematic of the multi-bit pulsed latch is designed from chosen topologies and compared to a schematic of the standard multi-bit flip flop. Required layouts of multi-bit pulsed latches are then made and compared to standard layouts of multi-bit flip flops. Those designed multi-bit pulsed latches are also simulated in a simple design.

## Keywords

Pulse latch, flip flop, multi-bit pulsed latch, low power techniques, pulse generator, CMOS, low power consumption

## Abstrakt

Diplomová práce se zabývá typy výkonových ztrát v technologii CMOS a následně jejich řešením metodami nízké spotřeby, které lze použít v oblasti zákaznických integrovaných obvodů. Jednou z možných metod pro nízkou spotřebu výkonu je vícebitový pulzní klopný obvod, který lze použít jako náhradu za standardní vícebitový klopný obvod typu master-slave. Vícebitový pulzní klopný obvod se skládá ze dvou částí, pulzního generátoru a pulzního klopného obvodu. V diplomové práci jsou popsané topologie, které mohou být použité. Konečná topologie byla vybraná na základě nízké spotřeby a plochy. Z vybrané topologie je vytvořeno schéma vícebitového pulzního klopného obvodu, které je porovnáno se schématem vícebitového klopného obvodu. Následně jsou vytvořeny layouty potřebných vícebitových pulzních klopných obvodů a porovnány jsou se standardními layouty vícebitových klopných obvodů. V závěru práce jsou navrhnuté vícebitové pulzní klopné obvody odsimulovány v jednoduchém designu.

## Klíčová slova

Pulzní klopný obvod, klopný obvod, vícebitový pulzní klopný obvod, metody nízké spotřeby, pulzní generátor, CMOS, nízká spotřeba

## Rozšířený abstrakt

Diplomová práce se zabývá typy výkonových ztrát, které vznikají v technologie CMOS. CMOS technologie je nejpoužívanější technologií pro výrobu čipů, ve které se pro snížení spotřeby používají metody pro nízkou spotřebu. Za jednu z metod nízké spotřeby a velikosti se považuje vícebitový pulzní klopný obvod. Standardní vícebitový klopný obvod typu master-slave lze nahradit za vícebitový pulzní klopný obvod, který má lepší vlastnosti v porovnání s velikostí a spotřebou. Vícebitový pulzní klopný obvod se skládá ze dvou částí, z pulzního generátoru a pulzního klopného obvodu. Pulzní klopný obvod je klopný obvod, který lze řídit krátkým pulzem namísto klasického obdélníkového signálu, který má obvykle střídu signálu 1:1. Pulz je vytvořen v pulznímu generátoru, který je navržený tak, aby byl dostatečně dlouhý pro ovládání pulzního klopného obvodu. V diplomové práci se porovnávají různé typy pulzních generátorů a pulzních klopných obvodů. Topologie je vybraná na základě vhodných parametrů. Z vybraného pulzního generátoru a pulzního klopného obvodu je možné vytvořit vícebitový pulzní klopný obvod, který má lepší spotřebu a velikost než varianta s jedním bitem. Vícebitový pulzní klopný obvod má lepší spotřebu a velikost, protože má méně tranzistorů. Pro jeden generátor je použito více pulzních klopných obvodů. Z vybrané topologie je vytvořeno schéma vícebitového pulzního klopného obvodu, které je porovnáno se schématem vícebitového klopného obvodu. Následně jsou vytvořeny layouty potřebných vícebitových pulzních klopných obvodů a porovnány jsou se standardními layouty vícebitových klopných obvodů. Zjišť ují se i minimální a maximální použitelné frekvence všech obvodů. V závěru práce jsou navrhnuté vícebitové pulzní klopné obvody odsimulované v jednoduchém designu, ve kterém je potvrzeno, že vícebitové pulzní klopné obvody mohou být použity jako náhrada za standardní vícebitové klopné obvody.

## **Bibliographic citation**

KRÁL, Vojtěch. *Úspora spotřeby a plochy při použití multi-bitových pulsních klopných obvodů* [online]. Brno, 2022 [cit. 2022-05-14]. Dostupné z: <u>https://www.vutbr.cz/studenti/zav-prace/detail/141542</u>. Diplomová práce. Vysoké učení technické v Brně, Fakulta elektrotechniky a komunikačních technologií, Ústav radioelektroniky. Vedoucí práce Jiří Dřínovský.

## **Author's Declaration**

| Author:        | Bc. Vojtěch Král                                    |

|----------------|-----------------------------------------------------|

| Author's ID:   | 195671                                              |

| Paper type:    | Master's Thesis                                     |

| Academic year: | 2021/22                                             |

| Topic:         | Saving power and area with multi-bit pulsed latches |

I declare that I have written this paper independently, under the guidance of the advisor and using exclusively the technical references and other sources of information cited in the project and listed in the comprehensive bibliography at the end of the project.

As the author, I furthermore declare that, with respect to the creation of this paper, I have not infringed any copyright or violated anyone's personal and/or ownership rights. In this context, I am fully aware of the consequences of breaking Regulation S 11 of the Copyright Act No. 121/2000 Coll. of the Czech Republic, as amended, and of any breach of rights related to intellectual property or introduced within amendments to relevant Acts such as the Intellectual Property Act or the Criminal Code, Act No. 40/2009 Coll., Section 2, Head VI, Part 4.

Brno, May 10, 2022

\_\_\_\_\_

author's signature

## Acknowledgement

I would like to thank my supervisor and boss Jiří Šolc, who let me make this thesis on multi-bit pulsed latches. I would also like to thank my colleagues both at work and at school who helped me when I needed it the most. A big thank you also goes to my close family for their unlimited help in difficult times and my girlfriend Eliška Křížová for her unlimited positive energy and belief in me. Thank you, everybody.

Brno, May 10, 2022

-----

Author's signature

# Contents

| FIGURES                                                                                   | 8  |

|-------------------------------------------------------------------------------------------|----|

| TABLES                                                                                    | 10 |

| INTRODUCTION                                                                              | 11 |

| 1. CMOS TECHNOLOGY                                                                        | 13 |

| 1.1 FUNDAMENTALS OF CMOS TRANSISTORS                                                      | 13 |

| 1.2 DIGITAL STANDARD CELL LIBRARY                                                         | 15 |

| 1.3 PARAMETERS OF CMOS TRANSISTORS                                                        | 17 |

| 2. POWER CONSUMPTION IN CMOS TECHNOLOGY                                                   | 19 |

| 2.1 SWITCHING POWER                                                                       | 20 |

| 2.2 Short-circuit power                                                                   | 20 |

| 2.3 LEAKAGE POWER                                                                         | 21 |

| 2.3.1 Subthreshold leakage                                                                | 22 |

| 2.3.2 Thin gate-oxide tunneling leakage                                                   | 23 |

| 2.3.3 Reverse-bias pn-junction leakage                                                    | 23 |

| 3. LOW POWER TECHNIQUES                                                                   | 24 |

| 3.1 System                                                                                | 24 |

| 3.2 PLACE & ROUTE                                                                         |    |

| 3.3 Algorithm                                                                             | -  |

| 3.4 Architecture                                                                          | 27 |

| 3.5 Logic                                                                                 |    |

| 3.6 Technology                                                                            | 28 |

| 3.7 TOPOLOGY AND CIRCUIT                                                                  | 28 |

| 4. MULTI-BIT PULSED LATCH                                                                 | 30 |

| 4.1 Pulse generator                                                                       | 31 |

| 4.1.1 Suitable pulse generators                                                           | 33 |

| 4.1.2 Pulse generators for special purpose                                                | 38 |

| 4.2 PULSED LATCH                                                                          | 40 |

| 4.3 MULTI-BIT PULSED LATCH                                                                | 45 |

| 4.4 COMPARATION OF MULTI-BIT FLIP FLOPS AND MULTI-BIT PULSED LATCHES IN SIMPLE SIMULATION | ON |

| FROM SCHEMATIC NETLIST                                                                    | 54 |

| 4.5 LAYOUTS OF DESIGNED MULTI-BIT PULSED LATCHES                                          | 56 |

| 4.6 TESTING IN SIMPLE DESIGN                                                              | 70 |

| 5. CONCLUSION                                                                             | 72 |

| LITERATURE                                                                                | 74 |

| SYMBOLS AND ABBREVIATIONS                                                                 | 76 |

# **FIGURES**

| Figure 1.1 - Number of transistors in integrated circuits in dependence on years [7]               | 13 |

|----------------------------------------------------------------------------------------------------|----|

| Figure 1.2 - Symbol and functions of NMOS and PMOS transistors [9]                                 |    |

| Figure 1.3 - The side view of NMOS (left) and PMOS (right) transistors [3]                         |    |

| Figure 1.4 - Layout of inverter in 65 nm technology                                                |    |

| Figure 1.5 - Zoomed NMOS transistor from inverter cell with parameters of the transistor           |    |

| Figure 1.6 - The schematic of an inverter                                                          |    |

| Figure 2.1 - Dependence of normalized power on years [10]                                          |    |

| Figure 2.2 - Leakage components are shown in layout and schematic (I1 – Diode reverse bias current |    |

| Subthreshold current, I3 – Gate-induced drain leakage, I4 – Thin-oxide tunneling leakage) [11]     |    |

| Figure 3.1 - Example of AND glitch generator                                                       |    |

| Figure 3.2 - Differences between (a) normal, (b) parallelism, and (c) pipelined circuit [3]        |    |

| Figure 4.1 - Block diagram of multi-bit pulsed latch in normal mode                                |    |

| Figure 4.2 - Design of global and local pulse generator                                            |    |

| Figure 4.3 - Block diagram of multi-bit pulsed latch in scan mode                                  |    |

| Figure 4.4 - Block diagram of the simple pulse generator                                           |    |

| Figure 4.5 - Simulated block diagram from Figure 4.4 in MATLAB                                     |    |

| Figure 4.6 - Simple pulse generator made of inverter and 2-input AND                               |    |

| Figure 4.7 - Graph of dependence of inverter delay on transistor channel length                    |    |

| Figure 4.8 - Stacked inverter                                                                      |    |

| Figure 4.9 - Double-stacked inverter                                                               |    |

| Figure 4.10 - Five inverters delay (top) and three inverters delay (bottom)                        |    |

| Figure 4.11 - Double stacked inverter with 2-input logical AND                                     |    |

| Figure 4.12 - Generated pulses across the PVTs from chosen generator                               |    |

| Figure 4.13 - Block diagram of the pulse generator with 2-input NOR gate                           |    |

| Figure 4.14 - Simulated block diagram from Figure 4.13 in MATLAB                                   |    |

| Figure 4.15 - Circuit of the pulse generator with NOR logical gate                                 |    |

| Figure 4.16 - Circuit of the pulse generator with XOR logical gate                                 |    |

| Figure 4.17 - PTLA topology of a pulsed latch                                                      |    |

| Figure 4.18 - SSALA topology of a pulsed latch                                                     |    |

| Figure 4.19 - SSA2LA topology of a pulsed latch                                                    |    |

| Figure 4.20 - CPNLA topology of a pulsed latch                                                     |    |

| Figure 4.21 - PPCLA topology of a pulsed latch                                                     |    |

| Figure 4.22 - PPCLA modified topology of a pulsed latch                                            |    |

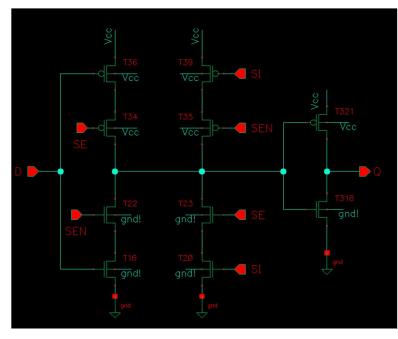

| Figure 4.23 - Standard 2-bit multiplexer                                                           |    |

| Figure 4.24 - Pass gate topology of 2-bit multiplexer                                              |    |

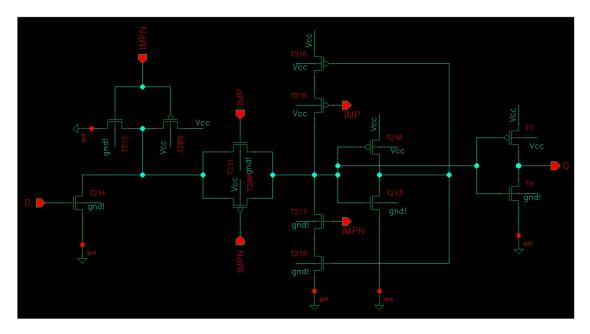

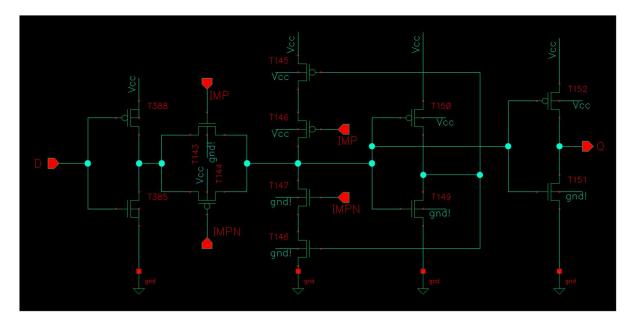

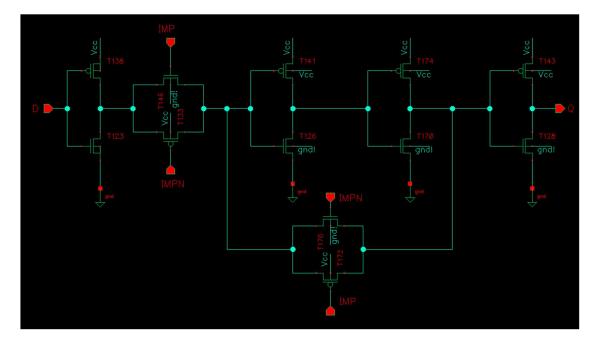

| Figure 4.25 - Pulsed latch with scan mode and negated output                                       |    |

| Figure 4.26 - 2-bit pulsed latch with scan mode and negated output                                 |    |

| Figure 4.27- Used topology of the pulsed latch with a multiplexer and reset pin                    |    |

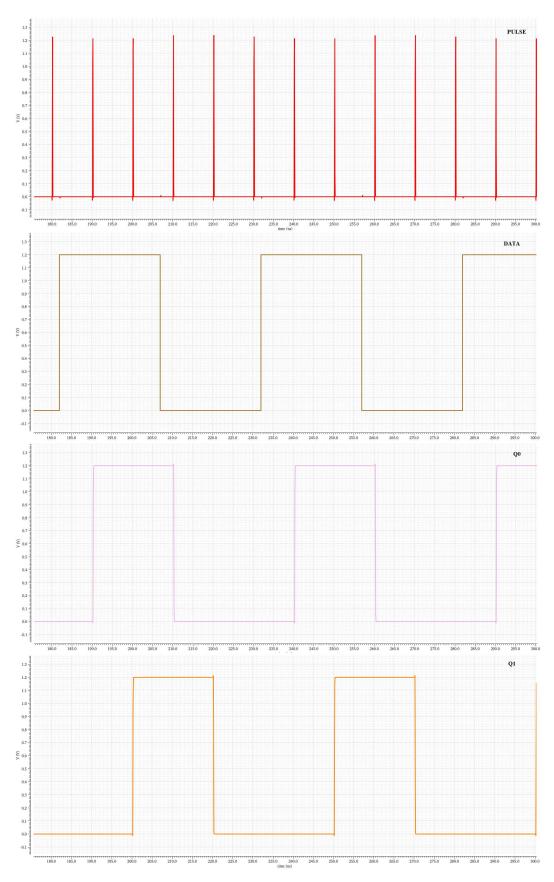

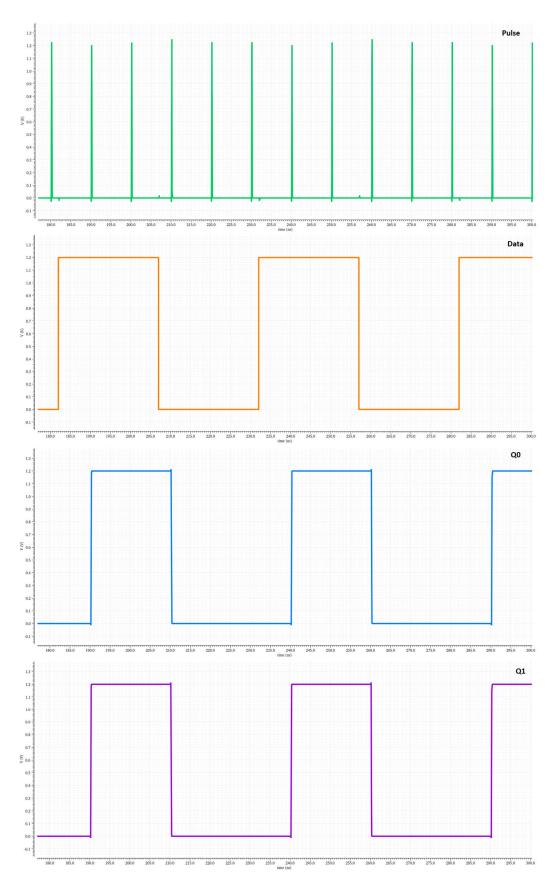

| Figure 4.28 – Graphs of 2-bit pulsed latch in scan mode                                            |    |

| Figure 4.29 – Graphs of 2-bit pulsed latch in normal mode                                          |    |

| Figure 4.30 - The 4-bit pulsed latch with scan mode and negated output                             |    |

| Figure 4.30 - The 4-bit pulsed latch with scan mode and negated output                             |    |

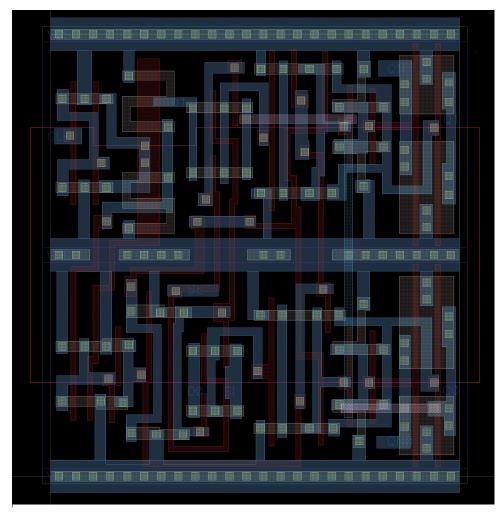

| Figure 4.32 - Layout of the plain 2-bit pulsed latch                                               |    |

| Figure 4.32 - Layout of the plain 2-oft pulsed latch                                               |    |

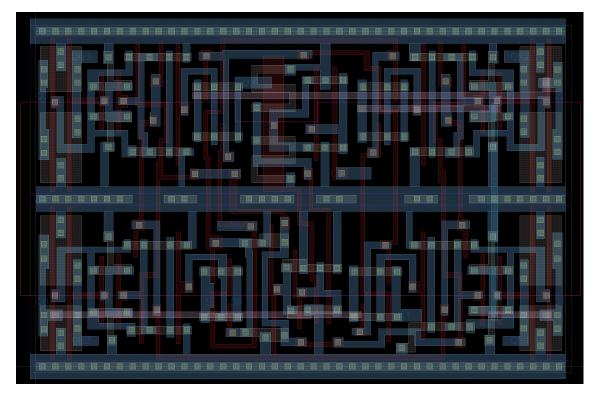

| Figure 4.33 - Layout of the plain 4-oft pulsed latch                                               |    |

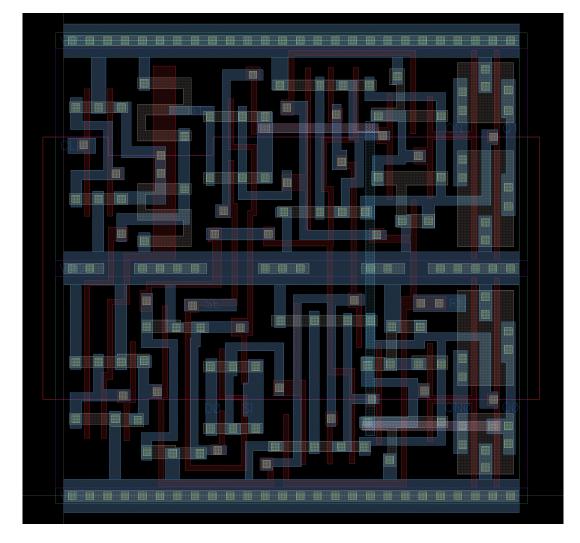

| Figure 4.35 - Layout of the reset 2-bit pulsed latch                                               |    |

| rigure 4.55 - Layout of the reset 2-oft pulsed laten                                               | 00 |

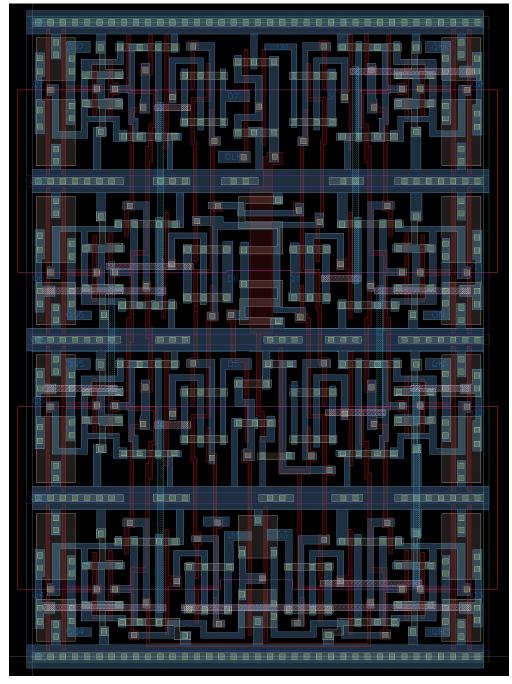

| Figure 4.36 - Layout of the reset 4-bit pulsed latch                                                       | 51 |

|------------------------------------------------------------------------------------------------------------|----|

| Figure 4.37 - Layout of the reset 8-bit pulsed latch                                                       | 52 |

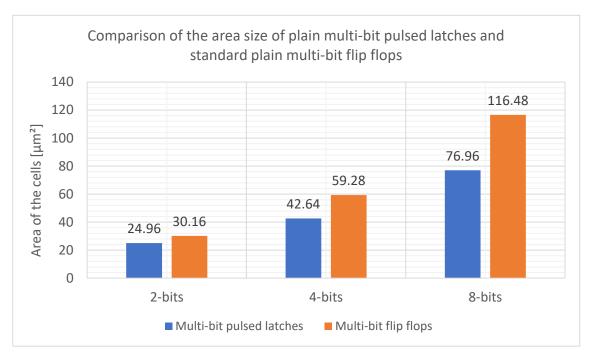

| Figure 4.38 - Graph of the comparison of the area size of plain multi-bit pulsed latches and standard plai | n  |

| multi-bit flip flops                                                                                       | 65 |

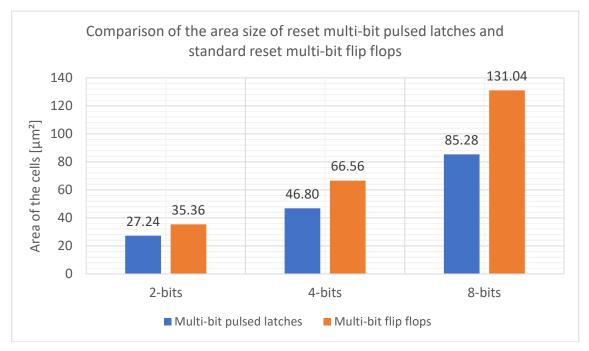

| Figure 4.39 - Graph of the comparison of the area size of reset multi-bit pulsed latches and standard rese | t  |

| multi-bit flip flops                                                                                       | 65 |

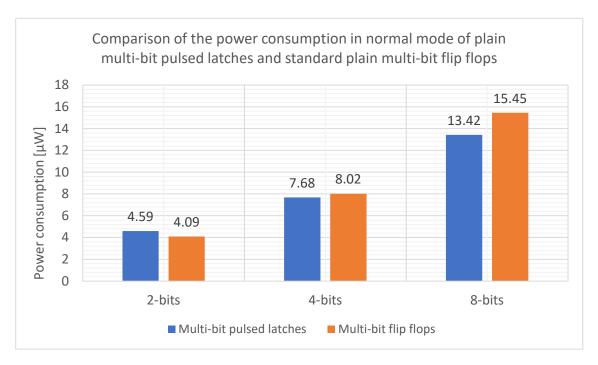

| Figure 4.40 - Graph of the comparison of the power consumption in normal mode of plain multi-bit           |    |

| pulsed latches and standard plain multi-bit flip flops                                                     | 56 |

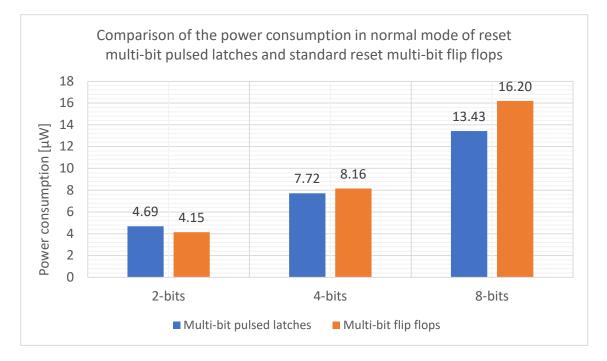

| Figure 4.41 - Graph of the comparison of the power consumption in normal mode of reset multi-bit puls      | ed |

| latches and standard reset multi-bit flip flops                                                            | 56 |

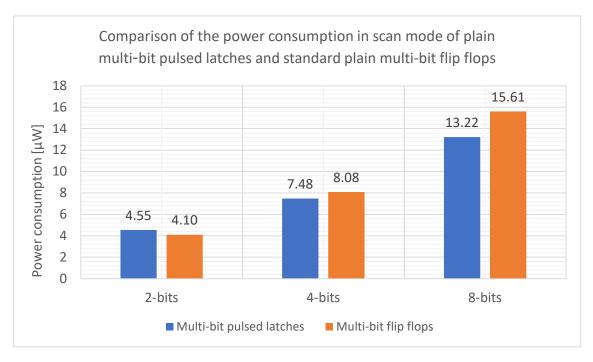

| Figure 4.42 - Graph of the comparison of the power consumption in scan mode of plain multi-bit pulsed      |    |

| latches and standard plain multi-bit flip flops                                                            | 67 |

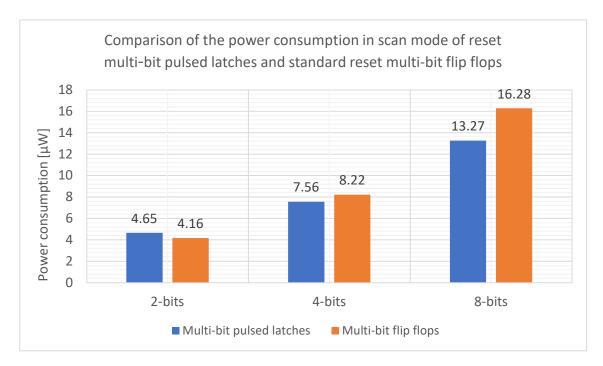

| Figure 4.43 - Graph of the comparison of the power consumption in scan mode of reset multi-bit pulsed      |    |

| latches and standard reset multi-bit flip flops                                                            | 67 |

## **TABLES**

| Table 1.1 - List of common cells in the digital standard cell library                                   | . 16 |

|---------------------------------------------------------------------------------------------------------|------|

| Table 1.2 - Truth table of an inverter                                                                  | . 18 |

| Table 3.1 - Different design levels with examples of low power techniques                               | . 24 |

| Table 3.2 - Binary and Gray code sequence                                                               | . 28 |

| Table 4.1 - Example of values from the graph in Figure 4.7                                              | . 33 |

| Table 4.2 - Parameters of simulated pulse generators                                                    | . 36 |

| Table 4.3 - Table of specific cross corners                                                             | . 38 |

| Table 4.4 - Parameters of special simulated pulse generators                                            | . 38 |

| Table 4.5 - The comparison of latches controlled by pulse                                               | . 41 |

| Table 4.6 – Maximal frequency dependence on the number of bits                                          | . 49 |

| Table 4.7 - A comparison of the 2-bit pulsed latch and the 2-bit flip flop                              | . 54 |

| Table 4.8 - A comparison of the 4-bit pulsed latch and 4-bit flip flop                                  | . 55 |

| Table 4.9 - A comparison of the 8-bit pulsed latch and 8-bit flip flop                                  | . 55 |

| Table 4.10 - Measured power consumption of the multi-bit pulsed latches in normal mode                  | . 63 |

| Table 4.11 - Measured power consumption of the multi-bit pulsed latches in scan mode                    | . 63 |

| Table 4.12 - Measured area of the designed multi-bit pulsed latches                                     |      |

| Table 4.13 - Maximal usable frequency of the multi-bit pulsed latches                                   | . 63 |

| Table 4.14 - Overview of the measured parameters in designed multi-bit pulsed latches                   |      |

| Table 4.15 - Overview of parameters in standard multi-bit flip flops                                    | . 64 |

| Table 4.16 - Table of area comparison of multi-bit pulsed latches and multi-bit flip flops              | . 68 |

| Table 4.17 - Table of power consumption of multi-bit pulsed latches and multi-bit flip flops in normal  |      |

| mode                                                                                                    |      |

| Table 4.18 - Table of power consumption of multi-bit pulsed latches and multi-bit flip flops in scan mo | ode  |

|                                                                                                         | . 68 |

| Table 4.19 - Used parameters in a simple design simulation                                              |      |

| Table 4.20 - Measured power consumption of 64-bit shift register                                        | . 71 |

| Table 4.21 - Measured area size of the 64-bit shift register                                            | . 71 |

## INTRODUCTION

At this moment we are living in a phase in which we should start thinking about the future of the Earth more than ever before, since the carbon footprint is worse than ever. The carbon footprint is causing global warming which makes the planet warmer and warmer. Global warming is not caused only by carbon footprint but also by other greenhouse gases. At this moment, these gases are mainly produced by industrial and automotive end markets, but they are also made when the energy is generated by not re-usable resources - like coal. Many companies these days are promising to do something about it - like onsemi. The company onsemi has said it will achieve zero-net emissions by 2040 [12].

Energy demands are getting worse every year because many things must be supplied with power. Automotive markets also include chips that are developed for automotivespecific applications. These chips have a significant power consumption. What is more, when there are put together, the power consumption is even bigger. Nowadays, a modern car contains several hundreds of chips. These chips can be developed in different technologies that have different power consumption, but these chips can be also developed with low power solutions or ultra-low power solutions that minimize power consumption. For example, handheld devices have limited power supplies, because they are powered by batteries. If the power consumption is not optimized, the battery life will be short. What is more, the size of the battery would have to be huge. Both negative cases are unwanted.

At the beginning of this thesis, there is a short introduction to CMOS technology, where the basics of the technology are explained. There is also an explanation of where CMOS chips can lose power. The CMOS technology is the most used technology for chips. There will be a description of methods that can be used to reduce the power and area of application-specific integrated circuits (ASIC). The digital part of the chips is made of a standard library of digital cells also known as building blocks. Digital standard cell libraries are explained too. A multi-bit pulsed latch can be included into digital standard cell libraries. This pulsed latch can be used as a better replacement for standard multi-bit flip flops that have bigger area and power consumption.

The multi-bit pulsed latch is composed of a pulse generator and a latch that can be driven by pulse. The aim of this work is to choose a pulse generator and a latch topology for application in 65 nm CMOS technology with a specification mentioned in an assignment:  $\pm 10$  % of power supply, temperature range from -40 °C to 150 °C, and an option to have a scan input. There should also be a version of the multi-bit pulsed latch with and without a reset pin. The pulse generator and pulsed latch topologies have different results that will be explained. From a chosen pulse generator and a pulsed latch, a multi-bit version with scan can be built. Multi-bit cells are often designed in 2-bit, 4-bit and 8-bit versions. If a multi-bit pulsed latch has more bits, the savings are bigger.

These multi-bit pulsed latches are firstly simulated from the schematic netlist to get knowledge about functionality. The simulation is running in different process corners, voltages, and temperatures (PVTs) that were mentioned before. The most problematic circuit is the 8-bit pulsed latch with a scan input because the pulse has the biggest load and the pulse needs to be in a specific range which is dependent on the technology, used topology of the latch, and the point where the scan is connected to the next latch. The results of power consumption and estimated area of all designed multi-bit pulsed latches simulated from the schematic are compared with standard multi-bit flip flops. The most time-consuming part of this development is designing layouts from schematics. These layouts can be simulated too, but the advantage is that the parasitic extraction can be run. The parasitic extraction can extract netlist with parasitic elements which can be later simulated. At the end of this work, designed layouts of multi-bit pulsed latches are compared to standard layouts of multi-bit flip flops and then they are also tested in a simple design.

## **1. CMOS TECHNOLOGY**

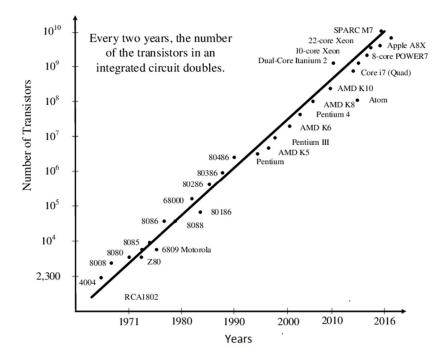

The first working transistor was invented in 1947 by American physicists John Bardeen and Walter Brattain. Since 1947 a lot of research was done. The research has had a great influence on today's devices. Today's transistors are part of integrated circuits, small electronic parts developed for a special purpose. These transistors can be of different types, but CMOS transistors are most used inside integrated circuits instead of bipolar transistors because the CMOS transistors are faster, have smaller power consumption, and have a smaller area on-chip. It needs to be mentioned that the first integrated circuit was invented in 1959 by Robert Noyce, because a few years later - in 1965 - American businessman and co-founder of Fairchild Semiconductor, Gordon Moore, predicted doubling of transistors every year in integrated circuits. The actual trend is shown in Figure 1.1. This prediction is called Moore's law [3].

Figure 1.1 - Number of transistors in integrated circuits in dependence on years [7]

#### **1.1 Fundamentals of CMOS transistors**

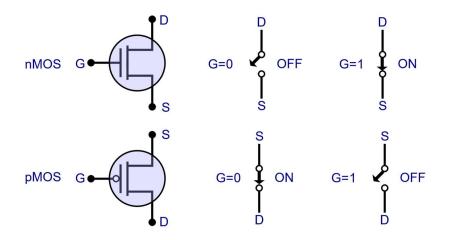

As it was mentioned above, the CMOS transistors are often used in integrated circuits because of their advantages in comparison with bipolar transistors. CMOS stands for a complementary metal-oxide-semiconductor. The word 'complementary' means that two types of transistors complement each other as transistor type N channel and P channel. Their schematic symbols and functions are shown in Figure 1.2. Figure 1.2 shows a schematic symbol with 3 pins: D (drain), G (gate), and S (source). In chip development,

there is also another pin called B (bulk) which is the substrate of the transistor. The gate is the pin which is controlling the state of the transistor as it is shown in Figure 1.2. The metal in the name stands for gate contact which is made of metal in modern chips. The space under the contact is made of polysilicon and in short term, it is called a poly. This contact is insulated by oxide as it is shown in Figure 1.3. Silicon dioxide also known as  $SiO_2$  is often used as oxide. In today's technology, the thickness of this insulator is about a few atoms which makes these devices vulnerable to electrostatic discharge (ESD), because even a small electrostatic charge can break the gate. The last part of the name stands for semiconductor because the transistor is made of semiconductor material [3].

Figure 1.2 - Symbol and functions of NMOS and PMOS transistors [9]

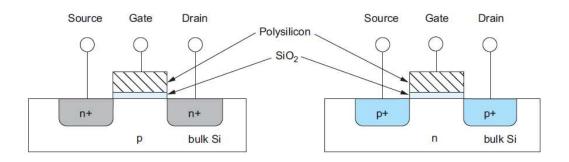

Figure 1.3 - The side view of NMOS (left) and PMOS (right) transistors [3]

The structure of the CMOS technology is shown in Figure 1.3, there is a NMOS transistor (left) and a PMOS transistor (right). It is important to state that NMOS and PMOS work differently, and their parasitic features are different. When comparing both transistors of the same size, the NMOS transistor will be faster with lower leakage than the one with the PMOS transistor. The leakage will be explained in the next chapter. On the other hand, the PMOS transistor is more immune to noise than the NMOS transistor.

The application for both transistors is specified by the negative and positive features, for example, the NMOS transistor with smaller leakage can be used as a standard cell called a fill capacitor in digital libraries.

## 1.2 Digital standard cell library

Digital standard cells are an irreplaceable part of automotive-specific applications. Digital standard cells are well-defined cells that can be used in a design as building blocks [18]. These cells have different views that can represent different functions like schematic, layout, symbol, verilog, liberty, and others [3]. These building blocks are also pre-characterized to save time when they are used in a bigger design. These data of the

cells for the whole library; like maximal load, input capacitance, and others, are stored in liberty to make more complex simulations faster. Many types of digital standard libraries can be found in the technology; it depends on the or requirements from customers. application The performance of the libraries is given by the height of the cells. The digital standard library has all cells with the same height because these cells can be easily connected to power rails and can be easily used with the automatic place and route tool [18]. Digital libraries can be often developed as high-density (HD) or high-speed (HS). High-speed libraries have greater height, larger speed, and bigger power consumption than high-density libraries. The width of the cells is given by the complexity of the cell, but the width of the cell should be minimized to achieve a maximal density of the design. These libraries can be also designed with different models of the transistor that have different threshold voltages [3].

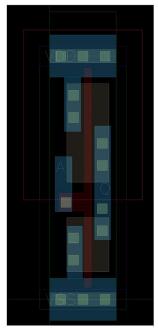

Figure 1.4 - Layout of inverter in 65 nm technology

The simplest cell is shown in Figure 1.4. It represents a simple layout inverter that is composed of two transistors. The height of these transistors in Figure 1.4 is not the same because the PMOS transistor is slower than the NMOS transistor with the same height as it was mentioned. The height ratio of both transistors is given by the technology. These libraries can be composed of many types of common cells. The list of often designed cells is shown in Table 1.1. These libraries can be also enriched with special digital standard cells that can have better power consumption, area, special purpose, or even performance. The following parts can be considered as digital standard cells: a level shifter, power-down cell, isolation cell, state retention flip flop, dual or multi-bit flip flops, dual

edge-triggered flip flop, low swing dual edge-triggered flip flop, and a multi-bit pulsed latch. This study is primarily focused on multi-bit pulsed latches [3].

| Name of cell             | Description of the cells                                        |

|--------------------------|-----------------------------------------------------------------|

| BUF, INV, AND, OR, NAND, | Simple logical functions with multi-inputs and different        |

| NOR, XOR, XNOR           | output strengths                                                |

| HALF / FULL ADDER        | 2-bit half or full adder with different output strengths        |

| MUX / DEMUX              | Multiplexer or demultiplexer with different output strengths    |

| ECO CELLS                | Universal cells that can be used in case of need                |

| AOI / OAI                | Multi-input and/or or or/and logical combination                |

| FLIP FLOPS / SCAN FLIP   | Flip flops (plain, reset, set) with different output strengths, |

| FLOPS                    | scan flip flop can be used as a shifter                         |

| LATCHES                  | Flip flop controlled with level                                 |

| FILLER / FILLCAP         | The cell can connect power rails or can be used as              |

|                          | decoupling capacitances                                         |

| DELAYS                   | Used for compensation of STA violations                         |

| CLOCK GATING CELLS       | Used to synchronize the clock signal                            |

Table 1.1 - List of common cells in the digital standard cell library

Digital standard cell libraries can be designed in each technology, where there may be different libraries in the technology with different uses as it was mentioned. The technology specifies the minimum length of transistors that can be used in the library. With passing years, people are making smaller and smaller transistors. Currently, the lowest technology is 3 nm [13]. The used technology in this thesis is 65 nm from onsemi company.

The reason, why the size of the technology is moving down, is simple. If the size of the transistor is smaller, used power supply voltage can be lower as well. It means that the power consumption is lower too. Also, the maximal possible frequency can be higher. The density is also higher, which means the amount of the used material is decreased. What's more, more chips can be made on the same size of a wafer than before. That is the main reason why the CMOS technology is moving forward. The smaller technology has also some problems. One of the disadvantages of the small technology is the cost of development and manufacturing - smaller technology requires more advanced processes. The problem of small technology is the leakage power which is more significant in smaller technology than in bigger technology. The leakage will be explained in more detail in the next chapter because it is linked with power consumption. With smaller technology, the ESD problem and the electromigration are more complicated for the price of higher density and performance [3].

#### **1.3 Parameters of CMOS transistors**

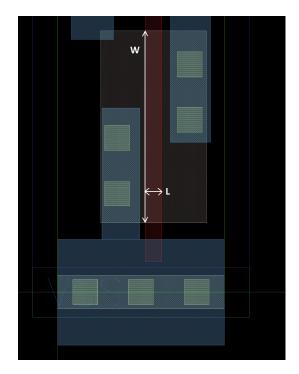

Transistors have four main parameters: one stands for W (width), the second stands for L (length), the third stands for n (number of fingers) and the last stands for m (multiplier). The last two are not common in digital standard cells. They are often used in analog CMOS circuits. The first two parameters are shown in Figure 1.5. These parameters define the size of the area under the gate (polysilicon) contact. Also, some parameters can be given by technology. For example, parasitic parameters as resistance or capacitance are both dependent on the size of the gate.

Figure 1.5 - Zoomed NMOS transistor from inverter cell with parameters of the transistor

As it was mentioned, the simplest standard cell in CMOS technology is an inverter, which represents a logical function called negation. The inverter has one input and one output. The truth table is shown in Table 1.2. The inverter is made of two transistors: NMOS and PMOS. The schematic and layout of the circuit are shown in Figure 1.6 and Figure 1.4. This circuit needs to be explained because the next chapter describes the power consumption in CMOS technology on this cell. That is why an understanding of this circuit is necessary. The layout is shown because there are layers that need to be explained and will be shown later in more complicated layouts.

The blue layer represents the metal one (M1) that is used for internal routing. Yellow boxes represent contacts (CO) between the active and metal one (M1). The beige layer represents an active which is an actual transistor. The top beige rectangle represents

PMOS, and the bottom beige rectangle is NMOS. The PMOS is bigger, because as it was mentioned, if both transistors had the same size, the PMOS would be slower. The last explained layer is red, which is crossing both actives. It is the poly (polysilicon) that represents the gate of the transistors. The size of the transistor is given by the size of the poly. Other layers are not important, because they are just technology layers. Colors in the layout are not important too, because every company or technology has its own colors of layers.

| Input (A) | Output (Q) |

|-----------|------------|

| 0 (Low)   | 1 (High)   |

| 1 (High)  | 0 (Low)    |

Table 1.2 - Truth table of an inverter

A MNI1 Vdl.\*

Figure 1.6 - The schematic of an inverter

## 2. POWER CONSUMPTION IN CMOS TECHNOLOGY

The power consumption in CMOS technology is a big issue nowadays. Devices with CMOS chips can be divided in two groups. One group has batteries, and the second group is powered from an outlet. Devices powered by batteries are limited by the capacity of the battery. If the power consumption is optimized in the case of handheld devices, the size of the battery can be smaller, and the device can last longer than before in the unoptimized state. If batteries last longer, it results in a better environment too, because batteries cannot be recycled efficiently. Devices powered by the outlet need to be optimized for power consumption too because if no one cares about power consumption at this moment, people in the future will have a big problem with energy consumption. After all, power stations will not be able to generate enough energy. With smaller technology, the power consumption decreases, and the performance of the chip is increased.

Before low power solutions can be shown, the cause of power consumption and its components need to be explained. The power consumption can be divided into two main groups: dynamic power and static power. The dynamic power is caused by flipping circuits as switching power and short-circuit power. The static power refers to leakage power. Each power consumption has its own parasitic features, that can affect the results of the power consumption. The total power consumption is given by equation (2.1) [3].

$$P_{total} = P_{switching} + P_{short-circui} + P_{leakage}.$$

(2.1)

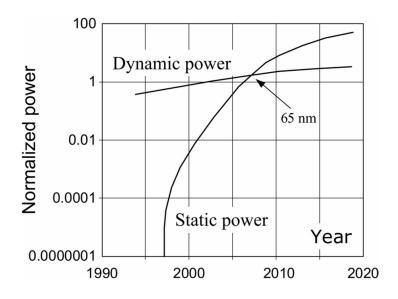

Figure 2.1 - Dependence of normalized power on years [10]

Components of the total power consumption are not of the same size for all technology processes as it is shown in Figure 2.1. As the years were passing by, the technology processes have changed but so have the magnitudes of dynamic and static power. As the years go on, the dynamic power increases slightly, but static power increases significantly. Static power becomes dominant when the technology reaches the 65 nm process, which is the case of this thesis. It needs to be dealt with [10]. Causes of the power consumption of each component will be explained on the inverter shown in Figure 1.6 in the following subchapters. Afterwards, it can be shown how to decrease power consumption with lower power techniques.

#### 2.1 Switching power

Switching power is caused by charging and discharging of capacitances node where the output is. The capacitance node mainly includes gate, overlapping, and interconnection capacitance. That is a reason why the layout needs to be designed precisely to minimize parasitic elements. The switching power can be expressed as equation (2.2):

$$P_{switching} = \alpha \cdot C_L \cdot f \cdot V_{DD}^2, \qquad (2.2)$$

where  $\alpha$  is the switching activity factor of the clock, C<sub>L</sub> is the capacitance load connected to the output stage, f is the frequency of the clock and V<sub>DD</sub> is the power supply voltage of the cell. The equation shows that the switching power depends on several quantities that are easily observable and measurable in CMOS circuits. These parameters need to be tailored to the application. Frequency and voltage do not need to be used with high value if the circuit performance does not require it. The typical switching activity factor of the clock is used as 0.5 which is equal to 50 % of the duty cycle. In a special application, the switching activity factor can be changed. The capacitive load needs to be optimized to the minimum possible value to reduce the switching power, which depends on the layout and output load. The switching power can be optimized with methods that can change the parameters in equation (2.2) [5].

#### 2.2 Short-circuit power

In digital CMOS circuits, there are always two complementary networks as p-network (pull-up) and n-network (pull-down). The inverter can be used as an example for the explanation as it is shown in Figure 1.6. Normally, when the input and output states are stable, only one transistor is turned on and conducts the output either to the power supply voltage node or to the ground node. The other network is turned off and blocks the current from flowing. There is also a transition state which is called short-circuit. The short-circuit

exists when switching to another state from a low logical state to a high logical state and vice versa when both transistors are half-opened. There is a short time interval, where both transistors are half-opened. The current flows through both types of transistors from the power supply to the ground. The short-circuit power can be expressed as equation (2.3):

$$P_{short-circuit} = I_{SC} \cdot V_{DD} \cdot f, \qquad (2.3)$$

where the  $I_{SC}$  is the short-circuit current that is caused by short-circuit,  $V_{DD}$  is the power supply voltage and f is the switching frequency. Parameters of equation (2.3) such as supply voltage and switching frequency need to be optimized because if the circuits do not need to be fast, the applied voltage and frequency can be lower, which helps to reduce power consumption. Dynamic power is the sum of switching and short-circuits power. Dynamic power is more significant for technologies larger than 65 nm as it is shown in Figure 2.1. For smaller technologies than 65 nm, dynamic power is less significant compared to the static power of the whole chip due to the leakage which will be explained in the next subchapter [3].

#### 2.3 Leakage power

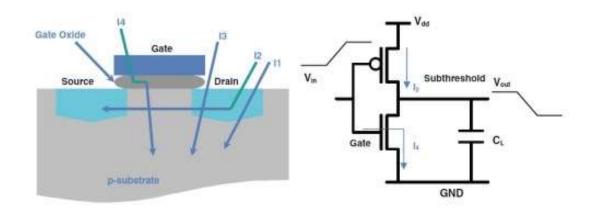

The static power of the whole chip becomes dominant when the process technology reaches 65 nm which is exactly what this thesis deals with. Even turned-off transistors can consume some amount of power. This power loss is called leakage, which can be caused by a variety of problems. Several causes will be explained in this subchapter to give a basic idea of leakage power. As it was stated earlier, the leakage power is dependent on technology. With lower technology, the leakage is more dominant than the dynamic power as it is shown in Figure 2.1. For nanometer devices, leakage current is dominated by subthreshold leakage, thin-oxide tunneling leakage, and reverse-bias pn-junction leakage. There are still other leakage components like drain-induced barrier lowering and gate-induced drain leakage, but these are not important, because they are not significant in comparison with these three dominant leakages. These dominant leakages are shown in Figure 2.2. The leakage power cannot be simply expressed as in the case of dynamic power or short-circuit power, because the leakage is caused by many variables, but leakage power can be expressed as a function of many variables (2.4):

$$P_{leakage} = f\left(V_{DD}, V_{th}, \frac{W}{L}, T\right), \tag{2.4}$$

21

where the VDD is the power supply voltage,  $V_{th}$  is the threshold voltage of the transistor. W/L is the size of the transistor, when W is width, L length and T is the temperature in kelvins. Switching power and short-circuit power have a frequency as a variable in equations (2.2) and (2.3). Dynamic power dissipates in cycles, but the leakage power due to an absence of frequency in function (2.4) is continuous. That is the reason why the leakage is also called static power [3].

Figure 2.2 - Leakage components are shown in layout and schematic (I1 – Diode reverse bias current, I2 – Subthreshold current, I3 – Gate-induced drain leakage, I4 – Thin-oxide tunneling leakage) [11]

#### 2.3.1 Subthreshold leakage

The subthreshold leakage current  $I_{SUB}$  is a current which can flow between drain and source if the transistor is in weak inversion. A weak inversion occurs when the gate to source voltage  $V_{GS}$  is smaller than the threshold voltage  $V_{th}$  of the transistor. This current is happening because in the area between drain and source is a small amount of minority carrier concentration which can let the current through a drain to source. This leakage current is dependent on parameters of the transistor as is the power supply voltage, width, length, process, temperature, and type of the transistor. The reduction of this leakage current can be made with special topologies. For example, a standard inverter (inverter based on 2 transistors) can be replaced with a stacked inverter (inverter based on 4 transistors). Topology can be a good solution for subthreshold leakage reduction; but at the cost of the area of the cell. The subthreshold conduction can be used as an advantage. For example, it can be used in ultra-low power analog circuits, especially in dynamic random-access memories (DRAM) [3].

#### 2.3.2 Thin gate-oxide tunneling leakage

The silicon dioxide (insulator) between active and gate contact is thin, circa a few atoms in modern technologies. Due to the thickness of the insulator, there can be two types of leakages found. The first current leakage is called thin gate tunneling  $I_{TUNNEL}$ . The thin gate tunneling current is generated due to carries that are tunnelling through the thin insulator. The second one is known as hot carrier injection current  $I_{HC}$ . The cause of hot carrier injection current is the massive kinetic energy of carries which can overcome the gate potential barrier and go through the thin insulator. This effect is more usual to happen to electrons because their voltage barrier and effective mass are smaller than for holes [4].

#### 2.3.3 Reverse-bias pn-junction leakage

The last explained type of leakage is reverse-bias pn-junction leakage, which is caused by the structure of the CMOS transistor. In the structure of the CMOS transistors, shown in Figure 2.2, there are p-n junctions created between the active and the substrate. This pn-junction acts like a well-formed diode. Even if this diode is reverse-biased, the current flowing through is significant, because the reversed-biased diode still conducts a small amount of current I<sub>D</sub>. This reverse-bias diode current can be expressed as equation (2.5):

$$I_D = I_S \left( e^{\frac{V_{DB}}{V_T}} - 1 \right), \tag{2.5}$$

where  $I_s$  is reverse saturation current (parameter for the device),  $V_{DB}$  is the voltage between the drain and the body of the transistor and  $V_T$  is the thermal voltage which depends on temperature. For room temperature (T = 300 K) the value of  $V_T$  is 26 mV. Also, the thermal voltage can be expressed as equation (2.6):

$$V_T = \frac{kT}{q},\tag{2.6}$$

where the k is Boltzmann constant ( $1.38 \cdot 10^{-23}$  J/K), T is the absolute temperature in Kelvin and q is the electron charge [4].

## **3. LOW POWER TECHNIQUES**

The price of the chip is based on many things like the complexity of design, technology, size, performance, reliability, and power consumption. These parameters can be adjusted to the application, but this chapter will explain, how to reduce the power consumption. Power consumption is important in nanometer-scale devices because the power density is high. Power density can be decreased if the power consumption is lower. The high-power dissipation can cost a lot of money because the package of the chip will cost a lot too [3].

Low power techniques are supposed to reduce power consumption. A combination of low power techniques can be used to reduce power consumption to minimal value because different techniques can reduce only specific power consumption, like dynamic or static power. Low power techniques can increase the area of the cell or worsen another parameter of the circuit. There are a lot of techniques that can be used in application-specific integrated circuits. These techniques can be also divided into different levels of chip development as it is shown in Table 3.1. All design levels will be explained in the following subchapters [3].

| DESIGN LEVEL           | STRATEGIES                                                                                                                                                                                                                                                                    |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SYSTEM OR CHIP         | partitioning, power-down, clock tree optimization (clock<br>gating), level shifters, always-on cells, substrate biasing<br>or adapting back biasing, and sleep or standby mode                                                                                                |  |

| PLACE AND<br>ROUTE     | placement/floorplan (reduce physical capacitance and<br>resistance), optimizing, buffering, routing, on-chip<br>power distribution, and glitch power                                                                                                                          |  |

| ALGORITHM              | parallelism and pipelining                                                                                                                                                                                                                                                    |  |

| ARCHITECTURE           | voltage scaling, frequency scaling, clustered voltage<br>scaling, adaptive voltage scaling, low swing clock, low<br>swing clock double-edge triggered flip flop                                                                                                               |  |

| LOGIC                  | data coding/encoding and operand isolation                                                                                                                                                                                                                                    |  |

| TECHNOLOGY             | threshold reduction and multi-threshold devices                                                                                                                                                                                                                               |  |

| CIRCUIT OR<br>TOPOLOGY | transistor sizing, longer channel in non-critical paths in<br>small technologies, best topology, pin swapping, special<br>circuits as state retention flip flop, dual or multi-bit flip<br>flops, dual edge-triggered flip flops, pulsed latch, and<br>multi-bit pulsed latch |  |

Table 3.1 - Different design levels with examples of low power techniques

### 3.1 System

The system-level should mainly provide information about the specification of the chip like voltage distribution. Chip developers can retrieve useful information from the specifications and can state which methods can be used for the best performance of the chip. There are many techniques how to make a better performance, for example, the chip can be divided into different blocks. These divided blocks can be powered with different power supply voltage depending on demands from the block because some parts of the chip do not need to be fast. The lower voltage of the block can reduce power consumption as it is shown in equations (2.2), (2.3), and (2.4) but at the cost of slower performance. The decision of what supply voltage the block will have depends on the application. Level shifters, which can change the levels of the signal, are used between blocks with different power supply voltages [3].

There may be parts of the chip that do not need to be on all the time, on the other hand, there may also be parts of the chip that need to be on all the time. Always-on cells can serve as an example, because they are turned on all the time. As it was explained in the chapter before, there is some standby power consumption which is significant in today's power consumption of the whole chip. A block or cell that does not need to be powered at a precise time can be turned off using two transistors connected between the power supply and the block and ground. It saves power consumption, but the area is increased because there were two transistors added to turn off the block. However, the design is becoming more complex.

The designer needs to place isolation cells between active and inactive blocks to reduce ticking especially in the clock path. This method is called clock tree optimization and it can save a lot of dynamic power consumption across the chip. In ultra-low techniques, substrate biasing or adapting back biasing can be used to reduce leakage if it is necessary. It means that the bulk of the transistors can be connected to a different voltage than typical  $V_{DD}$  or GND [15].

#### 3.2 Place & Route

Place and route are important steps in the chip development. This step can make difference between a good chip and a bad one because the correct placement of the cells can reduce parasitic elements such as resistance, inductance, and capacitance. Cells should be organized as a group of cells that need to be close to themselves because the routing can add parasitic elements too.

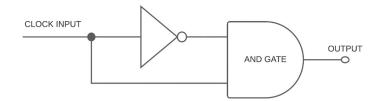

If the routing is not optimized, the size of the chip can be increased, because more buffers are needed than in the optimized state. On-chip power distribution is how the grid of rails with supply voltage will look. Power voltage distribution needs to be also optimized for application because it can help with voltage drop and performance of the chip. Unwanted glitch needs to be fixed too because it is causing more dynamic power consumption. However, the output is changed in a short time and without purpose. These glitches can be fixed with an additional simple logical gate that does not change the final logical function. The glitch can be also known as a hazard in combination with logical circuits. The simplest glitch generator can be made with two logical gates, an inverter and AND gate. The circuit is shown in Figure 3.1 [3].

Figure 3.1 - Example of AND glitch generator

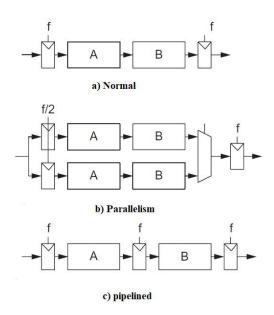

## 3.3 Algorithm

The algorithm has a large impact on power consumption. Pipelining and parallelism can be used as the algorithm. These methods can be used in a combination to achieve a maximal reduction of power consumption. Pipelining can also reduce the critical path, and increase the clock speed, or sample speed. Parallelism is used for increased sample speed and reduction of power consumption. The used circuit is duplicated and connected in parallel to the original circuit with a multiplexer connected to the end of both parallel circuits. Circuits can work with half of the frequency than before, but the multiplexer needs to be controlled with the original frequency to control the output correctly. Both methods can be used separately but for the best efficiency, methods should be used together. Both methods are shown in Figure 3.2. The biggest disadvantage of these techniques is the increased area of the circuit. On the other hand, this leads to lower power consumption [3].

Figure 3.2 - Differences between (a) normal, (b) parallelism, and (c) pipelined circuit [3]

#### 3.4 Architecture

The architecture is like a system, but it has more advanced techniques. As it is written in the system subchapter, the parts (blocks) of the chip can be powered with different voltages. In the case of the system, this voltage is fixed. In architecture, the voltage can be decreased or increased according to the desired performance of the block in time. This technique is called voltage scaling. The application can change the voltage between 3 fixed voltages like fast, typical, and slow performance. The fast performance corresponds with higher voltage. The typical performance is a nominal voltage which is placed between fast and slow performance. The slow performance corresponds with a lower voltage than the nominal one. If the performance is needed to be high, the voltage can be increased depending on the application. Also, if it is not needed to have high performance, the voltage can be lower, and the circuit can save some power consumption. The voltage is changed automatically by the chip [16].

A more advanced technique of changing voltage is called adaptive voltage scaling, which is like voltage scaling, but the voltage can be changed linearly from minimal to the maximal value given by the circuit. The frequency can also be changed depending on the desired performance. The frequency of the clock can be reduced if the chip does not need to be fast and the circuit can save power consumption because the frequency is variable in dynamic power consumption. The frequency can be increased or decreased as it is with voltage. The frequency scaling can be made with a divider to have some fixed values, or the frequency can be adaptive. Adaptive frequency scaling can be scaled linearly [3].

Digital combination logical circuits are often controlled by the rising edge. In special applications, the circuit can be triggered by a falling edge or even with both edges. The circuits working on both edges are called dual trigger edge circuits. These circuits can change the output twice as much than standard circuits can. These are triggered only with one edge. For example, flip flops can be double edge-triggered, or they can even be double-edge triggered with a low swing clock source [3].

## 3.5 Logic

The coding and encoding need to be implemented correctly because different coding and encoding implementations can lead to different power consumptions and delays. For example, a 3-bit counter can be implemented using the binary counting sequence or the Gray code sequence. Both codes have different counting sequence results and number of toggled bits as it is shown in Table 3.2. The power dissipation is related to toggle activities, a grey code is generally more power-efficient than a binary code. This is the reason why logical code must be chosen correctly for low-power chips.

Operand isolation, which can reduce power dissipation in the data path, can be used in designs. The signal is controlled by enabling signal when the data path element is not needed to save power consumption [16].

| Bina     | ry code            | Gra      | y code    |

|----------|--------------------|----------|-----------|

| Sequence | Number of Security | Sequence | Number of |

| Sequence | toggles            | Sequence | toggles   |

| 000      | 3                  | 000      | 1         |

| 001      | 1                  | 001      | 1         |

| 010      | 2                  | 011      | 1         |

| 011      | 1                  | 010      | 1         |

| 100      | 3                  | 110      | 1         |

| 101      | 1                  | 111      | 1         |

| 110      | 2                  | 101      | 1         |

| 111      | 1                  | 100      | 1         |

Table 3.2 - Binary and Gray code sequence

#### 3.6 Technology

In every technology, there are transistors with different voltage thresholds like low voltage threshold (LVT), standard voltage threshold (SVT), and high voltage threshold (HVT). Different voltage thresholds of transistors lead to different results like speed and power consumption. Transistors with low voltage thresholds are faster with higher leakage than standard transistors are. These transistors are used when the circuit needs to be fast, and it does not matter how big the power consumption is. If the power consumption needs to be as lowest as possible, transistors with high switching threshold need to be chosen, because they have minimal leakage. However, at the cost of lower speed. The selection of transistors depends on the application [14].

## 3.7 Topology and Circuit

The topology of the circuit must be chosen carefully because different topologies always lead to different results; in area, power consumption, leakage, clock to output delay, and other parameters. The sizing of transistors is important too because the size of the transistor has a big impact on many parameters of the circuit. The size of the transistor means the width and length of the gate as it is shown in Figure 1.5.

Transistors with a bigger length of the gate are often used in critical paths because as it was explained before, transistors with a small length of the gate are leaking more than transistors with a longer length of the gate. Output stages are often created with transistors that have big width of a gate to have a possibility of driving a big load.

Pin swapping is also important because pins have different capacitances. Different capacitances are caused by the connectivity of the circuit and layout which can cause parasitic elements. For example, if two pins have different capacitances, the circuit should

better use the pin which has less capacitance, because the capacitance is a parameter for dynamic power consumption, and with less capacitance, the power consumption is also smaller.

Special topologies, like a state retention flip flop composed of two parts, can be used. The first part is a typical flip flop with a power voltage domain which can be turned off if the flip flop is not used. The second part of the state retention flip flop is internal memory which has its own power voltage domain that cannot be turned off. The memory can save the last data that can be used later. A flip flop can be used in multi-bit versions which can save area better than a single flip flop can. Special flip flops can also work for both edges. Multi-bit flip flops can be replaced with a more saving circuit like the multi-bit pulsed latch. The multi-bit pulsed latch is the main topic of this thesis which will be explained in the next chapter [3].

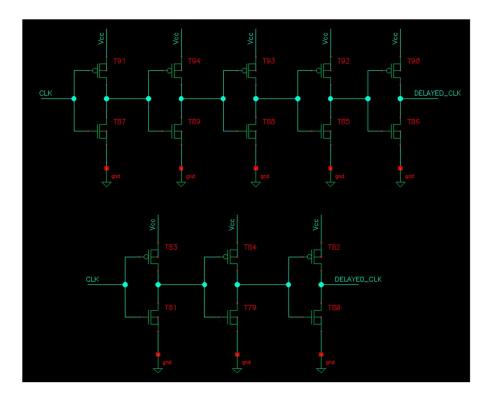

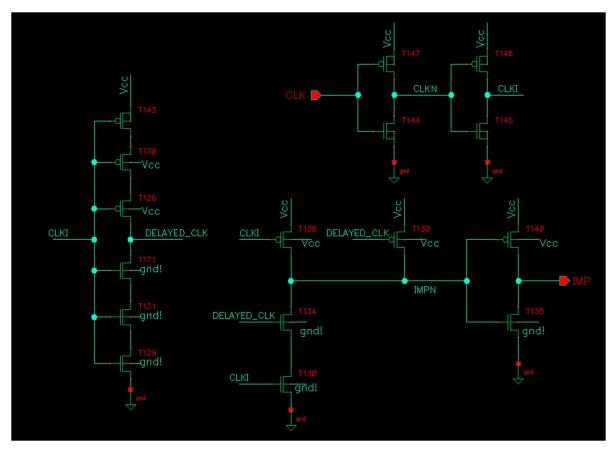

## **4. MULTI-BIT PULSED LATCH**

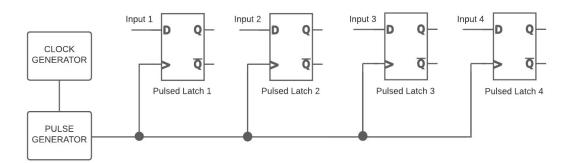

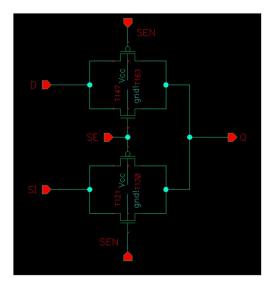

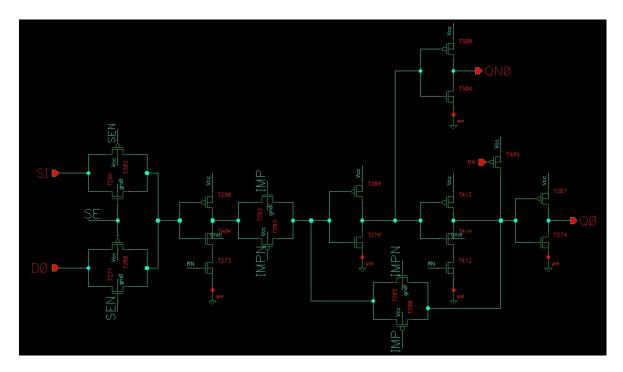

A multi-bit pulsed latch is a new solution for low-power libraries. In comparison with flip flops, multi-bit pulsed latches have a smaller area and a smaller power consumption. The multi-bit pulsed latch is composed of a pulse generator and pulsed latches shown in Figure 4.1 [3].

Figure 4.1 - Block diagram of multi-bit pulsed latch in normal mode

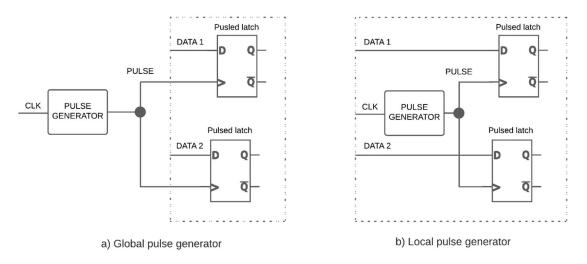

Multi-bit means that there is more than one latch that can be driven by one pulse generator. The pulsed latch is a simple latch that can be driven by a short pulse instead of a standard clock source. The latch driven by a pulse has the same truth table as the flip flop which means that the flip flop can be replaced by a pulsed latch. A pulse that is sufficiently wide enough is generated in a pulse generator. There are two possibilities for how the pulse generator can be developed as it is shown in Figure 4.2. The global pulse generator is developed separately from the latch and is used less frequently because of parasitic elements (longer routing than in the local pulse generator) and it is more complicated in place and route phase.

Figure 4.2 - Design of global and local pulse generator

The local pulse generator is a part of a multi-bit latch cell and is developed to cover all problems that can be found in the exact multi-bit pulsed latch. The layout of the multi-bit pulsed latch is developed as one cell which is better because the layout is created with minimal size and minimal additionally routing [2].

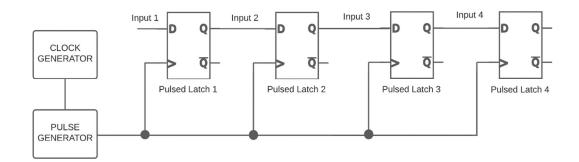

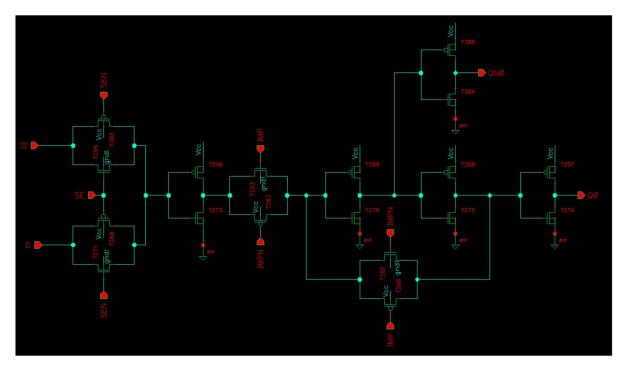

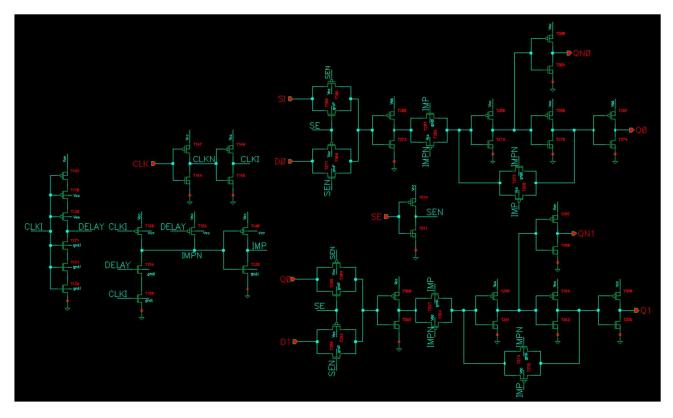

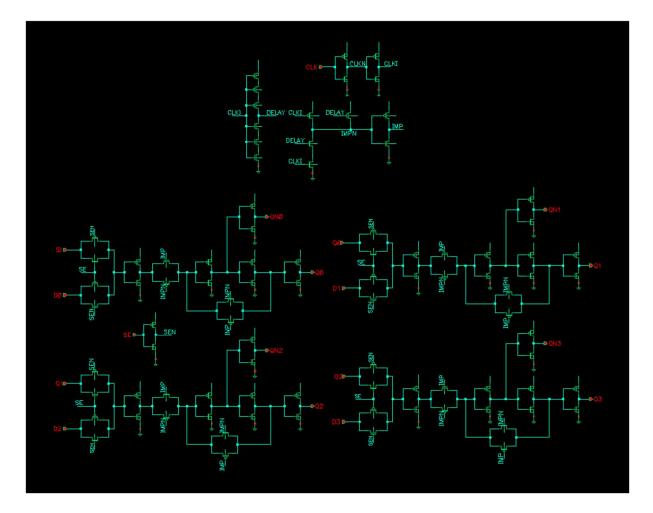

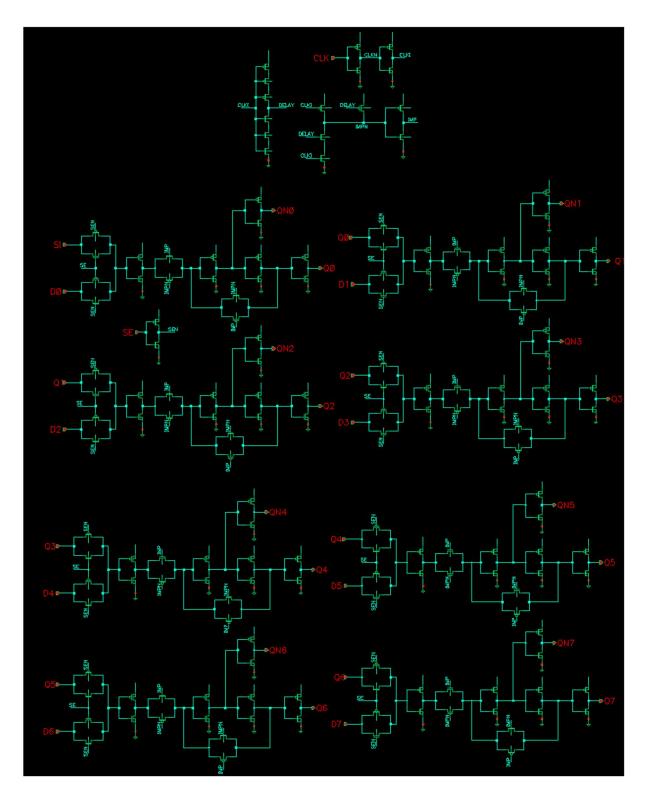

The specification of this thesis states that a multi-bit pulsed latch should work in scan mode. Scan mode is a mode where the output of the first latch is connected to the input of the next latch and the output of this latch is connected to the next latch input. This continues until the penultimate bit of the chain is connected to the last latch. This mode works as a shifter (serial memory) which is shown in Figure 4.3. Also, the circuit can be switched to normal mode where all inputs of latches can be used separately as it is shown in Figure 4.1. The switch is created as a multiplexer with two inputs (data and serial data) and one output. A multiplexer will be explained later because even multiplexers can be created differently which can lead to different results. Multi-bit versions are most often developed as 2, 4, and 8 bits with different output strength and additional functions like set, reset, or both. The practical side of this work is concerned with creating multi-bit pulsed latches with 2, 4, and 8 bits with reset pin and scan input. The area and power consumption savings should be most significant in the 8-bit version of the multi-bit pulsed latch.

Figure 4.3 - Block diagram of multi-bit pulsed latch in scan mode

#### 4.1 Pulse generator

As it was mentioned at the beginning of this chapter, the pulse generator can be developed as local or global. In the case of this work, there will be a pulse generator for local purpose designed. Many pulse generators can create different pulses but only one pulse generator must be chosen. Main differences between pulse generators are power, area of the cell, rising and falling times of edges, maximal load, the minimal and maximal activity of the clock, behaviors across the PVTs, and on what event is the pulse generated. Pulse can be generated for different events like rising, falling, or both edges.

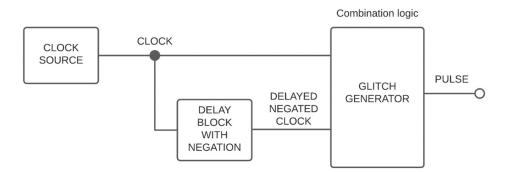

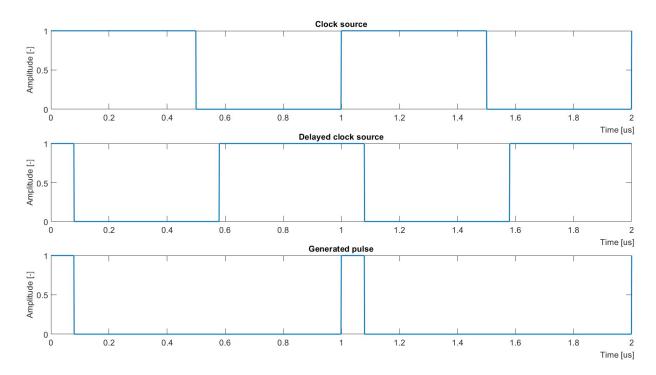

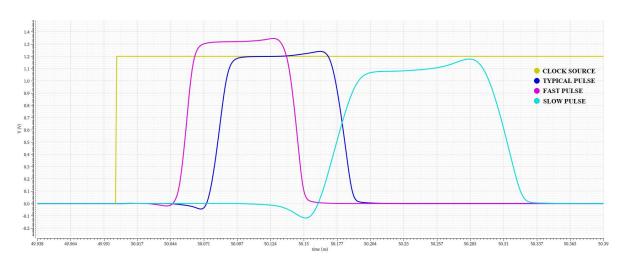

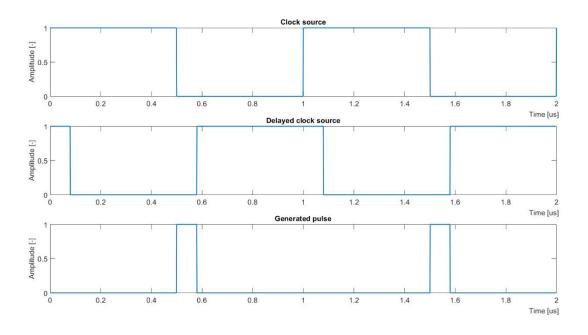

This chapter will be divided into two sections. The first subchapter will cover pulse generators that are suitable for this work and can be used. The second subchapter will cover pulse generators that are special and can be used in exact cases if the application needs it. The composition of the pulse generator is simple. The generator is composed of some combination logic which makes glitch (pulse) and the delay block with negation as it is shown in Figure 4.4. The width of the glitch is dependent on the delay between clock signals as it is shown in Figure 4.5 where the signals were simulated in MATLAB and based on the block diagram shown in Figure 4.4. The simulation is very simple because it does not include parasitic elements. The width of the generated pulse is dependent on the delay block. The width of the pulse will be different across technologies.

Figure 4.4 - Block diagram of the simple pulse generator

Figure 4.5 - Simulated block diagram from Figure 4.4 in MATLAB

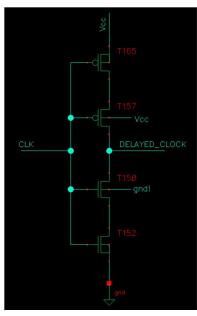

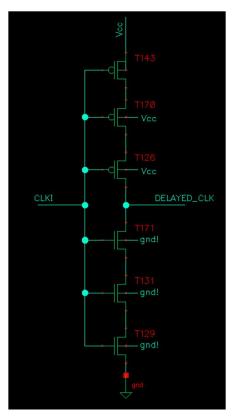

#### 4.1.1 Suitable pulse generators

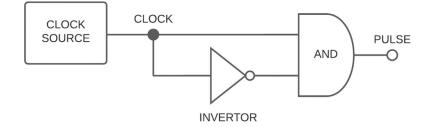

The aim of this thesis is to reduce power consumption and area of the cell in a comparison to a multi-bit flip flop. This means that the chosen topology of the pulse generator should be simple yet power efficient. This subchapter will be about pulse generators that generate a pulse on the rising edge of the clock signal. At a first sight, the most suitable circuit for the pulse generator seems to be a 2-input logical AND with an inverter in one of the inputs which makes the delay as it is shown in Figure 4.6. The combination logic which makes glitches is not too hard to find because there is just one option for the circuit to have those required parameters like the smallest possible area and power consumption. The AND logical gate is the most suitable combination logic that can be used.

Figure 4.6 - Simple pulse generator made of inverter and 2-input AND

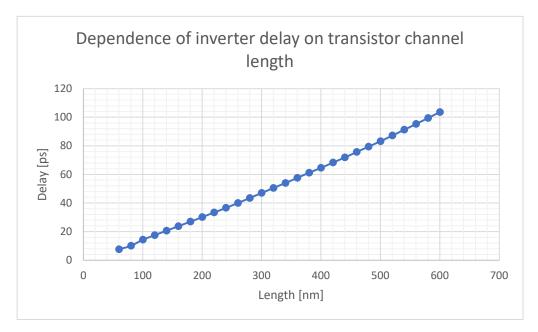

The main problem of the pulse generator development is the delay part that can also negate the clock source. Delay can be made in many ways, but every topology has different results. The simplest delay can be made with a standard inverter composed of 2 transistors as it is shown in Figure 4.6. The Delay of the inverter is dependent on the size of the transistors. As it was mentioned, the size of the gate can be changed with width and length parameters. The minimal width and length are given by technology. The delay of the inverter can be increased with decreasing width, but there is a minimal value of width that cannot be crossed. If the delay is not delayed enough to make the correct pulse, the length of the gate can be increased. A longer length makes the inverter slower, and the delay increases too. The delay dependent on the length of the simple inverter's channel is shown in Figure 4.7. A few values from the graph are shown in Table 4.1.

| Length [nm] | Delay [ps] |

|-------------|------------|

| 60          | 7.705      |

| 120         | 17.56      |

| 180         | 26.99      |

| 240         | 36.65      |

| 300         | 47.04      |

Table 4.1 - Example of values from the graph in Figure 4.7

Figure 4.7 - Graph of dependence of inverter delay on transistor channel length

The disadvantage of the simple inverter, for example of a delay block, is bigger leakage in comparison to other topologies. Leakage can be limited if different topology of the inverter is used. The better topology for the inverter is a stacked inverter that has lower leakage in comparison to a typical inverter, but the size of the cell is bigger. The stacked inverter is shown in Figure 4.8. A better solution is a double-stacked inverter as it is shown in Figure 4.9 [17]. There were opinions that more inverters with lower lengths can be used to make the delay bigger, but the power consumption is huge in comparison to other topologies. There is a simulated circuit with three and five inverters in serial shown in Figure 4.10.

Figure 4.8 - Stacked inverter

Figure 4.9 - Double-stacked inverter

Figure 4.10 - Five inverters delay (top) and three inverters delay (bottom)

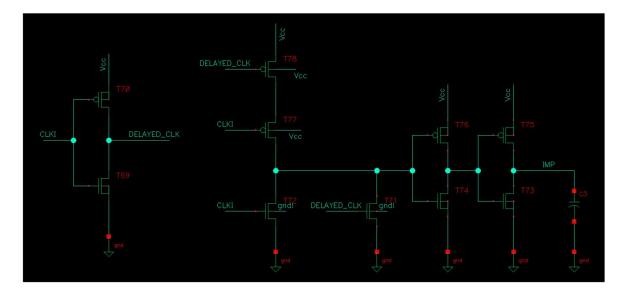

The measured data for all mentioned circuits are shown in Table 4.2. There were three basic parameters measured that are most important for this work; total power, leakage, and area of the cell. The width of the cell is not so important because the actual area of the cell can be different based on this prediction. Still, it needs to be measured to make sure the width of the cell is not so different from other values of pulse generators. The layout of the cell can be different because some tricks that can help to reduce the area can be used. The double-stacked inverter is expected to have the smallest size of the layout. Leakage in comparison to total power is not so significant but the leakage in the whole chip can be significant and there is a slight difference between topologies, so the leakage needs to be investigated. The five inverters delay leaks the most, which is caused by added inverters. Also, the leakage is increased in the case of three inverters delay. The best topology for leakage is a double-stacked inverter. The total power consumption is also increased if the inverters are added, similarly to the case of three and five inverters in comparison to a single inverter. That is the reason why three and five inverters delays cannot be used because they do not have any advantages. Also, the layouts of three and five inverters are expected to be bigger than other topologies because of design rules which need to be met. Total power was the lowest with double-stacked inverters.

| Type of delay           | Total power [µW] | Leakage [pW] | Width of delay [nm] |

|-------------------------|------------------|--------------|---------------------|

| Inverter                | 1.258            | 71.96        | 755                 |

| Three inverters         | 1.325            | 83.59        | 582                 |

| Five inverters          | 1.441            | 93.06        | 560                 |

| Stacked inverter        | 1.329            | 70.37        | 748                 |

| Double-stacked inverter | 1.229            | 68.28        | 666                 |

Table 4.2 - Parameters of simulated pulse generators

The chosen topology is a double-stacked inverter because the circuit has the best total power and leakage. The width of the cell is not the best but as it was said before, the width of the cell in Table 4.2 is just a prediction. At this point, the circuit looks like there can be tricks used to reduce the area of the layout more than in other topologies. The rising and falling edge in every circuit is similar because the output stage is the same size. The simulation is the same in all cases in terms of load, frequency, activity, and other parameters. The chosen circuit is shown in Figure 4.11. The output pulse of the pulse generator for typical, slow, and fast process corners is shown in Figure 4.12. Specifications of corners are shown in Table 4.3. Models of transistors are simulated with  $3\sigma$ . The maximal frequency, which can be used, is limited by load, power supply voltage, and temperature. There should not be a minimum frequency that can be used because the width of the pulse is given by the delay block in the pulse generator. The next subchapter will explain pulse generators that can be used in special applications.

Figure 4.11 - Double stacked inverter with 2-input logical AND

Figure 4.12 - Generated pulses across the PVTs from chosen generator

| Name        | Slow corner         | Typical corner | Fast corner |

|-------------|---------------------|----------------|-------------|

| Process     | Slow 3 <sub>5</sub> | Typical        | Fast 30     |

| Voltage     | 1.08 V              | 1.20 V         | 1.32 V      |

| Temperature | -40 °C              | 27 °C          | 150 °C      |

Table 4.3 - Table of specific cross corners

#### 4.1.2 Pulse generators for special purpose

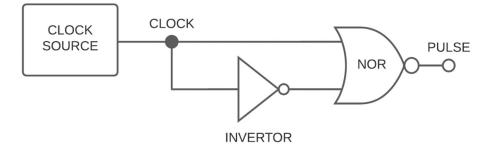

The purpose of the previous subchapter was to make a pulse generator that can make a pulse for the rising edge of the clock signal. These kinds of generators can make a pulse on the falling edge or both edges. First, the pulse generator that can make a pulse on the falling edge will be explained. This generator must be used for special purposes because the system needs to be prepared for this kind of generator. A pulse generator working on the falling edge can be made like the pulse generator shown in Figure 4.6 but instead of a logical AND, there is a logical NOR as it is shown in Figure 4.13.

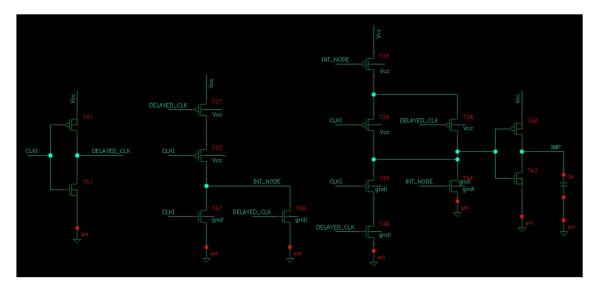

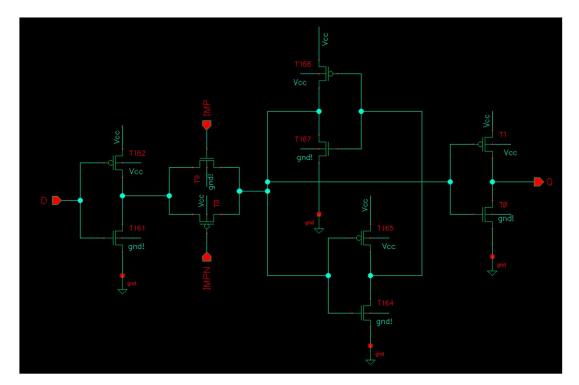

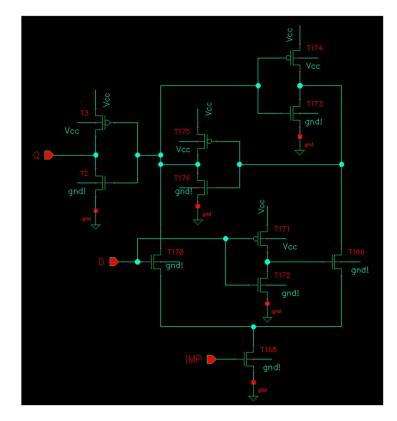

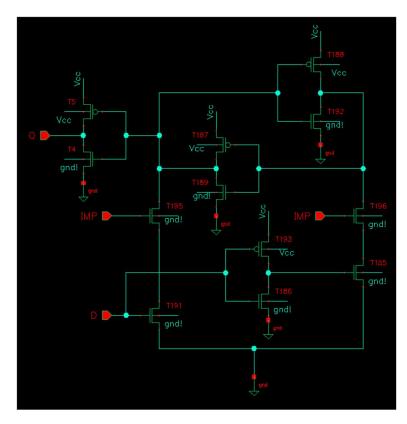

Figure 4.13 - Block diagram of the pulse generator with 2-input NOR gate