# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# CENTRAL EUROPEAN INSTITUTE OF TECHNOLOGY BUT

STŘEDOEVROPSKÝ TECHNOLOGICKÝ INSTITUT VUT

# NEW NANODEVICES FOR ELECTRONICS - FABRICATION AND CHARACTERIZATION

NOVÉ NANOPRVKY PRO ELEKTRONIKU – PŘÍPRAVA A CHARAKTERIZACE

# **DOCTORAL THESIS**

DIZERTAČNÍ PRÁCE

**AUTHOR** AUTOR PRÁCE Ing. Marian Márik

**SUPERVISOR**

ŠKOLITEL

doc. Ing. Jaromír Hubálek, Ph.D.

**BRNO 2021**

# **ABSTRACT**

This work proposes a technique for fabrication of a self-ordered nanostructures for electrical applications. The devices were prepared by anodic oxidation in two lengths and three different heat treatments. The structural characterization using SEM, TEM and EDX technics, respectively, were evaluated from structural and material point of view as well. The unique root structure of the highly self-ordered nanocolumn arrays was evaluated and compared after three different heat treatments: as anodized, vacuum annealed and air annealed, respectively. The possible crystallographic orientation of the columns was not observed, however the nano-crystallites under the root structures were found.

The electrical study about the devices shown resistive switching behavior (RS), diode like behavior and a capacitive coupled diode like behavior as well. The active surface, from RS point of view, for the switching mechanism is at the top of the nanocolumns and the gold top electrode. The Schottky barrier height of the Ti/TiO<sub>2</sub> interface was calculated with two methods, and it was lower than 1,11 eV for all three devices.

# **KEYWORDS**

TiO<sub>2</sub>, anodic oxidation, resistive switching, Schottky barrier height, nanocolumn, alumina

## **ABSTRAKT**

Táto práca sa zaoberá technikou výroby samousporiadaných nanoštruktúr pre elektrické aplikácie. Prototypy boli pripravené anodickou oxidáciou v dvoch dĺžkach a tromi rôznymi tepelnými úpravami. Štrukturálna charakterizácia bola spravená pomocou techniky SEM, TEM a EDX a vyhodnotenie nielen z štrukturálneho, ale aj z materiálového hľadiska. Jedinečná koreňová štruktúra samousporiadaných nanotyčiniek bola vyhodnotená a porovnaná po troch rôznych tepelných úpravách: po anodizácii, po vákuovom žíhaní, a po žíhaní vo vzduchu. Všetky prototypy obsahujú nanotyčinky s amorfnou štruktúrou, ale našli však nanokryštály koreňovými štruktúrami. aj pod sa Elektrická charakterizácia prototypov ukázala: odporové spínacie správanie (RS), diódové charakteristiky a charakteristiku podobnú pre diódy s kapacitorom. Aktívny povrch pre spínací mechanizmus je v hornej časti nanoštruktúr na rozhraní nanotyčiniek a zlatej elektródy. Výška Schottkyho bariéry na rozhraní Ti / TiO2 bola vypočítaná dvoma spôsobmi a pre všetky tri zariadenia bola nižšia ako 1,11 eV.

# **KĽÚČOVÉ SLOVÁ**

TiO<sub>2</sub>, anodická oxidácia, odporové spínanie, Schottkyho bariéra, nanotyčinka, oxid hlinitý

MÁRIK, Marian. Nové nanoprvky pro elektroniku – příprava a charakterizace [online]. Brno, 2021 [cit. 2021-04-30]. Dostupné z: https://www.vutbr.cz/studenti/zav-prace/detail/125711. Dizertační práce. Vysoké učení technické v Brně, Středoevropský technologický institut VUT. Středoevropský technologický institut VUT. Vedoucí práce Jaromír Hubálek.

# **DECLARATION**

| I certify that the work presented in this thesis was performed independently, under the supervision of doc.Ing. Jaromír Hubálek Ph.D., and is original with the sole exception of the technical literature and other sources of information that are acknowledged in the text and reference list, and that the material has not been submitted, in whole or in part, for a degree at this or any other university. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Brno(Ing. Marian Márik)                                                                                                                                                                                                                                                                                                                                                                                            |

# **ACKNOWLEDGEMENTS**

I would like to thank you to my supervisor doc. Ing. Jaromir Hubalek, Ph.D. for his support during my studies and my work. I would like to thank to my colleagues from LabSensNano for their suggestions and ideas.

Special gratitude goes to Dr. Alexander Mozalev for his advices and for the introduction into the world of electrochemistry. Also, I would like to thank to Dipl.Ing. Maria Bendova, Ph.D., for his support and because she taught me the importance of the data organization and the reporting.

My sincere gratitude goes to my family and friends for their well-timed motivation, they support me always in the biggest needs. Last, but not least I would like to thank you to my wife and to my daughter for their patience and love.

# **Contents**

| Ab  | stract      |                                                        | i  |

|-----|-------------|--------------------------------------------------------|----|

| Ke  | ywords      |                                                        | i  |

| Ab  | strakt      |                                                        | i  |

| ΚĽ  | ÚČOVÉ SLOV  | VÁ                                                     | i  |

| Do  | claration   |                                                        | i. |

|     |             |                                                        | iv |

| Ac  | knowledger  | nents                                                  | V  |

| Int | roduction   |                                                        | 8  |

| 1   | State of th | ne art                                                 | 9  |

|     | 1.1         | Memristors and resistive switching                     | 10 |

|     | 1.1.1       | Memristors from the mathematical view                  | 11 |

|     | 1.1.2       | Memristors: the emerging memories- type of memristors  | 13 |

|     | 1.1.3       | Principles and technologies in most promising memories | 15 |

|     | 1.1.4       | Switching behavior in valve metal oxides               | 19 |

|     | 1.2         | Valve metal oxides                                     | 25 |

|     | 1.2.1       | Anodic aluminum oxide                                  | 26 |

|     | 1.2.2       | 2 Titanium dioxide                                     | 29 |

| 2   | Aim of the  | e work                                                 | 32 |

| 3   | Experimer   | ntal                                                   | 33 |

|     | 3.1         | Layer preparation                                      | 34 |

|     | 3.2         | Anodization of Aluminum                                | 36 |

|     | 3.3         | One step anodization                                   | 37 |

|     | 3.4         | Two step anodization                                   | 39 |

|     | 3.5         | Anodization of Titanium                                | 42 |

|     | 3.6         | Deposition of top electrode arrays                     | 47 |

|     | 3.6.1       | , ,                                                    |    |

|     | 3.6.2       |                                                        |    |

|     | 3.7         | Material and structure characterization                |    |

|     | 3.7.1       | TEM sample preparation                                 | 56 |

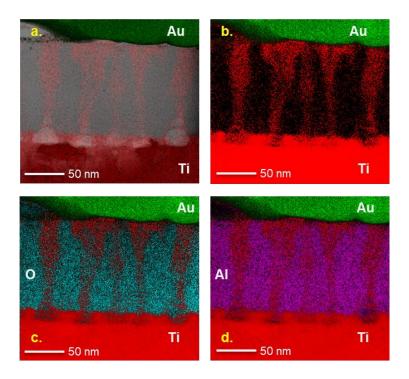

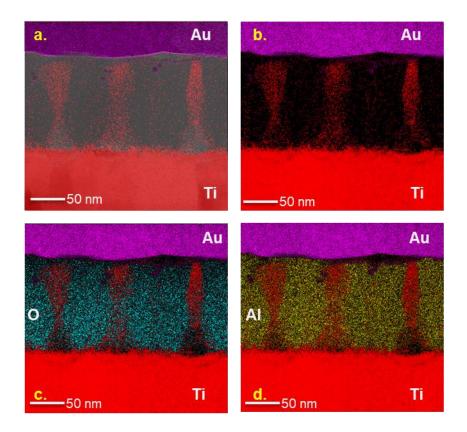

|     |        | 3.7.2             | Material characterization by TEM and EDX                                                         | 57       |

|-----|--------|-------------------|--------------------------------------------------------------------------------------------------|----------|

|     |        | 3.7.3             | Characterization of nanocolumns anodically grown at 40V                                          | 59       |

|     |        | 3.7.4             | Characterization of nanocolumns re-anodized at 100V                                              | 63       |

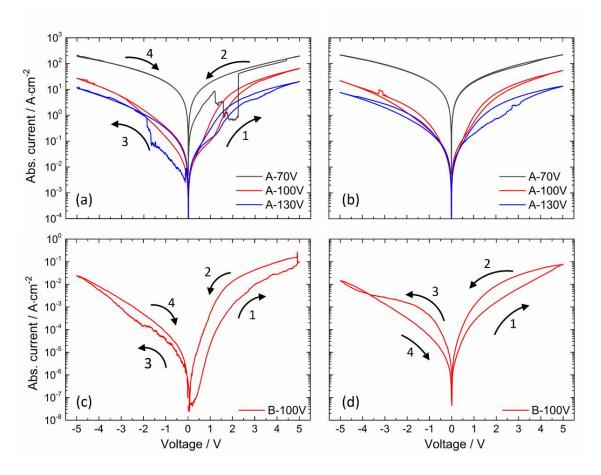

|     | 3      | .8 E              | lectrical Characterization                                                                       | 68       |

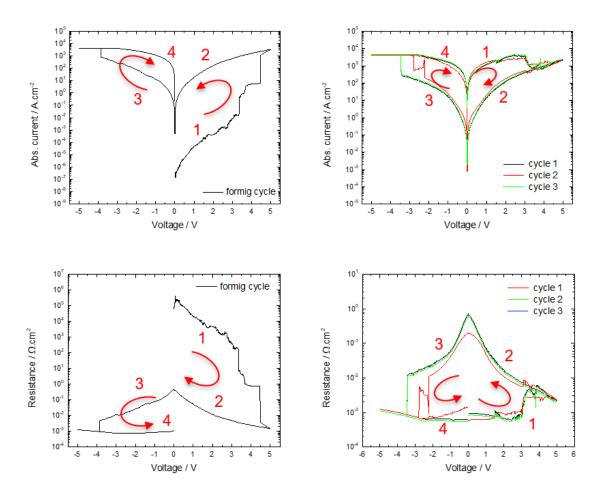

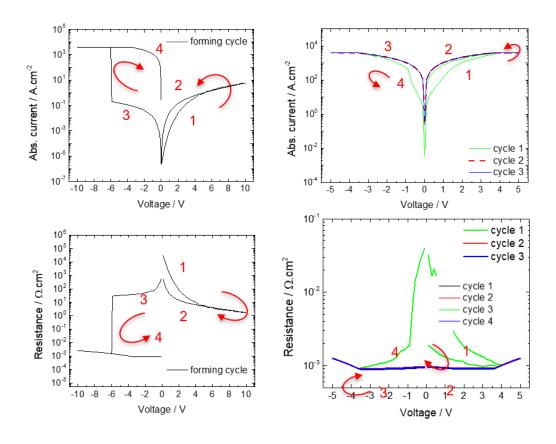

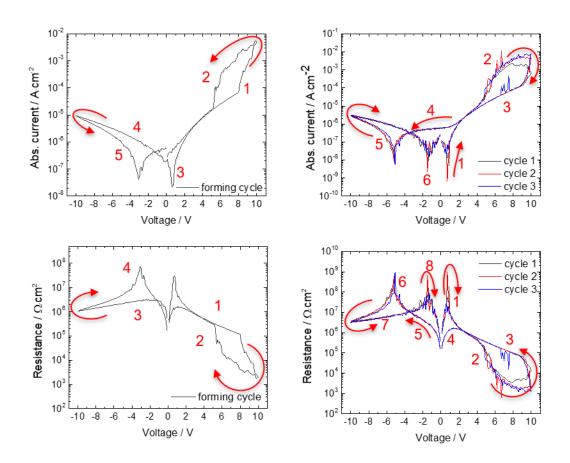

|     | eled   | 3.8.1<br>ctrochen | Quotation 1.: Electrical characterization of nanomically grown at sweep rate 2 V·s <sup>-1</sup> |          |

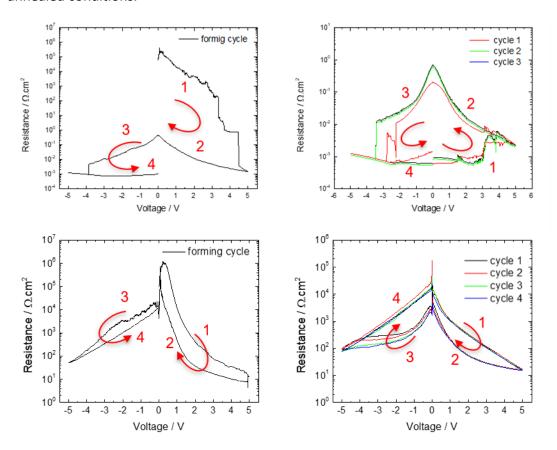

|     | V      | 3.8.2             | Electrical characterization of nanocolumns electrochemically gro                                 | wn at 40 |

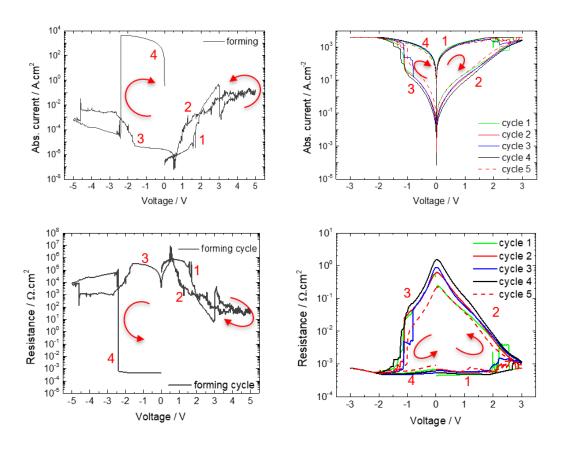

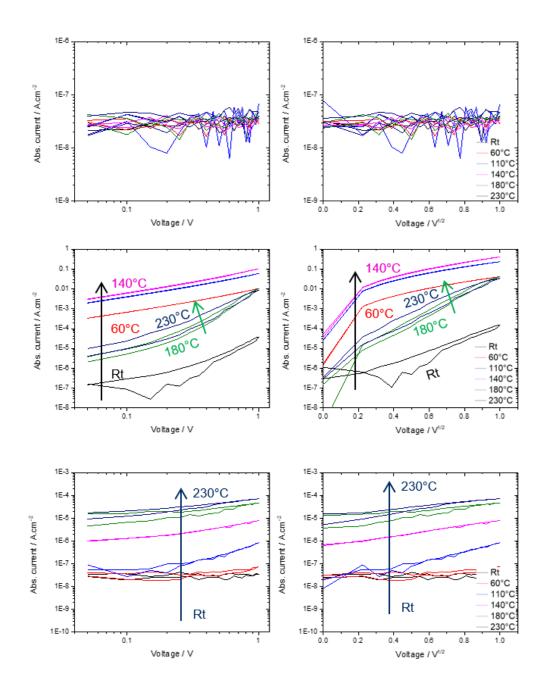

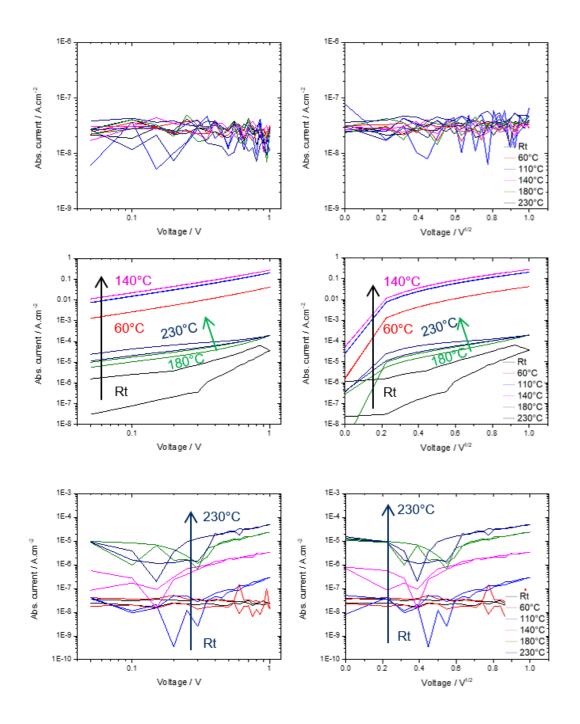

|     |        | 3.8.3             | Electrical properties of nanocolumns differently annealed                                        | 74       |

| 4   | Cond   | clusion           |                                                                                                  | 83       |

| Re  | ferenc | ces               |                                                                                                  | lxxxv    |

| LIS | T OF F | GURES             |                                                                                                  | хс       |

| LIS | T OF 1 | TABLES            |                                                                                                  | xcv      |

| LIS | T OF A | ACRONY            | <b>YMS</b>                                                                                       | xcvi     |

| Au  | thors  | publicat          | tions and other inputs                                                                           | 97       |

# INTRODUCTION

In 1965, Gordon E. Moor said about the semiconductor manufacturers, they had been doubling the density of components on integrated circuits periodically every second year. His prediction, commonly known as Moor's law, has been fulfilled in the last fifty years. [1.] According to the current state of art, that paradigm eventually comes to the end in the next 5 or 15 years. Instead of the focus just on the size reduction, the electronic industry should emphasis more on the increasingly capable devices. [2.]

The common available memory devices were mostly based on transistor oriented electronic design, which is not limited just with decreasing size and basic laws of physics, but also with suitable combination with passive elements. Introduction of a new passive element, called memristor, could be improving the performance of digital circuits. [2.] Main advantage of the memristors is their ability to save information. The memristor is able to "remember" the last state before the power is switched off.

Since May 2008, when the research laboratory of Hewlett Packard published the first experimental memristor (Strukov et al., The missing memristor found, Nature Letters [3.]), the interest ain the resistive and memristive research suddenly increased. Based on the state of the art of the memristor technology, the possible way to realize a commonly usable resistive memory is extremely wide. Using an oxide-based multilayers is one of the feasible directions.

This essay is dealing with fabrication and characterization of metal/oxide/metal devices with expected resistive switching abilities, which are basics of memristors for non-volatile memory applications.

The first part of this study is dealing with the fundamental theoretical knowledge about memristors, briefly from mathematical background through the current state of the art continuously to the deeper introduction of the titanium dioxide (TiO<sub>2</sub>) based resistive memories. The second part of the thesis is oriented on the practical works and experimental results. The fabrication is focused mainly on the TiO<sub>2</sub> nanostructures, prepared, and modified with electrochemical processes. The electrical characterization of prepared structures is discussed as well.

# 1 STATE OF THE ART

Smaller, faster, cheaper, and simpler structure – these four requirements are determining the direction of the memory development. In last three decades the progress in the traditional memory technology and storage systems was enormous. The requirements for the systems with higher performance and larger capacity are increasing; however, the energy consumption and the space requirements should be lower and lower.

These above-mentioned facts motivated the researchers to find another way, how to fulfill requirements with existing technology possibilities. This resulted strong innovation in the current memory technology and it has also motivated for a development of alternative memory technologies as well.

Among several potential candidates for alternative memory technology, memristors have been recognizing as a viable option due to their simple physical structure, scalability potential and reliable characteristics. The possible answer for question of the 21<sup>st</sup> century was found in the past at the beginning of the 70's.

# 1.1 Memristors and resistive switching

In the last 150 years, the known fundamental passive elements were limited to capacitor [C], resistor [R], and inductor [L]. In 1971, Professor Leon Chua at the University of California, Berkley published an underestimated paper about the fourth basic passive element. However, the idea was great, the technology in the 20<sup>th</sup> century was not enough developed. [4.][5.]

The "re-invention,, of the memristors is boiled together with the name Strukov and the HP laboratory, where the first physical model was born and published. The number of the researches and the researchers dealing with memristors exponentially raised. In last 12 years. However we are usually speaking about the memristor oriented research, the difference between the memristors and the memristive switching has to be declared.

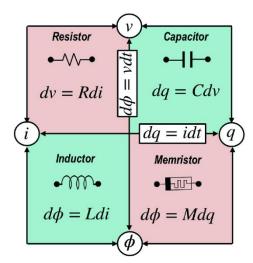

The memristor is a two-terminal component with non-linear electrical characteristics, linking magnetic flux and charge, presented in Figure 1.1. [4.]

The resistive switching is a phenomenon observed at devices, which are changing their resistance based on the applied potential / current and when the power is off, the resistance state will not change back.

Figure 1.1.: The extrapolated conceptual symmetry between the non-linear resistor, non-linear capacitor, non-linear inductor and the forth possible passive fundamental non-linear element, the memristor. [4.]

#### 1.1.1 Memristors from the mathematical view

From the circuit-theoretic point of view, Chua published the relationship between the four circuit quantities — voltage, current, charge and magnetic flux — which are define by the three basic two-terminal elements (C, R, L). [2.],[5.] Six possible combinations of relationship can be deduced for these circuit variables.

The relationship between the charge and the current is given by the equation 1, and the one between flux and voltage is described by the equation 2. Three other relationships are written by the axiomatic definition of the resistor (equation 3), capacitor (equation 4) and of the inductor (equation 5). [5.]

$$q(t) = \int_{-\infty}^{t} i(\tau) d\tau \tag{1}$$

$$\varphi(t) = \int_{-\infty}^{t} v(\tau) d\tau$$

(2)

$$dv = Rdi$$

(3)

$$dq = Cdv (4)$$

$$d\varphi = Ldi$$

(5)

The functional relation between the charge and the flux from the logical and the axiomatic point of view is possible only with a new two-terminal element (equation 6) which is characterized by 2-q curve. The new element was titled memristor [M]. [3.][5.]

$$d\phi = Mdq \tag{6}$$

The first physical model of memristor was published by HP research laboratories in 2008. This device was a metal oxide metal multilayer controlled by the current. The differential form of the current controlled memristor for circuit analysis is written in equations 7 and 8 [4.],

$$v = \mathcal{R}(w)I \tag{7}$$

$$\frac{\mathrm{dw}}{\mathrm{dt}} = I \tag{8}$$

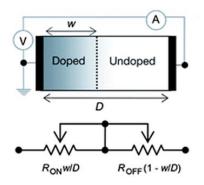

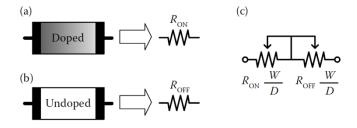

where w can be a set of state variables and R and f can be in general explicit functions of time. The simplest way to explain how the memristor works is to consider a thin sandwich film of metal – semiconductor – metal (see Figure 1.2). The semiconductor layer with thickness D is placed between two metal contacts. The specialty of this semiconductive layer is the nonhomogenous concentration of the dopants. Because of this fact, the total resistance is considered between the two metal contacts for the full-length D and it is determined by two resistors in series.

Figure 1.2: The diagram of the memristor with a simplified equivalent circuit. [3.]

The higher dopant concentration causes lower resistance, the lower dopant concentration causes higher resistance. The applied external bias voltage v(t) across the device can move the boundary between the doped and undoped region. The equations for governing of memristance of a thin semiconductor film were obtained using the models in Figure 1.3 and considering the simplest case of ohmic conduction and linear ionic drift in a uniform field with an average ion mobility  $\mu_v$ :

$$v = \left(R_{on} \frac{w(t)}{D} R_{off} \left(1 - \frac{w(t)}{D}\right)\right) i(t) \tag{11}$$

$$\frac{\mathrm{d}w(t)}{\mathrm{d}t} = \mu_{v} \frac{R_{on}}{D} i(t) \tag{12}$$

which yields in the following formula for w(t):

$$w(t) = \mu_v \frac{R_{on}}{p} q(t). \tag{13}$$

By substituting eq.13 in eq. 11, we obtain the memristance of the system, which for the case Ron << Roff is simplified to:

$$M(q) = R_{off} \left( 1 - \frac{\mu_{\nu} R_{on}}{D^2} q(t) \right). \tag{14}$$

Figure 1.3: Memristor in ON state (a.) and in OFF state (b) with the equivalent circuit (c.). [2.]

# 1.1.2 Memristors: the emerging memories- type of memristors

Since 2008 memristor became a synonym for the non-volatile memories (NVM). The question, if the non-volatile memories are really memristors or not, will be discussed later. For better understanding why it is important to deal with NVMs and what is the current situation in this field, the types and the basic principles of the NVMs are introduced at first. [6.]

The research in non-volatile memories in the last few years rapidly rises. More and more companies are trying to substitute classical volatile memories as DRAMs, SRAMs or non-volatile NOR-Flashes and NAND Flashes. The main disadvantage of the SRAM and DRAM memories is their volatile character. If the power is turned off, they lose the stored information. At non- volatile Flash memories the information is stored even the power is turned off, but they are limited with amount of read/write cycles and with read/write speed. The new emerging memories are intended to fix disadvantages of above-mentioned memories. The basic comparison of conventional and emerging memories is shown in Table 1 [7.]

Table 1.: The basic comparison of conventional and emerging memories.

|                      | Volatile<br>memory  |                     | Non-volatile<br>memory |                  | Emerging non-volatile memory |                       |                         |                            |

|----------------------|---------------------|---------------------|------------------------|------------------|------------------------------|-----------------------|-------------------------|----------------------------|

| Туре                 | SRAM                | DRAM                | NOR-<br>FLASH          | NAND-<br>FLASH   | MRAM                         | PRAM                  | FRAM                    | RRAM                       |

| Cell elements        | 6T                  | 1T1C                | <b>1</b> T             | 1T               | 1(2)T1R                      | 1T1R or<br>1D1R       | 1T1C                    | 1T1R<br>or1D1R             |

| Cell elements        |                     |                     |                        |                  | Magneto-<br>resistance       |                       | Polarization-<br>change | Resistance<br>-change      |

| Minimum cell size    | 140F <sup>2</sup>   | 6F <sup>2</sup>     | 10F <sup>2</sup>       | 5F <sup>2</sup>  | 20F <sup>2</sup>             | 4.8(4)F <sup>2b</sup> | 22F <sup>2</sup>        | 4F <sup>2c</sup>           |

| Write/<br>Earse time | 0.3ns/<br>0.3ns     | <10ns/<br><10ns     | 1ms/0.1ms              | 1ms/<br>0.1ms    | 10ns/<br>10ns                | 20ns/<br>50ns         | 10ns/ 10ns              | 5ns/5ns                    |

| Endurance (cycles)   | >3x10 <sup>16</sup> | >3x10 <sup>16</sup> | >10 <sup>5</sup>       | >10 <sup>5</sup> | >3x10 <sup>16</sup>          | 10 <sup>8</sup>       | 10 <sup>14</sup>        | >10 <sup>10</sup>          |

| Application          | Cache               | Main<br>memory      | Storage                | Storage          | Storage                      | Storage               | Storage                 | Storage/<br>Main<br>memory |

There are several types of new non-volatile memories, but most of them exist only on laboratory level. The most common classification of emerging memories is based on the phenomenon which allows data storage without external power:

- Ferroelectric RAMs (FRAMs),

- Magnetic or Magnetoresistive RAMs (MRAMs),

- Phase-change RAMs (PRAMs),

- Resistive RAMs (RRAMs)

- Electrochemical metallization memories (ECM)

- Programmable metallization cell memories (PCM),

- Carbon nanotube (CNT) memories,

- Millipede memories

- Molecular memories,

- Nano-crystal floating gate FLASH memories,

- DNA memories.

From above mentioned memory types, only FRAMs, MRAMs, PRAMs and RRAMs could overcome limitations of DRAMs or FLASH memories. The principles and technologies of data storage used in these memories are discussed in the next chapter. [7.]

# 1.1.3 Principles and technologies in most promising memories

#### 1.1.3.1 FRAM

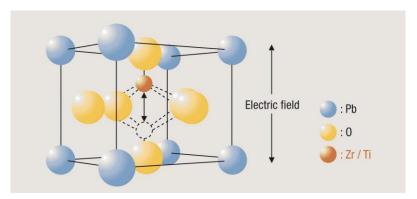

Ferroelectric RAMs use ferroelectric phenomena in ferroelectric materials. When an electric field E stronger than coercive field Ec is applied to a ferroelectric material, the change in the ferroelectric polarization get hysteresis character. The data storage is possible when the polarization versus the electric field loop presents two distinguishable polarization states. [7.]

Two classes of ferroelectric materials are used for FRAMs:

- perovskite structures (PbZr<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub> PZT)

- layered structures. (Sr<sub>1-y</sub>Bi<sub>2+x</sub>Ta<sub>2</sub>O<sub>9</sub> SBT or Bi<sub>4-x</sub>La<sub>x</sub>Ti<sub>3</sub>O<sub>12</sub> BLT)

Polarization occurs as a lattice deformation of the cubic form below the Curie point, the temperature above which the material becomes paraelectric. Moving of Ti atom in PZT is possible into two stable positions by an electric field. One of the positions is above the second one below the oxygen plane of the structure (see Figure 1.4). The residual permanent polarization of ferroelectric materials is in the range of 10 to 30  $\mu\text{C/cm}$ . The voltage range required to switch the permanent polarization for deposited layer thicknesses ranging from 70 to 100 nm is between 1.5 to 3 V. From this information is clear the ferroelectric memories are suitable for low voltage applications. [8.]

Figure 1.4: The information (logically 1 or 0) is contained in the polarization of the PZT. [9.]

#### 1.1.3.2 MRAM

Magnetic RAMs are possible candidates to replace the current memories, mainly embedded SRAMs and NOR-Flashes. Two types of MRAMs are distinguished based on the used phenomena for data storage:

- Field-writing MRAM the writing is done by a magnetic field around the current line.

Promising results were shown at developing three terminal devices where the magnetic state of magnetic tunnel junction (MTJ) act as a memory bit. [10.]

- Spin-transfer torque MRAMs the writing is done by spin polarized current which can manipulate magnetization orientations in the magnetic multilayer nanostructures.

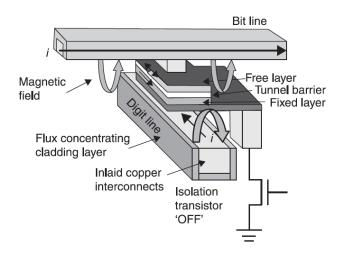

The MTJ is schematically shown in Figure 1.5. It is composed from pinned magnetic

layer, tunnel barrier and free magnetic layer. The magnetic layer polarizes the electron spin, which traverses the tunnel barrier. The parallel alignment of the free layer with respect to pinned layer results in a low resistance state, while an antiparallel alignment results in a high resistance state. [8.] Moreover, one of the advantages of the MTJ MRAMs is the non-destructive read with very fast access cycles and the adequate read/write cycles. The major disadvantage of these memories is the high write current, which is in mA range.

Figure 1.5: Schema of the programming operation mode at the MRAM cell in the 1MTJ/1transistor option [8.]

The Spin-Transfer torque MRAMs are also based on MTJ structures, where a current induced switching caused by spin-transfer torque is exploited.[8.]

#### 1.1.3.3 PRAM

Phase change memory (PCM) exploits the resistance contrast between the amorphous and crystalline states in materials. This simple change is related only to special group of materials, called phase change materials. Indeed, it is not possible to change amorphous phase to crystalline or vice versa in all materials. As a result, it allows distinguishing high electrical resistivity at amorphous state and low resistivity at crystalline state. [12.]

The change between the two states is provided by current induced joule heating. With miniaturization, the energy of 1 pJ should be sufficient for programming for one memory cell. According to the last research results, 40 nm technology is real for mass production.

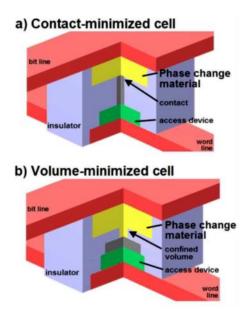

To realize a PCM cell, usually two types of cell structures are used: either contact minimized cells or volume minimized cells (see Figure 1.6). The contact minimized cell structure is based on a narrow cylindrical metal electrode, which is contacted to a thin phase change material film. This cell structure is also called a mushroom cell. [8.]

The volume minimized cell structure is similar to the mushroom cell, but the fabrication processes more challenged. The most obvious structures in this category are pillar and pore cells. At the pillar cells a narrow cylinder of phase change material is placed between two

electrodes. The fabrication of this kind of structure is difficult, because the pillar is too small and the patterning of the large bottom and top contact must be precise. [14.]

The pore cells are fabricated by filling a sub-lithographic hole in the insulating material at the top of the bottom electrode. The conformal filling of the holes with conventional PVD processes is difficult, but results in filling the hole via ALD and CVD deposition techniques are promising. [14.]

Figure 1.6: Typical device archetypes for PCMs.[8.]

#### 1.1.3.4 RRAM

The basic idea was set up on Chua's paper from 1972, which was a two-terminal resistor with a memory. Resistive switching memory cells are usually presented as a three-layer metal – insulator – metal (MIM) sandwich systems. By applying an appropriate voltage on a MIM cell, the electrical resistivity of the system can be changed substantially. The change from the high resistance state (HRS) to the low resistance state (LRS) or vice versa can represent the logic values 1 and 0. As it was mentioned in the Chapter 1., the main advantage of this change is the state remaining after the electrical power is removed. The switching between two states could be provided with changing the size and the polarity of the electrical potential.

Depending on the voltage polarity, the memristors (or RRAMs) are classified to unipolar, bipolar and nonpolar devices based on the switching behavior. The unipolar switching is provided with a voltage at the same polarity, but with a different magnitude. The bipolar switching is provided by using of both polarities. One polarity is for changing the device from LRS to HRS, the second one is responsible for the switching from HRS to LRS. The nonpolar or threshold devices are capable to switch from LRS to HRS and back from HRS to LRS in positive and also in negative voltage range.

The scientists make efforts to achieve the best performance in all computing and storage applications. The most important performance parameters can be summarized into seven points. [6.][12.]

- Operating voltage in practical applications the lower power consumption and the lower thermal loss is preferred. Most of the memristor prototypes are using up to 10V operating voltages, but some research labs are decreased switching voltage to 1 2V. This voltage range could be lower at thinner layers or at special type of materials.

- 2. **Operating speed** is the shortest time, which covers the reading/writing process for one memory cell. The average switching speed is around 5 to 100ns.

- 3. **Resistance ratio** the ratio between the HRS to the LRS plays important role at the reading and writing process. To distinguish the two states in circuit design, the resistance ratio must be greater than 10. Some resistive switching devices are working with a very high resistance ratio (6-7 orders of magnitude), which can be used at the fabrication of multibit or multilevel storages. [12.]

- 4. Endurance the lifetime of the RRAMs is depending on the distinguishable HRS and LRS. The device can be switched frequently, but every switching operation can introduce a small degradation of the device. Usually at the FLASH memories the maximum write cycle is between 10<sup>3</sup> and 10<sup>7</sup> cycles. To achieve a large success on the memory market a good RRAM should provide at least the same or bigger endurance, than the FLASH memories.

- 5. **Retention time** the longest time, during the memory cell is capable to retain the information without any change. Nowadays this time is around 10 to 40 years.

- 6. **Multilevel storage** ability to store more than one bit in one memory cell. It's enhanced storage density if the resistance ratio between the resistance states is enough large.

- 7. Device yield uncontrollability of the oxygen concentration in nonstoichiometric oxides generally indicates a fatal flaw of low device yield More papers were published in this field, where the device yield improvement was proposed by suitable electrode material, stoichiometric structures instead nonstoichiometric ones, intentionally used metal nanocrystals in oxide and utilizing doped metal oxide.[6.]

# 1.1.4 Switching behavior in valve metal oxides

Resistive switching phenomenon has been observed at most of the transition metal oxides. The switching behavior could be observed from physical and from electrical point of view. In unipolar RS, the switching direction depends on the applied voltage amplitude. At the memory cell prepared in HRS, usually a high voltage stress is used to put it into LRS. After this step so called" forming process ", the cell from LRS is switched to HRS by applying a threshold voltage (RESET). For switching from HRS to LRS a voltage higher than the threshold potential is needed. In the SET process the current must be limited. This type of switching has been observed mainly at the highly insulated binary metal oxides. [15.]

At the bipolar RS the dependence of the directional RS on the polarity of applied voltage has been shown. This type of RS behavior has been mainly observed at many semiconducting oxides, such as perovskite oxides.

Threshold switching is a less frequently used and observed than bipolar or unipolar RS. That phenomenon is similar to the unipolar switching. It works with one stable state with no external bias. The device from the HRS to LRS is switched by V<sub>set</sub>, and the LRS is stable over only a certain range of applied biases. The device reverts to the HRS in moment, when the applied bias falls below this range. The threshold switching due to the instability of CFs in LRS is not suitable for NVM.

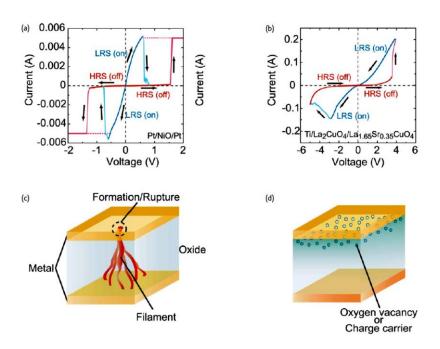

The RS behavior based on the conductive path is commonly categorized into two classes. The first class is the filamentary conductive path, where the ON and the OFF state are depending on the formation and the rupture of the conductive filament in an insulating matrix. (Figure 1.7.c.) [15.]

The second class is the interface type path, where the RS takes place at the interface between the metal electrode and the oxide. Electrochemical migration of oxygen vacancies, charge carrier (hole or electron) trapping or Mott transition induced by carriers doped at the interface are the mostly used models for driving mechanism in RS involving an interface type conducting path. (Figure 1.7.d.) [15.]

Figure 1.7: Schematic view of the unipolar (a) and bipolar (b) switching behavior. Schema of the filament type (c) and interface-type conductive paths (d). [15.]

#### 1.1.4.1 Unipolar switching in oxides

## **Forming and Set processes**

As-grown oxide cells are good dielectrics without capability of RS. To crate RS device from an as-grown oxide is obligatory to change the oxide properties. By applying a large external bias, oxygen vacancies or CFs are generated. This process called electroforming in unipolar switching is known to be triggered by the soft dielectric breakdown. Soft dielectric breakdown is a controlled breakdown limited by the compliance current, and it provides thermal energy to the ions in an oxide cell. When a large electric field is applied to a pristine oxide cell, the negatively charged oxygen ions move to the anodic interface.

The formation of one oxygen vacancy can be described in Kröger–Vink nomenclature as follow:

$$O_O \leftrightarrow \frac{1}{2}O_2 + V_O'' + 2e^-$$

(18)

Based on a paper from Kröger and Vink the  $O_0$  denotes an oxygen ion in a regular lattice and  $V_0$  indicates an oxygen vacancy. [23.][24.]

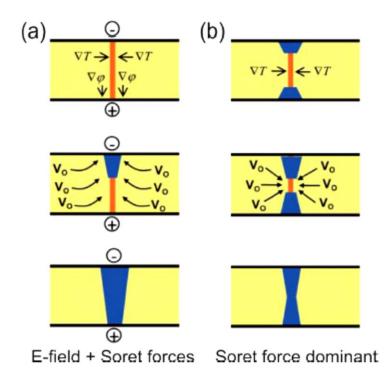

The dominant force for oxygen vacancy migration – electric field effect or Soret force – has primary effect on the growth behaviors of the CFs during the forming process.

In case, when the dominant force is the electric field effect, the oxygen vacancies are migrating toward the cathode. In this process the CFs composed of oxygen vacancies accumulating near the cathode and subsequently growing through the cell. This type of CF generation has been observed with a conical structure in TiO<sub>2</sub> [23.][25.] [Figure 1.8. a.] The second case, when the Soret force is dominated, the oxygen vacancies are moving mostly perpendicularly to the electric field. The CFs usually are expected with cylindrical shape and

Figure 1.8.: Two filament growing models initiated by Joule heating. The CF is built by positively charged vacancies, attracted toward the cathode (a.). CF built is induced by Soret and Fick forces if the vacancies are electronically neutral (b.). [25.][23.]

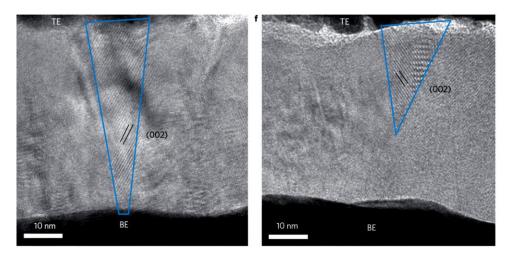

The localized CFs in an oxide samples generated by forming process brings local change in conductance, which is is related to changes in the chemical stoichiometry of the oxide. The mechanism of the local conductance changed by the oxygen stoichiometry is depending on the material, mainly on the phase diagram of the composing oxide. During the RS formation in metal oxides the formation of Magnéli phases of formation of metal-rich (or metlallic) region is used for CF generating. As Kwon et.al. published they found besides the nanofilaments in the connected shape several disconnected nanofilaments in Magneli phases as well. The diameter of the CFs at the cathode side was bigger which is a proof the CFs are growing mostly from the cathode side. [44.]

When the current limit reaches the compliance limit, the bias voltage is significantly reduced to prevent a further growth of other CFs. Figure 1.9. a. show a complete CF with conical shape grown from the top electrode down to the bottom electrode. The not completed or disconnected nanofilament kept the conical shape with a wider diameter at the TE. (Figure 1.9. b.)

Figure 1.9.: Magne'li structures in the SET sample. High-resolution TEM image of a connected Ti<sub>4</sub>O<sub>7</sub> / Ti<sub>5</sub>O<sub>9</sub> nanofilament (left) and a disconnected filament (right). [44.]

#### **Reset process**

The flown current during the forming or set process can produce in the formed CF Joule heating. Thereby the temperature in nanometer scale temporary can reach few hundred Kelvins. As Chang et.al. observed in a Pt/NiO/Pt unipolar switching cell, the maximum temperature in the vicinity of the CF could reach higher than 900 °K with a bias of 2 V applied to the electrodes. If we took into consideration the fact, the  $TiO_2$  can be transform from amorphous phase into crystal phase from 400 °C by thermal annealing, or even at lower temperature in case of hydrothermal treatments, and then it is clear the switching mechanism can be more complex in few cases. [44.][45.]

The current generated Joule heating can provide the oxygen vacancies with sufficient thermal energy to overcome the energetic barrier for hopping. In this case the Soret force and the Fick force are acting perpendicularly to the electric field. The Soret force can be characterized as an effect where the temperature gradient attracts the oxygen vacancies toward the CF. The Fick force is an effect where the density gradient repels the oxygen vacancies from the CF.

Both forces are playing important role in resistive switching. The Fick force is dominating during the reset process, where the CF is ruptured. [46.][46.]

#### 1.1.4.2 Bipolar switching in oxides

Bipolar switching in oxides means polarity dependence of the Set and Reset operations. The basic mechanism for bipolar switching can be defined on the movement of oxygen vacancies or by the electron trapping/de-trapping.

Oxygen vacancies should always exist in any oxide due to entropic disorder. The creation of the oxygen vacancies can be created by partial substitution with dopants, as Y-doped  $ZrO_2$  or Ca-doped  $BiFeO_3$ , or via the forming process, as a result of electrolytic reaction – explained by Kröger – Vink nomenclature.

The oxygen vacancy motion is forced by an external electric field, the direction of the detailed motion of the vacancies is vary, however for the vacancies formed in a solid with periodic potential, the motion can be described by a thermally assisted hopping process. [75.][76.] The disordered interfaces or the grain boundaries can also have effect on the oxygen vacancy migration.

The electron trap/detrap in oxides usually is presented by three models:

- 1. Pool-Frenkel emission, where the emission model is related to the thermal fluctuations of trapped electrons. The trapped electron gets energy from the random thermal fluctuation for the transfer from the localized state into the conduction band, where it can transport through the crystal. The I(V) behaves as I~Vexp<sup>(V1/2)</sup>

- 2. The space charge limited current model describes situation, where the external charge carriers from the electrode are more dominant than the free carriers in the film. At low voltage the films conduction is dominating (the I(V) curve is linear), at increasing voltage the amount of the externa charge carriers increasing, therefor the electrons are gradually trapped into the defects (non-linear I(V)). If the applied potential is high, the electrons are trapped in defects, however the excess electrons can flow and therefor the linear relationship of I~V is recovered.

- 3. Trap-assisted tunneling model describes tunneling of the electrons between the traps via hopping. The conduction is dominated by cathode-trap or anode-trap hoping, resulting I(V) curves as  $In(I/V^2)^{-1}I/V$ .

Forming process is required due to first conductive filament formation. The forming is not necessary for all oxides, especially if the bulk region is eliminated by a low thickness (about 4 nm), however for some oxides, like (TaO<sub>x</sub>, TiO<sub>2</sub>), the CFs can be created only by forming process. The CFs can be detectable by TEM, EELS or by hard X-ray spectromicroscopy, if channels are formed by exhibited metallic properties and ordered planes of oxygen vacancies, or by comparison of oxygen-deficient regions with as-grown material.

Briefly the forming process is the first step, when the virgin sample (also called pristine sample) under applied external bias a CFs are grown, mostly in the bulk region. Between the CF and the top electrode, a gap region is formed as well, however the gap has lower resistance (R<sub>LRS</sub>) then the CF (LRS state). The HRS state appears after Reset process, when the Gap region with resistance R<sub>LRS</sub> is transformed back to the initial resistance state of the oxide (HRS).

The importance of the CF in bipolar switching is significant mainly due to the current localization. The CF localizes current into conducting spots and therefor the switching will take place always at the same position in the same gap region.

The resistance of the device will be independent on the electrode area, the determining is the CF nanoscale gap area at the top of the CF. In studies, where the electrode surface had effect on the RS resistances, the switching behavior can be called as interface type switching or laterally uniform switching among the interfaces.

Bipolar switching can be achieved by growth/shrinkage of a virtual cathode by oxygen vacancy movements, by modulation of the Schottky barrier by oxygen vacancy movements and by trap/detrap of electrons. The modulation of the Schottky barrier by oxygen vacancy

movements is typical for n-type semiconductors with a metal electrode with a large work function, as Au or Pt.

This work is focusing on the TiO<sub>2</sub> based MOM devices with Ti and Au electrodes, therefor the modulation of the Schottky barrier height by oxygen vacancy movements will be briefly described.

The interface between the Ti (low work funciton) and the oxide is usually ohmic. The Schottky barrier appears at the oxide and Au interface, where the oxygen vacancies in the oxide are behaves as donors. Therefor any change in the oxygen vacancy concentration can significantly change the barrier width and along with it the electrical resistivity of the device, respectively. The width of the Schottky barrier between the oxide and the Au electrode, has width inversely proportional to the square root of the dopant concentration.

The negative polarization of the anode forcing the positively charged electrons towards the electrode, therefore the Schottky barrier width is decreased, the resistance state from HRS is changing to LRS. At positive anode polarization the barrier width is increasing and with the barrier width the resistance is growing as well. Simulation of a semiconductor with mobile dopant model for bipolar switching was published by Lee at al., [73.] Another models were described by Jeon et al., about the effect of Helmholtz layer in Pt/TiO<sub>2</sub>/Pt devices, where the barrier height was modulated by electrochemical reactions involving oxygen vacancies at the metal oxide interface. [74.]

## 1.2 Valve metal oxides

Valve metals are part of group *IVB* and *VB*, as Ti, Zr, Hf, V, Nb, Ta, from *IIIA* Al, and they are immediately reacting with the oxygen or humidity to form a protective oxide layer. For their fast self-protection oxide layer, they are widely used in the construction of chemical apparatus.

The other usage for the valve metals or valve metal oxides, respectively, is in electronics, where their excellent metal oxide properties are used in piezoelectric, multifrerrocity, sensing or resistive switching researches.

Dielectric properties of valve metal oxides are well known due to the high dielectric constants, therefore the high- $\kappa$  oxide can be also a proper naming. Other oxide properties, like the vacancy defects formed by oxygen disorder in the lattice is used in electronics, as band insulators or Mott insulators.

Memristive research is using valve metal oxides from the beginning – the first memristor published by Strukov et al., was fabricated with a TiO<sub>2</sub> layer – and with the different preparation methods, the physical properties or even the shape of the prepared oxide can be controlled.

The spine of this work is  $TiO_2$  structures, prepared by electrochemical anodization. The  $TiO_2$  is described in chapter 1.2.2. and the fabrication process is explained in chapter 3.5., respectively.

#### 1.2.1 Anodic aluminum oxide

The aluminum layers in ambient atmospheres becomes quickly coated with a native oxide layer in thickness 2-3 nm. This thin oxide layer inhibits the aluminum surface from corrosion in common environments. Corrosive chemicals or environments containing chlorides, sulfates etc. can cause local corrosion of metal.

Buff in 1857 discovered the aluminum can be electrochemically oxidized in aqueous solution to form thicker oxide layer than the native one. The aluminum part in the electrolytic cell was used as anode and the process has been named "anodization". Anodic oxidation of aluminum surfaces was commercially used as a protection layer since the beginning of the 20<sup>th</sup> century.

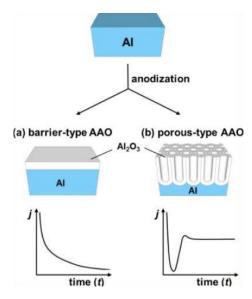

Generally, the aluminum oxide has two type of morphologies: the nonporous barrier oxide and the porous oxide. The morphology is mainly determined by the chemical nature of the electrolyte. A compact barrier type film (BTF) can be formed in electrolytes with pH 5-7. The most common solutions for preparation are oxalate, citrate, phosphate, adipate. The porous anodic alumina (PAA) is formed in acidic electrolytes. Oxalic, malonic, selenic, tartaric, citric, phosphoric, malic and chromic acids are widely used for anodization. The pores are formed due to the lower pH, because the AAO is slightly soluble at lower pH.

The oxide growth kinetics are different at BTF and PAA. The thickness of the BTF oxide formation is limited with the applied potential. During the oxide growth process at constant voltage (U) the current density (J) is decreasing exponentially with time (t). The film growth rate is decreases almost exponentially with the time, which means the film thickness is limited. Experimentally has been defined the thickness of the BTF is proportional to the applied potential.[47.]

Figure 1.10.: Aluminum oxide fomed by barrier type anodic oxidation and porous type anodic oxidation. [47.]

The PAA growth process is mainly depending on the current density (J). At potentiostatic (U is constant) conditions the current density is almost constant during the anodization. The stable current density is due to the constant thickness of the barrier layer at the pore bottom. The PAA thickness is linearly proportional to the total amount of the charge during the anodization. The diameter of the pores is depending on the applied potential and on the used electrolyte.[47.]

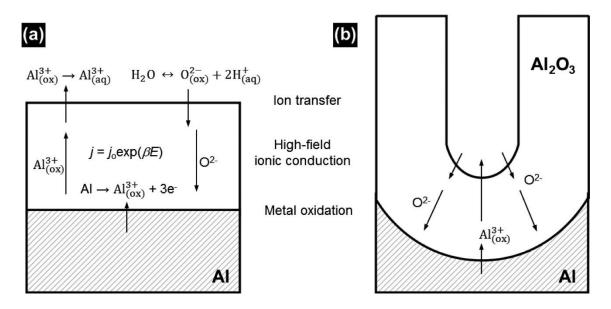

#### 1.2.1.1 Fundamental interfacial reactions

Empirical exponential dependence of the ionic current density (j) on the electric field (E) was established for aluminum anodizing. During the anodic oxide growth a high-field conditions are present. The current density (j) under high-field conditions can be related with the movement of the charged ions in the barrier oxide as well as the potential drop ( $\Delta U$ ) across the barrier oxide through the exponential law of Güntherschulze and Betz:

$$j = j_0 \exp\left(\frac{\beta \Delta U}{t_h}\right) \tag{19}$$

where  $j_0$  and  $\beta$  are material-dependent constants at a given temperature, and  $\Delta U/t_b$  is the effective electric field (E, usually  $10^6-10^7$  Vcm<sup>-1</sup>) impressed on the barrier layer with thickness  $t_b$ . For AAO a wide range of  $j_0$  and  $\beta$  values were published ( $j_0 = 3x10^4$  to  $10^{-18}$  Acm<sup>-2</sup> and  $\beta = 10^{-7}$  to  $5,1x10^{-6}$  cmV<sup>-1</sup>).

The anodic oxidation of metals in electrolytes are explained based on rate-determing steps for oxide formation in three different theories.

The Mott–Cabrera theory is explaining the ion transfer across the metal/oxide interface, the Verwey theory is using explanation for ion transfer through the oxide bulk, and the Dewald theory presents the ion transfer across the oxide/electrolyte interface.[47.]

In the point defect model of Chao et al.,[77.] the oxide film is assumed to contain a high concentration of non-interacting positive and negative point defects, and the rate-determining step for the oxide growth is assumed to be the transport of metal and oxide vacancies across the oxide film.

Above mentioned theories can explain the empirical relationship proposed by Güntershultz and Betz. On the other hand, transient experiments favorably indicate that the rate-determining step is the movement of charged ions within the oxide. [47.]

Figure 1.11.: Elementary interfacial reactions for barrier type (a.) and for porous type (b.) anodization. [47.]

The thickness of the consumed aluminum during anodization with 0,3M oxalic acid electrolyte is counted with equation

$$0.33I_a t = h_a \tag{20}$$

where  $I_a$  is the current density, t is time of the anodization and the  $h_a$  is the thickness of the consumed aluminum layer in nm.

## 1.2.2 Titanium dioxide

Titanium dioxide ( $TiO_2$ ) is a widely used material since the early  $20^{th}$  century. The properties of this binary oxide allow to use as a pigment in sunscreens, paints, toothpaste, etc. The discovery of the phenomenon of the photocatalytic splitting of water on  $TiO_2$  electrode under UV light in 1972 launched a wave of research based on  $TiO_2$ . Promising applications in areas ranging from photovoltaics, photo catalysis, gas sensors and non-volatile memories were developed and invented. The  $TiO_2$  is a widely used and easy modifiable material. The photoactivity, the sensing properties or the electrical behavior are depended on the crystallographic orientation, the doping, the surface structure, etc.

The  $TiO_2$  as a material could be prepared in several ways. In dependence of the preparation process the  $TiO_2$  producing is possible with several methods: [50.]

- a. sol-gel method

- b. micelle and inverse micelle method

- c. sol method

- d. hydrothermal method

- e. solvothermal method

- f. chemical vapor deposition

- g. physical vapor deposition

- h. electrochemical method

- i. sonochemical method

- j. microwave method

- k. mesoporous/nanoporous materials

- I. aerogels

- m. opal and photonic materials

- n. nanosheets.

Due to the length of the list, only some of the above-mentioned technologies will be characterized.[50.]

#### Sol-ge I method

The sol-gel method is a versatile process used in making various ceramic materials. In case of the  $TiO_2$  from hydrolysis of titanium precursor with sol-gel method the nanomaterial have been synthetized. The sol-gel prepared by mixing tetrabutyl-titanate or titanium isopropoxide in acetic acid is proper for preparation of nanorods with low diameter.  $TiO_2$  nanorods with diameter 5nm was synthetised with sol-gel method by Joo et al.[51.]

Sol-gel methods are often combined with PAA membranes for fabrication of  $TiO_2$  nanotubes (NT) and nanorods. Deposition of  $TiO_2$  into PAA template with well aligned parallel pores with well controlled dimensions is a cheap, low temperature easy controlled wet chemical process. The PAA template after the deposition of  $TiO_2$  is removed by wet etching. The dimensions of the deposited oxide array are depends on the PAA template pore alignments and dimensions.[50.][51.]

#### Physical vapor deposition (PVD)

PVD methods are variously used for metal layer depositions. The layer adhesion, the deposition speed or the various possibilities of set ups to control the material properties of the deposited layers are the biggest advantages of the PVD methods.

$TiO_2$  layers deposited by reactive radiofrequency magnetron sputtering system from highly pure Ti target at low argon/oxygen gas flow and crystallized to rutile phase are primary recommended for optoelectronic devices. The disadvantage of the RF magnetron sputtering is mainly the physical limitation of the deposition into deep narrow pores. [52.]

#### **Electrochemical method**

Electrochemical methods for preparation of  $TiO_2$  layers or structures could be distributed in two main groups. Electrodeposition of  $TiO_2$ , where the Ti or the  $TiO_2$  layer is deposited on the substrate, and anodic oxidation, where the previously deposited Ti layer is oxidized in electrolyte.

#### Electrodeposition

Electrodeposition is commonly used method to perform usually metallic coating on a surface by electrochemical reduction on the cathode side. The metallic ions are attracted to the cathodes surface and reduced to a metallic form. Based on the masking method the 2D geometrical shape is controlled by lithography techniques (masking by photoresist layers or using sacrificial layers removed by selective etchants).

The 3D shape of the reduced metals is prepared in assistance of supporting matrixes, as highly ordered porous anodic alumina oxides or other submicron structures.[53.]

#### **Electrochemical anodization**

Electrochemical anodization of valve metal oxides is a universal method with several possibilities. With anodic oxidation of the Ti layer, depending on the used electrolyte, from compact oxide layer — oxalic acid-based electrolytes — to different nanotube fields — ammonium fluoride-based electrolytes — can be prepared.

The anodized TiO<sub>2</sub> layers are mostly amorphous, the crystallographic orientation from anatase to brookite are achieved with annealing at higher temperatures. The crystallization process can be achieved for the same crystallographic orientation at different temperatures due to the anodizing conditions. The process of the Ti anodization for TiO<sub>2</sub> nanocolumns is explained in chapter 3.5 Anodization of Titanium.

#### Crystallography of the pure TiO<sub>2</sub>

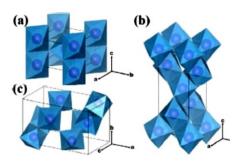

TiO<sub>2</sub> exists naturally mainly in three crystalline phases: anatase (tetragonal), rutile

(tetragonal), and brookite (orthorhombic) (Figure 1.12). Anatase and rutile have a tetragonal structure with a=0.536 nm and c=0.953 nm (anatase), a=0.459 nm and c=0.296 nm (rutile) and Brookite has an orthorhombic structure with a=0.915 nm, b=0.544 nm, and c=0.514 nm.[54.]

Figure 1.12.: Crystal structures of TiO<sub>2</sub> polymorphs: Rutile (a), Anatase (b), Brookite (c). The purple spheres represent Ti atom.[54.]

Among the different polymorphs, rutile is generally considered to be the most stable bulk phase, while at the nanoscale, anatase and brookite are more stable due to lower surface energy. The crystal phases are affected by the experimental conditions (synthesis method, annealing temperature, pH, duration etc.).[54.]

The XRD pattern of the  $TiO_2$  nanotube arrays before annealing did not contained obvious peak. The amorphous phase of the  $TiO_2$  NTA started to converse to anatase phase at approximately 250°C. From 250 to 650°C the relative intensity of the anatase peak is increasing. The anatase phase change observed at 650°C shown conversion of part of the anatase into rutile phase. With the increasing annealing temperature from 650°C up to 850°C the anatase phase is decreasing and the rutile phase is increasing.[55.]

Pure  $TiO_2$  synthetized by hydrothermal method conversed into  $TiO_2$  (B) has the same formula as  $TiO_2$ , it has more open framework structure, a relatively low density and large specific capacity than other polymorphs. This phenomenon began to grow applications in the fields of energy conversions as photocatalysis solar cells and lithium batteries.[55.]

# 2 AIM OF THE WORK

Considering the variability of the valve metal oxides preparation and the possibilities of its usage in electronics, the aim of this thesis is to seek a fabrication technique using self-ordered anodic alumina arrays with TiO<sub>2</sub> nanocolumns and investigate its electronic properties.

The particular aims of this thesis are:

- Preparation of the self-ordered AAO supporting matrix with self-grown TiO<sub>2</sub> nanocolumns and realization of the electric contacts for further measurements.

- Investigation of the functional material and the structure analysis of the nanocolumns grown at different conditions.

- Electrical characterization of prepared samples, evaluation of achieved resistive switching phenomenon.

# 3 EXPERIMENTAL

The fabrication complexity and expensive techniques used for memristor realization in HP lab (written in cap. 2.2) are not very popular in the most of research and industry laboratories. Even their idea is genius it could be further improved. Anodic oxidation of aluminum is a well-known process. This process can produce the porous films possessing high pore density, uniform pore size. The other important advantage is the versatility and low cost. [23.]

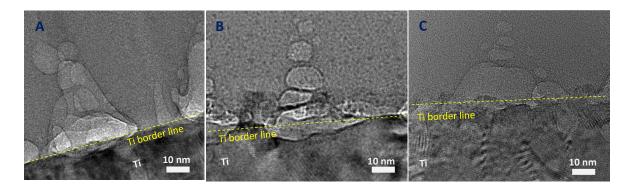

In 1999 Mozalev et al. published an article about the microresistors fabricated by anodic processes. [24.] They produced nanoscale metal-oxide coatings, using Ta-Al layers and anodic oxidation. Main advantage was the self-growing of  $tTa_2O_5$  nanostructures with high electrical resistance. Later in 2005, Mozalev et al. also characterized the growth and electrical transport properties of self-organized Ta–Al bilayers formed by anodization. [8.] During the material characterization of the cross-section sample of tantalum oxide nanohillocks in anodic aluminum oxide (AAO or porous anodic alumina PAA) layer, a non-homogenity of the oxygen concentration was detected. Using the information, it might be possible to prepare self-ordered memristive structures via anodization. [25.]

The schematic of the experimental plan (Table 2.) was set up with a purpose to compare different nanocolumn properties and find a way to prepare samples with resistive switching behavior. Samples, where resistive switching is achieved, will be analyzed in detail in electrical and in material point of view as well. If the sample was successfully prepared and it shown resistive switching behavior, the field can be green, if it was successfully prepared, but it is without resistive switching the field will be yellow. In case of failure at the fabrication, the field is red.

Table 2.: Experimental plan

| Anodization | Sweep rate            | Sweep rate  | Annealing set up |           |          |  |  |  |

|-------------|-----------------------|-------------|------------------|-----------|----------|--|--|--|

| potential   | for re-               | for re-     |                  |           |          |  |  |  |

|             | anodization           | anodization |                  |           |          |  |  |  |

|             | 0,2 V·s <sup>-1</sup> | 2 V·s⁻¹     | As-              | 500°C/2h  | 500°C/2h |  |  |  |

|             |                       |             | Anodized         | in Vacuum | in Air   |  |  |  |

| 40V         |                       |             |                  |           |          |  |  |  |

| 40V rA 100V |                       |             |                  |           |          |  |  |  |

| 40V rA 130V |                       |             |                  |           |          |  |  |  |

# 3.1 Layer preparation

The Ti layers, deposited by PVD evaporation or magnetron sputtering method, are not ideal for template-based anodization. Obviously in the evaporated/magnetron sputtered layers is observable a material stress or the layers crystallographic orientation is not uniform.

The Ion beam assisted deposition is a highly precise sputtering technique which fulfills every requirement of Ti layers for anodic oxidation.

Thermal-oxide-coated Si wafers of diameters 100 mm were used as starting substrates. Titanium layers with thickness 300 nm were deposited by sputtering of 99.95% Ti target, using an ion beam sputtering. The deposition chamber was initially evacuated to  $5 \cdot 10^{-7}$  mbar, with subsequent sputtering using 99.998% argon at  $5 \cdot 10^{-3}$  mbar. The Ti/Al bilayers (aluminum-on-titanium) were prepared by sequential sputter-deposition of Ti and Al layers, respectively 100 nm (Ti) and 100 to 1000nm (Al) thick.

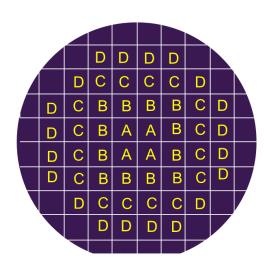

The wafer was cut on pieces with dimension 1x1 cm and categorized in four groups, based on Al thickness. The rest of the wafer was considered as scrap pieces, with a thinnest Al layer. (Figure 3.1.)

Figure 3.1.: Wafer drawing with marked section groups. The wafer was cutted into 1x1 cm pieces with diamond scratcher.

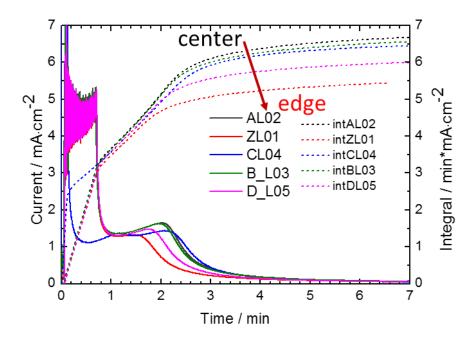

Based on previous experiences about anodization of sputtered Al layers a non-uniform layer thickness was observed. The thickness differences may cause undesirable inaccuracy mainly during two step anodization, where the precise thickness control during the Al anodizing is obligatory. The different anodization times are presented in Figure 3.2.

Figure 3.2.: Current time curves of anodized Al layer sputtered by IBAD. Anodization was performed at different wafer positions. The integral of the curves showing clearly, the thickness of the Al layer from the center to the edge is decreasing.

#### 3.2 Anodization of Aluminum

Valve metals as Al, Ti, Ta, W, are specific metals which are suitable for anodic oxidation.

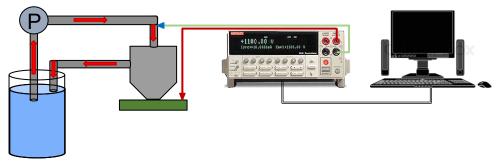

The first part of the experimental work is optimization of the anodic oxidation of Ti/Al structures. The initial surface was sputter-deposited metal bilayer of Ti/Al on the silicon wafer (previously covered with 500 nm of SiO2). Titanium layer with thickness of 300 nm was covered with 550 nm thick Al layer. The anodization was performed at 5 °C with a 0.3 M oxalic acid solution at the circulation speed of 70 mL/min. The apparatus was equipped with poly-tetrafluor-ethylene (PTFE ) cylindrical head with internal diameter 6.9 mm equipped with a stainless steel electrode. (Figure 3.3.)

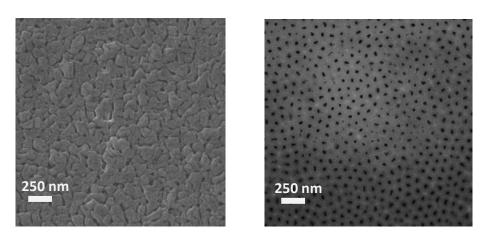

During the anodizing process, the current was always limited to 5 mA and the potential for the aluminum layer was constantly kept at 40 V. The diameter of the pores in AAO is approximately 36-40 nm. The surface of the AAO for more detailed evaluation was chemically decorated with selective AAO etchant. (Figure 3.4.)

Figure 3.3.: Schematic view of the anodization station.

Figure 3.4.: Surface of the AAO template anodized at 40V before chemical decoration (left) and after decoration for 20 seconds (right).

# 3.3 One step anodization

The first part of the experimental work is optimization of the anodic oxidation of Ti-Al structures. The initial surface was sputter-deposited metal bilayer of Ti/Al on the silicon wafer (previously covered with 500 nm of SiO2). Titanium layer with thickness of 300 nm was covered with 550 nm thick Al layer. The anodization was performed at 5 °C with a 0.3 M oxalic acid solution at the circulation speed of 70 mL/min. The apparatus was equipped with poly-tetrafluor-ethylene (PTFE ) head with internal diameter 6.9 mm equipped with a stainless steel electrode.

During the anodizing process, the current was always limited to 5 mA·cm<sup>-2</sup> and the potential for the aluminum layer was constantly kept at 40 V. The diameter of the pores in AAO is approximately 40–50 nm.

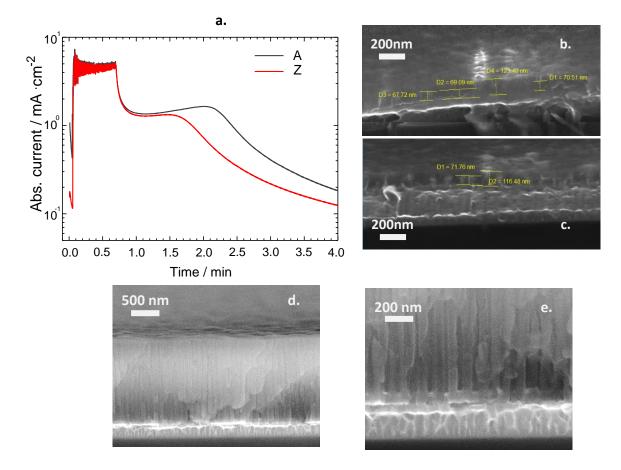

Anodization of the titanium layers were provided at potential of 40 V and 60 V (see Figure 3.5.). Both potentials are suitable to prepare self-grown  $TiO_2$  nanowires in AAO, the difference is in height of  $TiO_2$  nanowires in the pores. At the potential of 60 V the  $TiO_2$  columns are higher than at 40 V. The thickness of the AAO has no influence on the length of the nanocolumns. (Figure 3.6.)

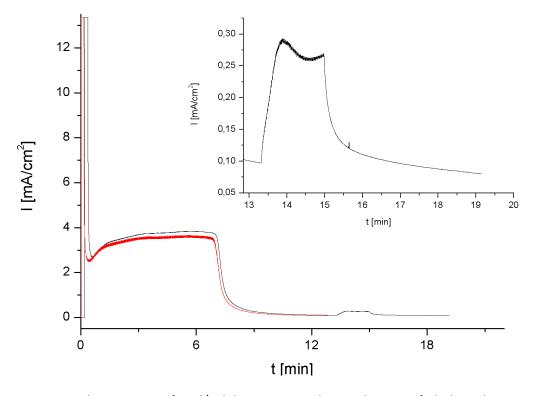

Figure 3.5.: Anodization curve for Al/Ti bilayer. During the anodization of Al, the voltage was kept at 40 V for both sample (red and black curves). The first sample was anodized for 13 min including Ti anodizing at 40 V (red curve). The second sample was anodized for 19.25 min. In case of the second sample after 13.5 minutes the voltage was increased from 40 to 60 V (black curve)

After the first successful and repeatable test the anodization parameters and the type of the samples for comparison purposes were fixed.

The temperature of the electrolyte for the anodization was fixed for 5°C, the flow rate of the electrolyte in the cylindrical PTFE cell was fixed for 70 ml. The anodization voltage for the aluminum layer and for the titanium oxide bulks was constant as well (40 V).

Three column length respectively anodization potential was fixed too. For the shortest column length 40V was used and for higher nanocolumns 100V were applied.

Figure 3.6.: Anodization of an 80 nm thin Al layer at potential 40 V and re-anodized at 60V. The current time curve shows the difference between the anodization time of the Al layer at the center of the wafer and on the edge (the re-anodization part of the curve was removed for better visualisation). The differencies in the final AAO layer thicknesses are approximatley -6 % at the edge in comparison with an anodized center. The re-anodized nanocolumns are about 70 nm.

The figures d and e are presenting an AAO prepared from 1000nm thick Al layer. The final AAO layer is extremly thick in comparison with tha layers in figures b and c, however the height of the nanocolumns are about 70nm, which means the thickness of the AAO has no influence on the growing process of the  $TiO_2$  nanocolumn arrays.

# 3.4 Two step anodization

In previous chapter the one step anodizing and re-anodizing process was explained. The two-step anodization from the electrochemical point of view is like the one step anodization. The main difference lies in the way of the AAO control. Due to the physical limitation of the AAO growing mechanism, the layer thickness control is possible only with removement of the undesirable layer thickness.

Differences between the final AAO thickness and the initial AAO thickness is depending on the length of the nanocolumns. The height of the nanocolumns is controlled by the reanodization potential and the initial thickness of the AAO was counted by equation 20 written in chapter 1.2.1.1. The calculation was verified with several thickness measurements from cross sections after the anodization. The samples were marked from the back side with dentification sign showing from which part of the silicon wafer was the sample taken. The distribution of the samples was explained in previous chapter 3.1. *Layer preparation*. The samples from the same bar have identic thicknesses and the undesirable layer thickness is definable precisely and easily.

The thickness of the consumed AL layer and the time of the anodization to reach the proper thickness of the undesirable layer specified as 6,5Å·s<sup>-1</sup>. The anodization of the aluminum was performed with identic setup for all experiments and therefore the speed of the Al layer consumption was in every case the same.

The process of anodization and the process of chemical etching of the AAO before the second anodization step is provided in the same anodization cell without dismounting. Rinsing of the AAO surface after the anodization was done by constant circulating of demineralized water (200 ml of  $H_2O$  at room temperature for every rinsing respectively). The selective etching process with tempered etchant to  $58^{\circ}C$  at constant circulation for 20 min at speed 75ml/minute was implemented. The selective AAO etchant for the AAO decoration and for the removal was the same. The etching was finished with rinsing to remove the etchant residues from the surface.

Second step of the anodizing process was performed in an identic way as the one step anodization. The results of the two-step anodization are presented in figures Figure 3.7., Figure 3.8. The advantages and disadvantages of between the one step and two step anodization are presented in Table 3.

Table 3. Comparison of the one- and the two-step anodization – advantages, disadvantages.

| One-step anodization                                                                                                                                                          | Two-step anodization                                                                                                                                                                                                                                                              |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Advantages                                                                                                                                                                    | Advantages                                                                                                                                                                                                                                                                        |  |

| Continuity of the anodizing  Probability of the structure/layer contamination is low  Probability of the trapped air bubbles in the apparatus above the sample surface is low | Thickness of the AAO layer is controlled  Blind pores are occurring rarely  Deposition of top electrode with PVD techniques primary on the top of the nanocolumns.                                                                                                                |  |

| Disadvantages                                                                                                                                                                 | Disadvantages                                                                                                                                                                                                                                                                     |  |

| The thickness of the final AAO layer depends on the thickness of the initial Al layer                                                                                         | Probability of the trapped air bubbles in the apparatus above the sample surface is higher, than at one step anodization  Probability of the structure/layer contamination is higher  The total time for the sample preparation is few times higher, than at one step anodization |  |

If the thickness of the AAO layer or the minimal height difference between the nanocolumns and nanopores is required, the two-step anodization can be an option. The final AAO must have thickness min. 2x height of the barrier layer (for example in case of 35nm thick barrier layer the final thinnest AAO must have 70 nm or higher). Therefore, the two-step anodization is appropriate only for re-anodized nanocolumns.

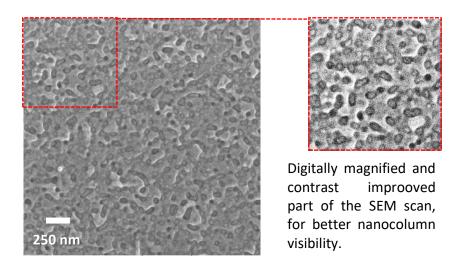

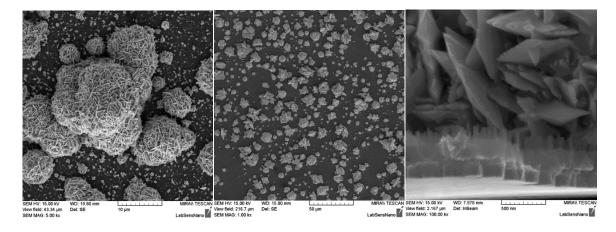

The nanocolumns after two step anodization and Ti re-anodization respectively should be visible during SEM observation. For better visibility the surface was decorated for 20 sec in selective etchant for AAO. (Figure 3.8.)

Figure 3.7.: AAO surface (left) after the second anodizing before re-anodization of Ti. Tilted cross section (right) about the AAO template before reanodization of Ti. After a re-anodization the pores should be filled with  $TiO_2$ . The not completely flat AAO surface has no negative effect on a later magnetron sputtering or on the electrical contacts.

Figure 3.8.: Surface of a re-anodized AAO template prepared with two step anodization.

The surface was decorated in selective AAO etchant for 20 seconds for better visibility. The top of the nanocolumns are clearly visible.

#### 3.5 Anodization of Titanium

The anodization of the Ti layer in aqueous oxalic acid solution with sequential anodizing technique was realized. The anodizing process of the Ti layer is starting with the formation of the  $TiO_2$  nanodots at the bottom of the AAO pores on the barrier layer. The speed of the anodic reaction at constant voltage is depending mainly on the electrolyte temperature. Higher is the temperature, the reaction is faster. At higher electrolyte temperature the oxidation process is faster than the growing speed, therefore the nanostructure can be instable and dissolve during the anodization causing a breakthrough across the layer. Due to this phenomenon after several experiments 5°C was chosen as an electrolyte temperature.

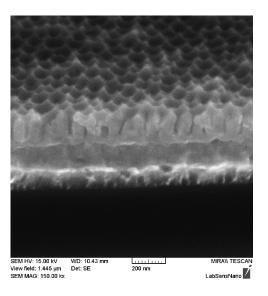

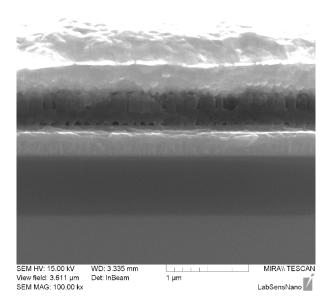

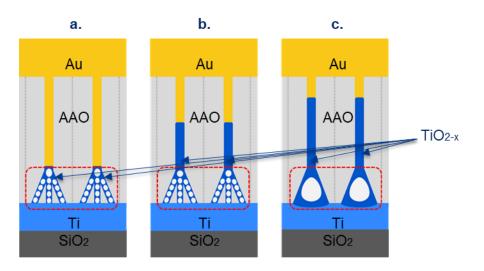

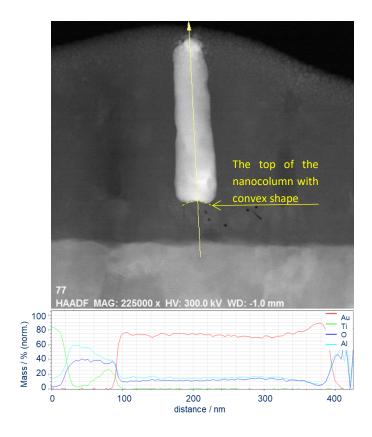

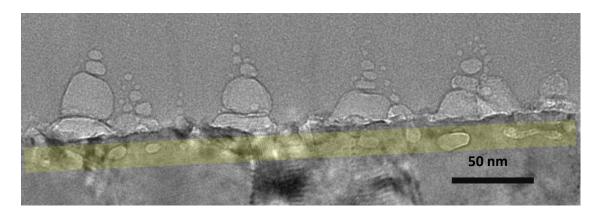

Titanium ion migration through the AAO barrier layer is depending on the temperature, on the anodization potential and current. Basic column, which is a titanium dioxide column anodized at potential 40 V as an AAO was prepared, has two main parts, the root and the column itself.

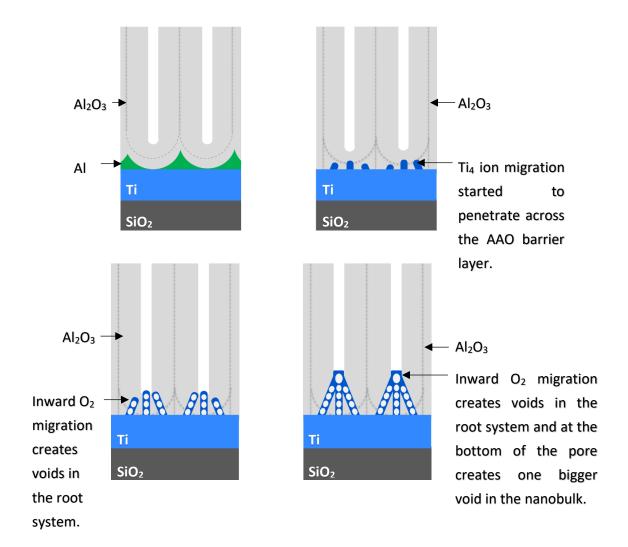

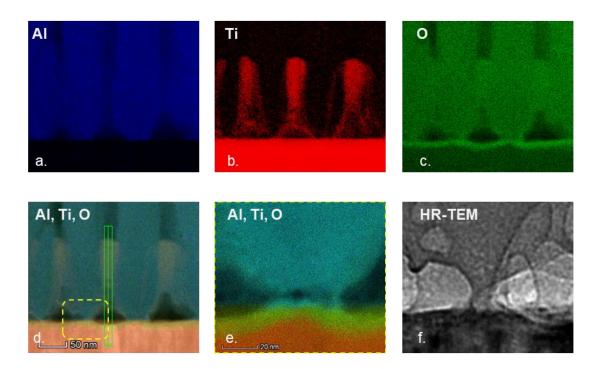

The Ti4+ ion migration through the AAO barrier layer are leading to a growing mechanism. Higher anodic potential leads to a better anodic titanium oxide (ATO) growing and the AAO nanopore filling redounds ATO nanocolumns. However, the anodizing process results titanium oxide growing, also an inward  $O_2$  ion migration appears on the interface of the AAO barrier and Ti layer. (Figure 3.9.)

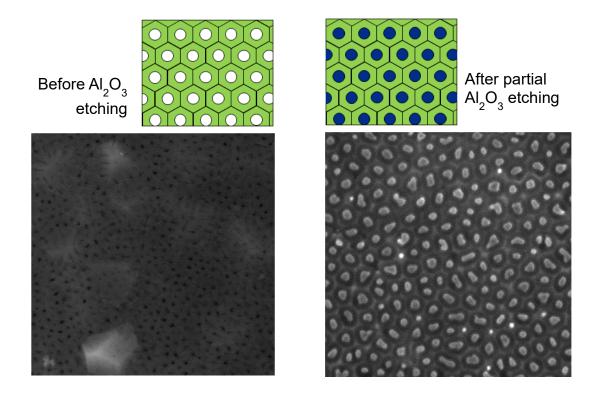

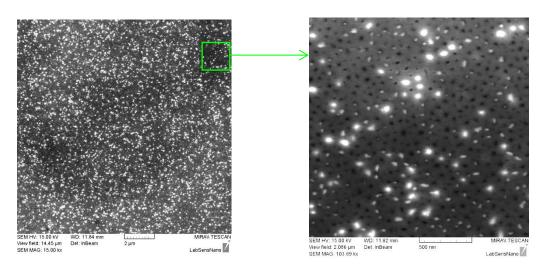

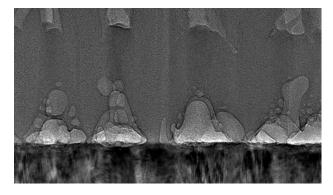

The I–t curves from the anodization process were presented in chapter 1.3, where the correlation between the anodization time and the AAO thickness was shown. To control how many pores are filled with nanocolumns, the AAO was removed. The pore saturation is around 95 to 100%. (Figure 3.10.) After a partial AAO removal the nanocolumns becomes visible, however the most of the nanocolumns were felt down or removed after a full template removal.

Figure 3.9.: Schematic view of the TiO<sub>2</sub> growing through the AAO barrier layer at potential 40V. During the anodization at first all of Al is anodized (a.), then the Ti starts to penetrate through the barrier layer at the thinnest places respectively at the places with a lowest resistence.(b) The inward O<sub>2</sub> migration creates voids in the stems and later in the cap on the nanocolumn as well.(c., d.)

Figure 3.10.: The pore saturation was controlled by a partial AAO removal. The surface of the AAO after the re-anodization (on left) before decoration, and the nanocolumns in the partially removed AAO template (on right). To see the effectivity of the saturation in detail, after an AAO removal only a part of the surface is shown.

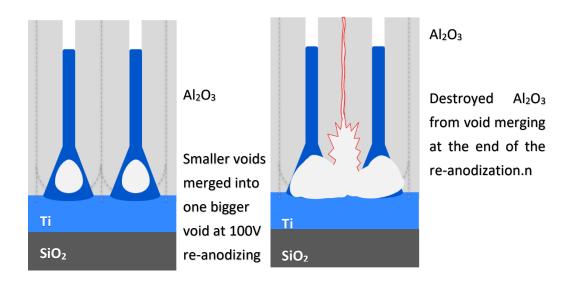

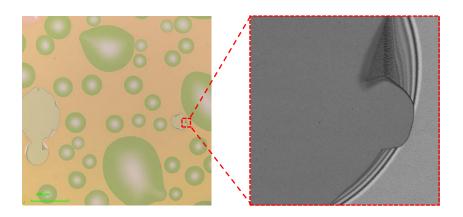

The negative effect of the voids, besides the nanocolumns are not stable after AAO removal, is the possible lentil surface during the anodization. Where the sample was ruptured or over-burned due to the high current density in a local point. Based on these experiences at anodic oxidizing we initiate higher amount of O<sub>2</sub>, migrating into the barrier layer. The shape of the roots and amount of the root filaments are changing simultaneously. During a long time finishing the voids are merging filling up the barrier layer. Later, the voids are spreading above the Ti layer and breaks up the AAO template. (Figure 3.12. Figure 3.12)

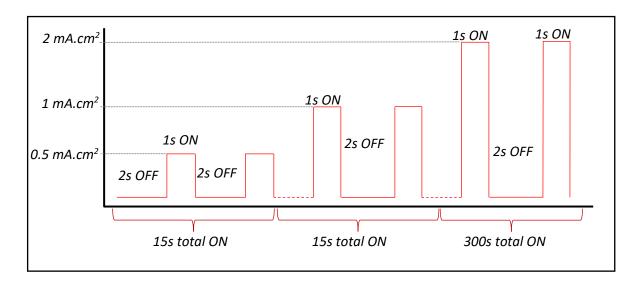

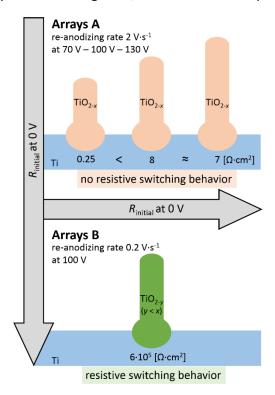

Re-anodizing sweep rate at reaching of the final re-anodizing potential has influence on the grown speed and on the electrical properties of the columns as well. This chapter briefly explain the differences in the grown process at sweep rate difference from  $0.2 \text{ V} \cdot \text{s}^{-1}$  to  $2 \text{ V} \cdot \text{s}^{-1}$ .

Figure 3.11.: The re-anodization at potential 100V reached at slow sweep rate leads to long nanocolumn growing, but the inward O<sub>2</sub> migration, respectively the voids in the nanocolumn in the AAO pores are not present. The root system in the AAO barrier layer due to the re-anodization is changing its structure. The voids from the O<sub>2</sub> migration are fulfilling the barrier layer and transforms the stem structure into one flask shaped root with 1 to 3 voids. (left) The long-time anodization finishing leads to a void merging between the roots and to a layer destruction. (right)

Figure 3.12.: Lentil like damage on the AAO layer caused by long finishing anodization. (left)

The magnified damage after eruption is magnified on a laser scanned image

(right)

The nanocolumn grown speed is higher and the final nanocolumns are about 10% higher than at lower speed. If the growing process is faster the inward  $O_2$  ion migration is causing bubble merging slower than at lower sweep rate. The nanocolumn can be anodized at higher potential as well (at 130V without any AAO damage).

The different grown speed assuming different material or root structures and electrical properties respectively.

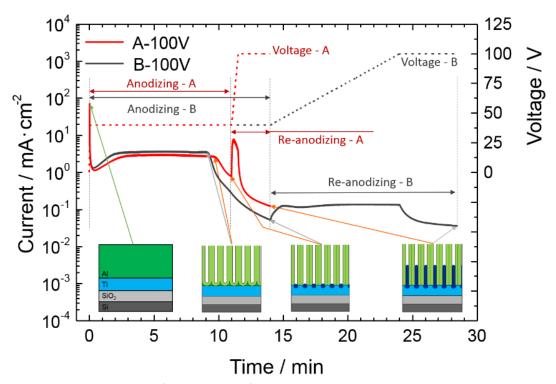

The differences in low and high sweep rate are presented (Figure 3.13), where the anodizing charts are explained the growing phases are illustrated.

Figure 3.13.: Comparison of sweep rate of re-anodizing potential. Current-time and potential-time transients recorded during the AAO-assisted anodization of arrays A-100V (red) and B-100V (black). The different regions (anodizing and re-anodizing) are marked and the images show schematically the arrays at the corresponding current or potential changes.[43.]

# 3.6 Deposition of top electrode arrays

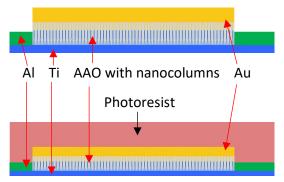

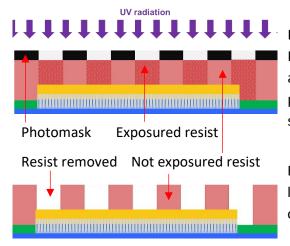

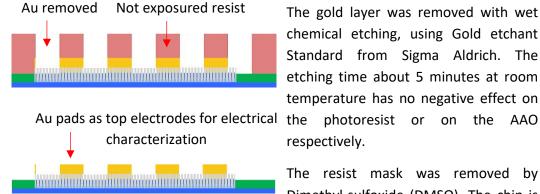

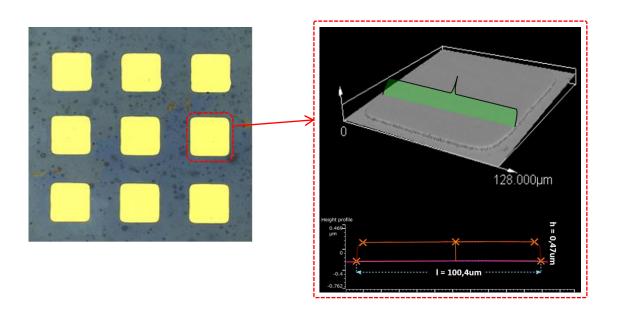

This chapter is dealing with the fabrication of the metal contact pads of TiO<sub>2</sub>self-ordered nanoarrays for electrical characterization. The bottom electrode of this two-terminal element is the Ti layer itself. The highly conductive pure metal layer is perfectly connected with the nano column array and it is easily accessible from the side of the chip.

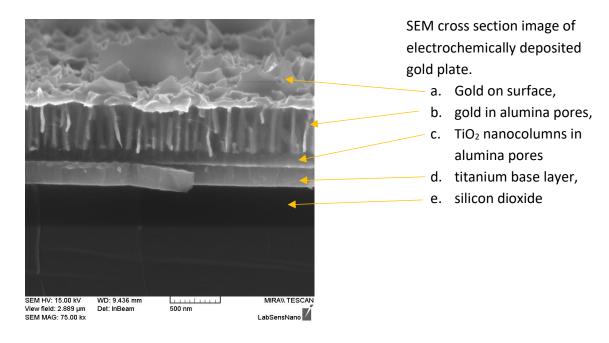

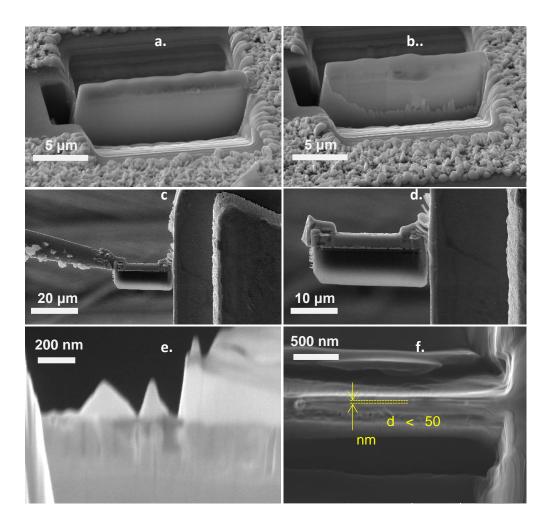

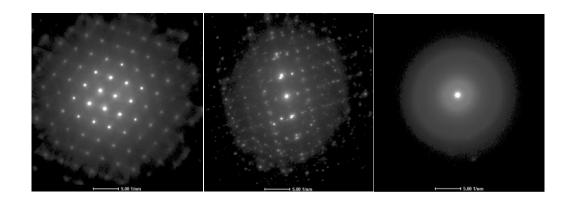

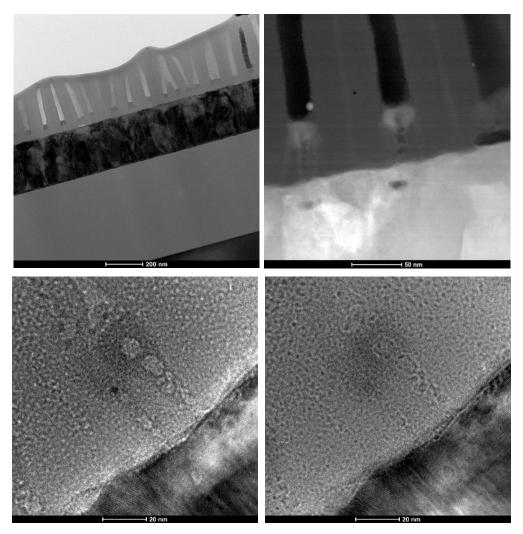

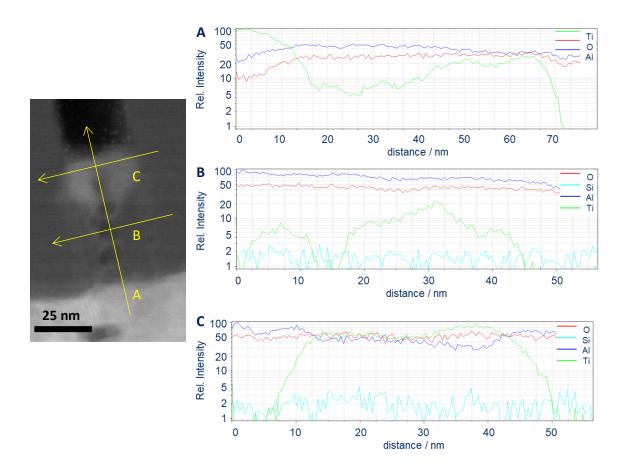

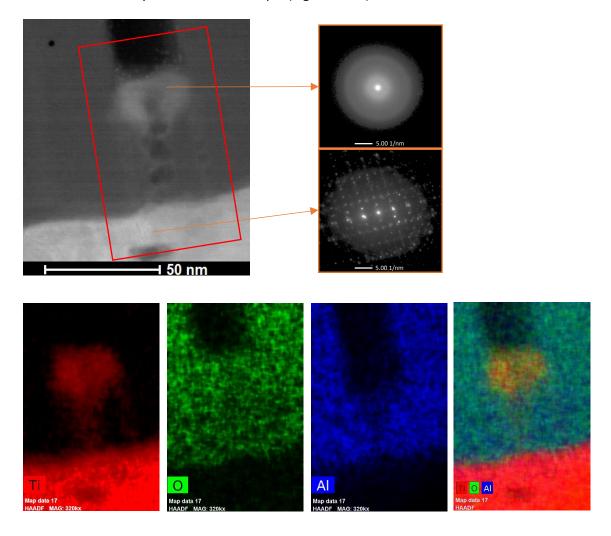

The top electrode material based on the literature should be a noble metal, as platinum or gold layer. Regarding to the available techniques and sources electrochemically or magnetron sputtered gold layers were chosen. The magnetron sputtering of Au was performed at standard set ups (prepared in CEITEC Core facilities in form of order) and therefor only the electrodeposition will be discussed in detail.