# VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

BRNO UNIVERSITY OF TECHNOLOGY

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ ÚSTAV MIKROELEKTRONIKY

FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION DEPARTMENT OF MICROELECTRONICS

# RESIDUE NUMBER SYSTEM BASED BUILDING BLOCKS FOR APPLICATIONS IN DIGITAL SIGNAL PROCESSING

DIZERTAČNÍ PRÁCE DOCTORAL THESIS

AUTOR PRÁCE AUTHOR Ing. DINA YOUNES

BRNO 2013

# VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

BRNO UNIVERSITY OF TECHNOLOGY

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ ÚSTAV MIKROELEKTRONIKY

FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION DEPARTMENT OF MICROELECTRONICS

# RESIDUE NUMBER SYSTEM BASED BUILDING BLOCKS FOR APPLICATIONS IN DIGITAL SIGNAL PROCESSING

VYUŽITÍ SYSTÉMU ZBYTKOVÝCH TŘÍD PRO ZPRACOVÁNÍ DIGITÁLNÍCH SIGNÁLŮ

DIZERTAČNÍ PRÁCE DOCTORAL THESIS

AUTOR PRÁCE AUTHOR Ing. DINA YOUNES

VEDOUCÍ PRÁCE SUPERVISOR doc. Ing. PAVEL ŠTEFFAN, Ph.D.

BRNO 2013

### Abstract

This doctoral thesis deals with designing residue number system based building blocks to enhance the performance of digital signal processing applications.

The residue number system (RNS) is a non-weighted number system that provides carry-free, parallel, high speed, secure and fault tolerant arithmetic operations. These features make it very attractive to be used in high-performance and fault tolerant digital signal processing (DSP) applications.

A typical RNS system consists of three main components; the first one is the binary to residue converter that computes the RNS equivalent of the inputs represented in the binary number system. The second component in this system is parallel residue arithmetic units that perform arithmetic operations on the operands already represented in RNS. The last component is the residue to binary converter, which converts the outputs back into their binary representation.

The main aim of this thesis was to propose novel structures of the basic components of this system in order to be later used as fundamental units in DSP applications.

This thesis encloses improving and designing novel structures of these components, simulating and verifying their efficiency via FPGA implementation. In addition to suggesting novel structures of basic RNS components, a detailed study on different moduli sets that compares and determines the most efficient one for different dynamic range requirements is also presented. One of the main outcomes of this thesis is concluding and verifying the main condition that should be met when choosing a moduli set, in order to improve the timing performance of a DSP application. An RNS-based image processing application is also proposed. Its efficiency, in terms of timing performance and power consumption, is proved via comparing it with a binary-based one. Finally, the main considerations that should be taken into account when choosing to use the binary number system or RNS are also discussed in details.

# Keywords

Residue number system, digital signal processing, modular arithmetic, moduli set, dynamic range, binary to RNS converter, RNS to binary converter, RNS-based application, parallel processing, power reduced DSP application, FPGA implementation.

### Abstrakt

Předkládaná disertační práce se zabývá návrhem základních bloků v systému zbytkových tříd pro zvýšení výkonu aplikací určených pro digitální zpracování signálů (DSP).

Systém zbytkových tříd (RNS) je neváhová číselná soustava, jež umožňuje provádět paralelizovatelné, vysokorychlostní, bezpečné a proti chybám odolné aritmetické operace, které jsou zpracovávány bez přenosu mezi řády. Tyto vlastnosti jej činí značně perspektivním pro použití v DSP aplikacích náročných na výpočetní výkon a odolných proti chybám.

Typický RNS systém se skládá ze tří hlavních částí: převodníku z binárního kódu do RNS, který počítá ekvivalent vstupních binárních hodnot v systému zbytkových tříd, dále jsou to paralelně řazené RNS aritmetické jednotky, které provádějí aritmetické operace s operandy již převedenými do RNS. Poslední část pak tvoří převodník z RNS do binárního kódu, který převádí výsledek zpět do výchozího binárního kódu.

Hlavním cílem této disertační práce bylo navrhnout nové struktury základních bloků výše zmiňovaného systému zbytkových tříd, které mohou být využity v aplikacích DSP.

Tato disertační práce předkládá zlepšení a návrhy nových struktur komponent RNS, simulaci a také ověření jejich funkčnosti prostřednictvím implementace v obvodech FPGA. Kromě návrhů nové struktury základních komponentů RNS je prezentován také podrobný výzkum různých sad modulů, který je srovnává a determinuje nejefektivnější sadu pro různé dynamické rozsahy. Dalším z klíčových přínosů disertační práce je objevení a ověření podmínky určující výběr optimální sady modulů, která umožňuje zvýšit výkonnost aplikací DSP. Dále byla navržena aplikace pro zpracování obrazu využívající RNS, která má vůči klasické binární implementanci nižší spotřebu a vyšší maximální pracovní frekvenci. V závěru práce byla vyhodnocena hlavní kritéria při rozhodování, zda je vhodnější pro danou aplikaci využít binární číselnou soustavu nebo RNS.

## Klíčová slova

Systém zbytkových tříd, digitální zpracování signálu, modulární aritmetika, sada modulů, dynamický rozsah, převodník z binární soustavy do RNS, převodník z RNS do binární soustavy, aplikace RNS, paralelní výpočty, aplikace DSP s nízkou spotřebou, implementace do FPGA.

YOUNES, D. *Residue number system based building blocks for applications in digital signal processing.* Brno: Brno University of Technology, Faculty of Electrical Engineering and Communication, Department of Microelectronics, 2013, 106 p. Supervised by doc. Ing. Pavel Šteffan, Ph.D.

## Declaration

I declare that I have elaborated my doctoral thesis on the theme of "Residue number system based building blocks for applications in digital signal processing" independently, under the supervision of the doctoral thesis supervisor and with the use of technical literature and other sources of information which are all quoted in the thesis and detailed in the list of literature at the end of the thesis.

As the author of the doctoral thesis I furthermore declare that, concerning the creation of this doctoral thesis, I have not infringed any copyright. In particular, I have not unlawfully encroached on anyone's personal copyright and I am fully aware of the consequences in the case of breaking Regulation S 11 and the following of the Copyright Act No 121/2000 Vol., including the possible consequences of criminal law resulted from Regulation S 152 of Criminal Act No 140/1961 Vol.

Brno .....

(author's signature)

### Acknowledgment

This doctoral thesis would not have been possible without the advice, guidance and help of the kind people around me who encouraged and supported me during this work.

First, I would like to express my deep gratitude to my advisor doc. Ing. Pavel Šteffan, Ph.D. for his support, guidance and help during the past four years I worked and studied at the Department of Microelectronics, Brno University of Technology.

I am very thankful to prof. Ing. Vladislav Musil, CSc. head of the Department of Microelectronics for his priceless advices, suggestions and continuous assistance during my work on Ph.D. thesis.

I would like to thank all other members of the Department of Microelectronics, who assisted me with advice or comment, to all my colleagues.

Finally, my great thanks belong to my parents, sister and husband who always believed in me and have always been my biggest supporter.

# **Table of Contents**

|                  | ST OF ABBREVIATIONS                                                                                                                                                        | .10                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| LI               | ST OF FIGURES                                                                                                                                                              | .11                                                             |

| LI               | ST OF TABLES                                                                                                                                                               | .13                                                             |

| 1                | INTRODUCTION                                                                                                                                                               | .16                                                             |

| 2                | STATE OF THE ART                                                                                                                                                           | .19                                                             |

|                  | <ul> <li>2.1 MODULI SET SELECTION</li></ul>                                                                                                                                | .19<br>.21<br>.23<br>.25<br>.25<br>.27<br>.27<br>.28            |

|                  | 2.4 RNS Applications                                                                                                                                                       | .31                                                             |

| 3                | AIMS OF DISSERTATION                                                                                                                                                       | .34                                                             |

| 4                | DISSERTATION RESULTS                                                                                                                                                       | .35                                                             |

| 4                | 4.1 THE MOST EFFICIENT MODULI SET FOR EACH DYNAMIC RANGE                                                                                                                   |                                                                 |

|                  | converters based on different moduli sets                                                                                                                                  |                                                                 |

|                  |                                                                                                                                                                            |                                                                 |

|                  | 4.1.2 The most efficient set for each dynamic range requirement                                                                                                            | .38                                                             |

|                  | 4.1.2 The most efficient set for each dynamic range requirement                                                                                                            | .38<br>.42                                                      |

|                  | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li> <li>4.2 PROPOSED FORWARD CONVERTER</li> <li>4.3 PROPOSED RESIDUE ARITHMETIC UNITS</li> </ul> | .38<br>.42<br>.45                                               |

|                  | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li> <li>4.2 PROPOSED FORWARD CONVERTER</li> <li>4.3 PROPOSED RESIDUE ARITHMETIC UNITS</li></ul>  | . 38<br>. 42<br>. 45<br>. 45                                    |

|                  | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | . 38<br>. 42<br>. 45<br>. 45<br>. 51                            |

| 4                | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li> <li>4.2 PROPOSED FORWARD CONVERTER</li> <li>4.3 PROPOSED RESIDUE ARITHMETIC UNITS</li></ul>  | . 38<br>. 42<br>. 45<br>. 45<br>. 51<br>. 51                    |

| 4                | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | 38<br>42<br>45<br>45<br>51<br>51<br>55                          |

| 4                | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | 38<br>42<br>45<br>51<br>51<br>55<br>55                          |

| 4                | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | 38<br>42<br>45<br>51<br>51<br>55<br>55<br>60                    |

| 2                | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | 38<br>42<br>45<br>51<br>51<br>55<br>55<br>60                    |

| 2                | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | . 38<br>.42<br>.45<br>.51<br>.51<br>.55<br>.55<br>.60<br>.66    |

| 2                | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | 38<br>.42<br>45<br>51<br>51<br>55<br>60<br>66                   |

| 2                | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | 38<br>.42<br>45<br>51<br>51<br>55<br>60<br>66                   |

| 2                | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | 38<br>42<br>45<br>51<br>51<br>55<br>60<br>66                    |

| 2                | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | 38<br>42<br>45<br>51<br>55<br>60<br>66<br>68                    |

| 2<br>2<br>2<br>E | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | 38<br>42<br>45<br>51<br>55<br>60<br>66<br>68                    |

| 2<br>2<br>2<br>E | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | 38<br>.42<br>45<br>51<br>55<br>60<br>66<br>68<br>70<br>72<br>74 |

| 2<br>2<br>2<br>E | <ul> <li>4.1.2 The most efficient set for each dynamic range requirement</li></ul>                                                                                         | 38<br>42<br>45<br>51<br>55<br>60<br>66<br>68<br>70<br>72<br>74  |

| 4.7.3 Performance evaluation and comparison                 | 79  |

|-------------------------------------------------------------|-----|

| 4.8 WHEN TO USE THE RNS (BINARY VS. RNS)                    |     |

| 4.8.1 The effect of the critical modulo within a moduli set | 81  |

| 4.8.2 When is RNS superior than binary number system        | 84  |

| 5 CONCLUSIONS                                               | 91  |

| 5.1 FINAL REMARKS                                           | 91  |

| BIBLIOGRAPHY                                                | 93  |

| AUTHOR'S PUBLICATIONS                                       | 99  |

| 6 APPENDIX                                                  | 100 |

|                                                             |     |

# List of Abbreviations

| BAU                                                              | binary arithmetic unit                                                                                                                                                                                                                           |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BNS                                                              | binary number system                                                                                                                                                                                                                             |

| CRT                                                              | Chinese remainder theorem                                                                                                                                                                                                                        |

| CPA                                                              | carry propagate adder                                                                                                                                                                                                                            |

| CSA                                                              | carry save adder                                                                                                                                                                                                                                 |

| CSA-EAC                                                          | carry save adder with end around carry                                                                                                                                                                                                           |

| DR                                                               | dynamic range                                                                                                                                                                                                                                    |

| DSP                                                              | digital signal processing                                                                                                                                                                                                                        |

| EAC                                                              | end around carry                                                                                                                                                                                                                                 |

| FA                                                               | full adder                                                                                                                                                                                                                                       |

| FC                                                               | forward converter (binary to residue converter)                                                                                                                                                                                                  |

| FIR filter                                                       | finite impulse response filter                                                                                                                                                                                                                   |

| FPGA                                                             | field programmable gate array                                                                                                                                                                                                                    |

|                                                                  |                                                                                                                                                                                                                                                  |

| GCD                                                              | greatest common divisor                                                                                                                                                                                                                          |

| GCD<br>HA                                                        | greatest common divisor<br>half adder                                                                                                                                                                                                            |

|                                                                  |                                                                                                                                                                                                                                                  |

| НА                                                               | half adder                                                                                                                                                                                                                                       |

| HA<br>IIR filter                                                 | half adder<br>infinite impulse response filter                                                                                                                                                                                                   |

| HA<br>IIR filter<br>LUT                                          | half adder<br>infinite impulse response filter<br>look-up table                                                                                                                                                                                  |

| HA<br>IIR filter<br>LUT<br>MRC                                   | half adder<br>infinite impulse response filter<br>look-up table<br>mixed radix conversion                                                                                                                                                        |

| HA<br>IIR filter<br>LUT<br>MRC<br>MSB                            | half adder<br>infinite impulse response filter<br>look-up table<br>mixed radix conversion<br>most significant bit                                                                                                                                |

| HA<br>IIR filter<br>LUT<br>MRC<br>MSB<br>RAM                     | half adder<br>infinite impulse response filter<br>look-up table<br>mixed radix conversion<br>most significant bit<br>random access memory                                                                                                        |

| HA<br>IIR filter<br>LUT<br>MRC<br>MSB<br>RAM<br>RAU              | half adder<br>infinite impulse response filter<br>look-up table<br>mixed radix conversion<br>most significant bit<br>random access memory<br>residue arithmetic unit                                                                             |

| HA<br>IIR filter<br>LUT<br>MRC<br>MSB<br>RAM<br>RAU<br>RAU       | half adder<br>infinite impulse response filter<br>look-up table<br>mixed radix conversion<br>most significant bit<br>random access memory<br>residue arithmetic unit<br>reverse converter (residue to binary converter)                          |

| HA<br>IIR filter<br>LUT<br>MRC<br>MSB<br>RAM<br>RAU<br>RC<br>RNS | half adder<br>infinite impulse response filter<br>look-up table<br>mixed radix conversion<br>most significant bit<br>random access memory<br>residue arithmetic unit<br>reverse converter (residue to binary converter)<br>residue number system |

# List of Figures

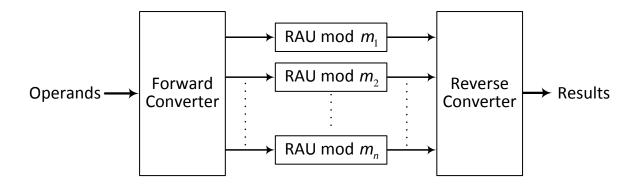

| Fig. 1.1: The architecture of the residue number system (RNS)17                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------|

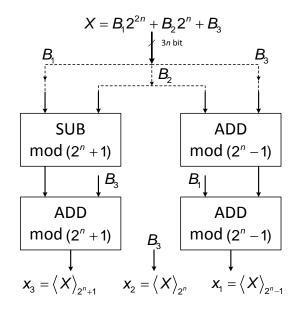

| <b>Fig. 2.1:</b> RNS forward converter for the moduli set $\{2^n - 1, 2^n, 2^n + 1\}$ [1]22                                               |

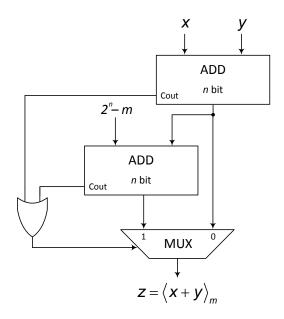

| <b>Fig. 2.2:</b> The structure of general modulo adder [22]                                                                               |

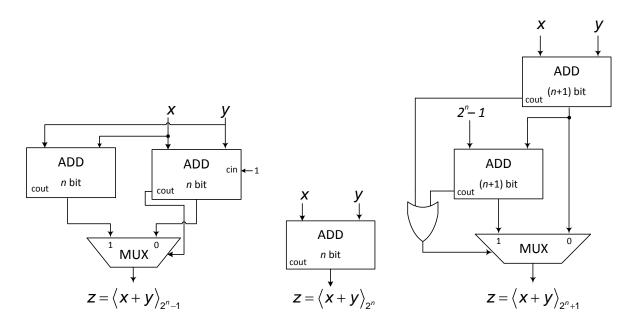

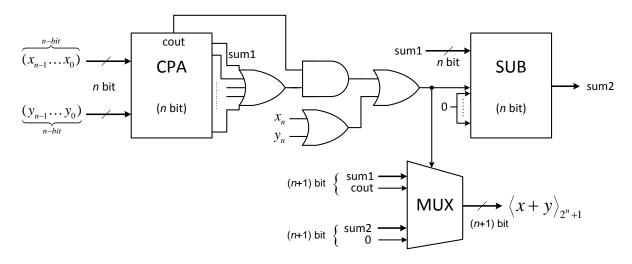

| <b>Fig. 2.3:</b> General structures of modular adders based on the moduli set $\{2^n - 1, 2^n, 2^n + 1\}$ [1], [26]                       |

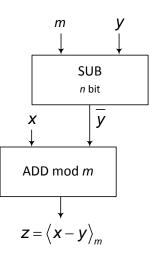

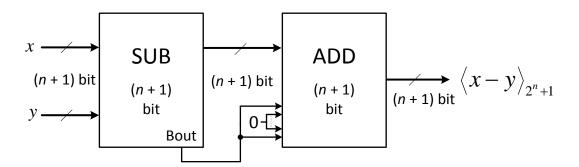

| Fig. 2.4: The structure of general modular subtractor [1], [2]                                                                            |

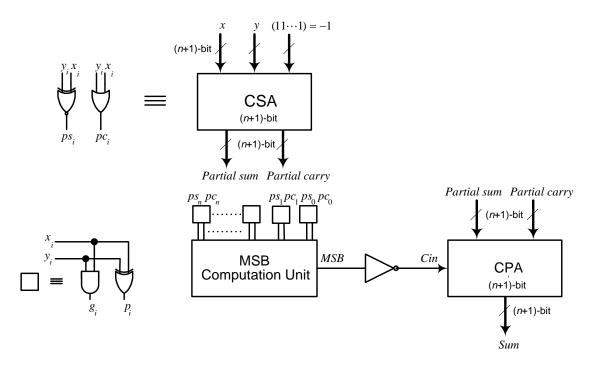

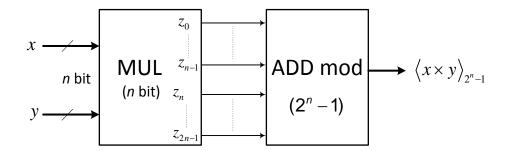

| <b>Fig. 2.5:</b> The structure of general modulo multiplier [1]                                                                           |

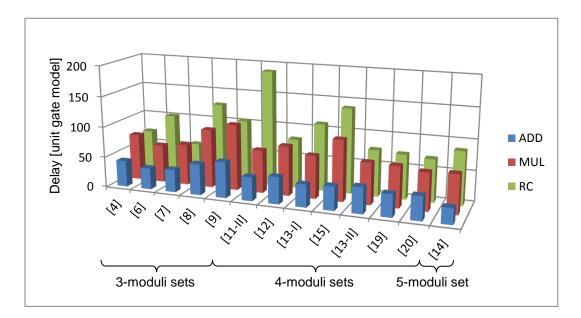

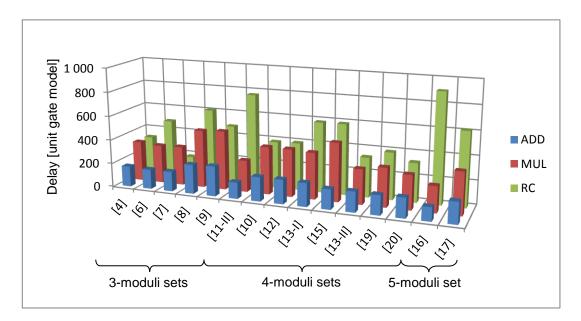

| Fig. 4.1: The delay of each basic component based on the moduli sets for DR = 12 bits (medium DR)                                         |

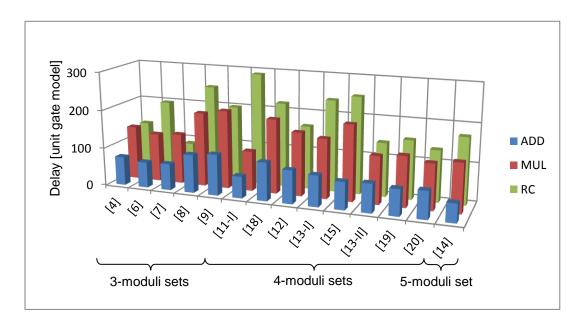

| Fig. 4.2: The delay of each basic component based on the moduli sets for DR = 24 bits (large DR)                                          |

| <b>Fig. 4.3:</b> The delay of each basic component based on the moduli sets for DR = 60 bits (very large DR)                              |

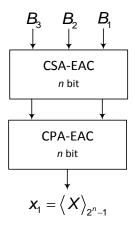

| <b>Fig. 4.4:</b> Modulo $(2^n - 1)$ channel of the binary to residue converter                                                            |

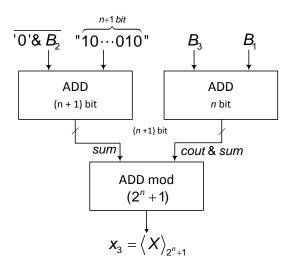

| <b>Fig. 4.5:</b> Proposed component for computing a residue with respect to modulo $(2^n + 1)$ channel of the binary to residue converter |

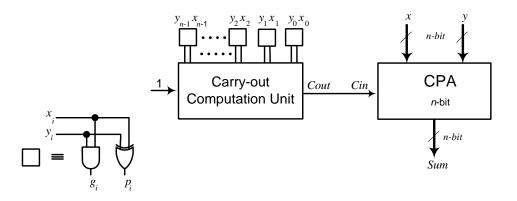

| <b>Fig. 4.6:</b> Proposed modulo $(2^n - 1)$ adder – based on prefix carry-out computation [78]46                                         |

| <b>Fig. 4.7:</b> Improved structure of the proposed modulo $(2^n + 1)$ adder – that uses <i>n</i> -bit components [79]                    |

| <b>Fig. 4.8:</b> Proposed modulo $(2^n + 1)$ adder - based on the prefix computation [78]49                                               |

| <b>Fig. 4.9:</b> Improved structure of proposed modulo $(2^n + 1)$ subtractor                                                             |

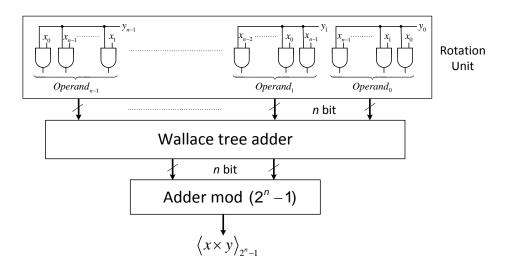

| <b>Fig. 4.10:</b> Proposed modulo $(2^n - 1)$ multiplier – based on multiplication-then-reduction approach                                |

| <b>Fig. 4.11:</b> Proposed modulo $(2^n - 1)$ multiplier – based on interleaving multiplication and reduction approach                    |

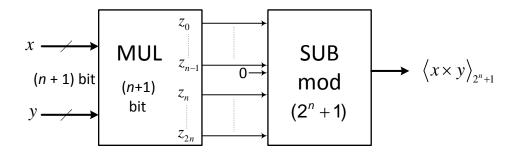

| <b>Fig. 4.12:</b> Proposed modulo $(2^n + 1)$ multiplier [80]                                                                             |

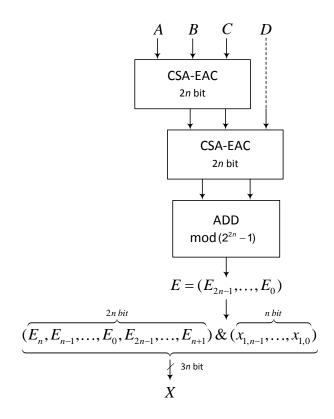

| Fig. 4.13: Proposed structure of reverse converter - based on the new CRT-I [83]56                                                        |

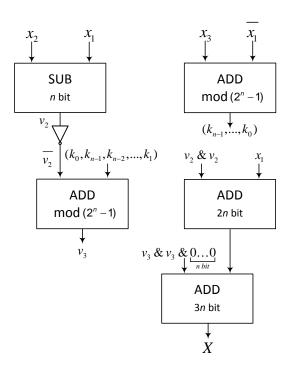

| Fig. 4.14: Proposed structure of reverse converter - based on the MRC [83]                                                                |

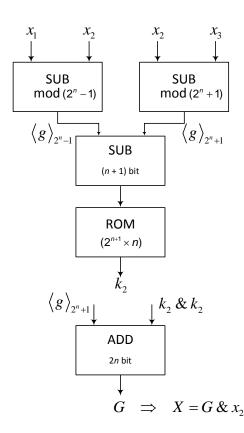

| Fig. 4.15: The structure of the reverse converter based on the proposed algorithm [86]63                              |

|-----------------------------------------------------------------------------------------------------------------------|

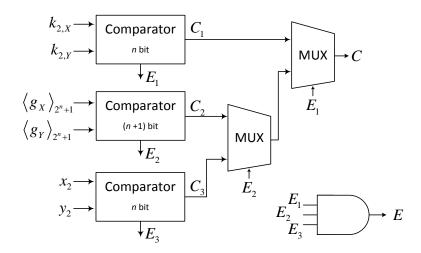

| Fig. 4.16: The structure of the residue comparator based on the proposed algorithm [86]66                             |

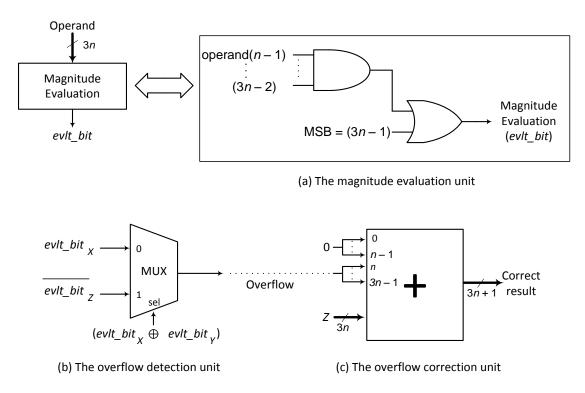

| Fig. 4.17: The internal structure of the proposed overflow detection & correction component for unsigned numbers [82] |

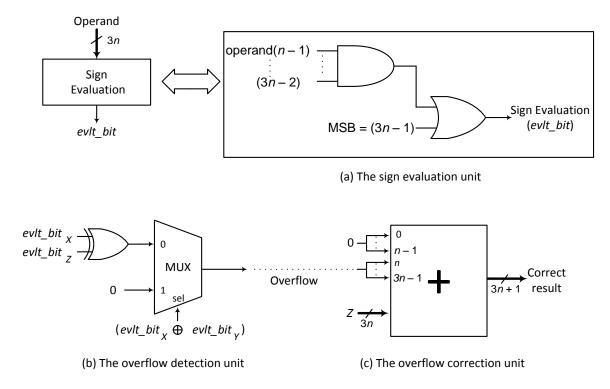

| Fig. 4.18: The internal structure of the sign and overflow detection & correction component for signed numbers [82]   |

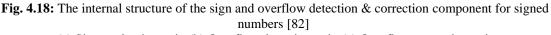

| Fig. 4.19: The structure of the proposed RNS-based image-processing application [84]75                                |

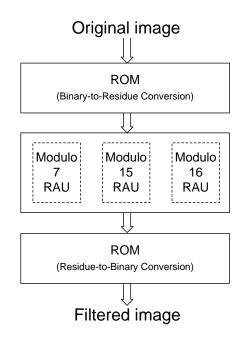

| Fig. 4.20: The Output images after applying edge detection and sharpening filters,                                    |

# List of Tables

| Tab. 2.1: The most recently published moduli sets    20                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Tab. 4.1:</b> The most efficient moduli sets regarding reverse converters for each dynamic range category                                    |

| <b>Tab. 4.2:</b> The most efficient moduli sets regarding RAUs for each dynamic range category 37                                               |

| Tab. 4.3:       Comparison between best moduli sets based on (D × C) [75] and timing performance [76]                                           |

| <b>Tab. 4.4:</b> Comparison between the proposed modulo $(2^n - 1)$ adder with its counterpart (f) in[26] in terms of critical path delay [ns]  |

| <b>Tab. 4.5:</b> Comparison between the proposed modulo $(2^n - 1)$ adder with its counterpart (f) in[26] in terms of area consumption [slices] |

| <b>Tab. 4.6:</b> Comparison between the proposed modulo $(2^n + 1)$ adder with its counterpart (k) in[26] in terms of critical path delay [ns]  |

| <b>Tab. 4.7:</b> Comparison between the proposed modulo $(2^n + 1)$ adder with its counterpart (k) in[26] in terms of area consumption [slices] |

| <b>Tab. 4.8:</b> Time and area improvements of multiplier's structure Fig. 4.11 over Fig. 4.1053                                                |

| <b>Tab. 4.9:</b> Comparison between the proposed multiplier and its counterpart in terms of critical path delay [ns]                            |

| Tab. 4.10: Comparison between the new CRT-I and MRC-based converters in terms of pad-<br>to-pad delay [ns]         59                           |

| Tab. 4.11: Comparison between the new CRT-I and MRC-based converters in terms of area         consumption [slices]         59                   |

| <b>Tab. 4.12:</b> The Groups within the dynamic range <i>M</i> of the moduli set $\{2^n - 1, 2^n, 2^n + 1\}$ 60                                 |

| <b>Tab. 4.13:</b> Comparison between reverse converters for different dynamic range requirements                                                |

| Tab. 4.14:         Comparison between proposed reverse converter and pure-ROM based one65                                                       |

| Tab. 4.15:       Comparison between different residue comparators for different dynamic range requirements                                      |

| Tab. 4.16: Performance comparison between the proposed designs and the analogous ones.73                                                        |

| <b>Tab. 4.17:</b> Comparison between binary and RNS-based image processing application that applies spatial filters on a gray-scale image                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Tab. 4.18:</b> A comparison between binary arithmetic unit and parallel RAUs (in terms of timing performance) based on moduli set $\{2^n - 1, 2^n + 1, 2^{2n} + 1\}$ [9], with DR = 4 <i>n</i> bit 83  |

| <b>Tab. 4.19:</b> Moduli sets that result in applications with worse timing performance than binary-<br>based ones                                                                                        |

| <b>Tab. 4.20:</b> The least numbers of iterated additions and multiplications required to achieve better timing performance of the RNS-based application that uses moduli set $\{2^n - 1, 2^n, 2^n + 1\}$ |

| <b>Tab. 4.21:</b> The least numbers of iterated additions and multiplications required to achieve better timing performance of the RNS based on Virtex-4 implementation                                   |

| <b>Tab. 4.22:</b> The maximum frequency of applications performing 10 iterated additions and 10 iterated multiplications using the RNS and BNS                                                            |

| <b>Tab. 4.23:</b> Power consumption at 100 MHz running application performing 10 iterated multiplications using the RNS and BNS                                                                           |

| <b>Tab. 4.24:</b> Hardware requirements for implementing applications performing 10 iteratedmultiplications using the RNS and BNS on Virtex-4 XC4VSX25 FPGA                                               |

| <b>Tab. 4.25:</b> The least numbers of iterated additions and multiplications required to achieve better timing performance of the RNS-based application that uses moduli set $\{2^n - 1, 2^n, 2^n + 1\}$ |

| Tab. 6.1: Delay and hardware complexity of different components using unit gate model100                                                                                                                  |

| <b>Tab. 6.2:</b> Comparison between reverse converters, modular adders and modular multipliersfor systems based on sets that provide $DR = 3n$ 101                                                        |

| <b>Tab. 6.3:</b> Comparison between reverse converters, modular adders and modular multipliersfor systems based on sets that provide $DR = 4n$ 101                                                        |

| <b>Tab. 6.4:</b> Comparison between reverse converters, modular adders and modular multipliersfor systems based on sets that provide $DR = 5n$                                                            |

| <b>Tab. 6.5:</b> Comparison between reverse converters, modular adders and modular multipliersfor systems based on sets that provide $DR = 6n$ 102                                                        |

| <b>Tab. 6.6:</b> The maximum frequency and power consumption of application performing a number of iterated additions using the RNS and BNS for DR = 12 bits (implemented on Virtex-4 XC4VSX25 FPGA)      |

### **1** Introduction

This thesis is concerned with an unconventional non-weighted number system that has gained a great scientific interest; the residue number system (RNS). Designing new and more efficient RNS based building blocks that improve digital signal processing (DSP) applications' performance is the main aim of this thesis.

Since the whole work will be devoted on the RNS, enclosing a brief introduction about this number system will be beneficial.

The RNS is a very old number system. It was found 1500 years ago by a Chinese scholar Sun Tzu. Since the last five decades, RNS's features have been rediscovered and thus the interest in this system has been renewed. The researchers have used the RNS in order to benefit from its features in designing high-speed and fault-tolerance applications.

The fundamental idea of the RNS is based on uniquely representing large binary numbers using a set of smaller residues, which results in carry-free, high-speed and parallel arithmetic [1].

This system is based on modulus operation, where the divider is called modulo and the remainder of the division operation is called residue. The basic notation in RNS is,

$$x_i = X \mod m_i = \left\langle x_i \right\rangle_{m_i} \quad ; \qquad 0 \le x_i < m_i \tag{1.1}$$

Each integer in RNS is represented by a set of residues corresponding to a specified moduli set. The main condition is that the moduli within the moduli set should be relatively prime,

$$X \xrightarrow{RNS} \left( \left\langle x_1 \right\rangle_{m_1}, \left\langle x_2 \right\rangle_{m_2}, \dots, \left\langle x_n \right\rangle_{m_n} \right) \quad ; \qquad GCD(m_i, m_j) = 1 \tag{1.2}$$

The RNS uniquely represents any integer X that locates in its dynamic range M, which is the product of the moduli within the moduli set.

$$M = \prod_{i=1}^{n} m_i \tag{1.3}$$

Both signed and unsigned integers can be represented in the RNS. For unsigned RNS, the range of the representable integers is,

$$0 \le X < M \tag{1.4}$$

For signed RNS, the range of representable integers is partitioned into two equal intervals,

| $0 \le X < \lfloor M / 2 \rfloor$ | for positive numbers | (1, 5) |

|-----------------------------------|----------------------|--------|

| $ M/2  \leq X < M$                | for negative numbers | (1.5)  |

In principle, any interval of M consecutive integers can be uniquely represented in the RNS. However, the standard conventions on representable integer ranges in the RNS are illustrated in equations (1.4) and (1.5).

The principal aspect that distinguishes the RNS from other number systems is that the standard arithmetic operations; addition, subtraction and multiplication are easily implemented, whereas operations such as division, root, comparison, scaling and overflow and sign detection are more complicated. Therefore, the RNS is extremely useful in applications that require a large number of addition and multiplication, and a minimum number of comparisons, divisions and scaling. In other words, the RNS is preferable in applications in which additions and multiplications are critical. Such applications are DSP, image processing, speech processing, cryptography and transforms [2].

The main RNS advantage is the absence of carry propagation between digits, which results in high-speed arithmetic needed in embedded processors. Another important feature of RNS is the digits independence, so an error in a digit does not propagate to other digits, which results in no error propagation, hence providing fault-tolerance systems. In addition, the RNS can be very efficient in complex-number arithmetic, because it simplifies and reduces the number of multiplications needed. All these features increase the scientific tendency toward the RNS especially for DSP applications. However, the RNS is still not popular in general-purpose processors, due the aforementioned difficulties.

Fig. 1.1: The architecture of the residue number system (RNS)

The basic RNS processor's architecture is shown in Fig. 1.1. It consists of three main components; a forward converter (binary to residue converter), that converts the binary number to n equivalent RNS residues, corresponding to the n moduli. The n residues are then processed using n parallel residue arithmetic units (RAUs); each of them corresponds to one

modulo. The *n* outputs of these units represented in RNS are then converted back into their binary equivalent, by utilizing the reverse converter (residue to binary converter).

The structure of this desecration is organized as follows; Chapter 2 presents a brief survey about the most recently achievements in the RNS, concerning different proposed moduli sets that provide different dynamic ranges, the common means and structures to perform forward and reverse conversion, general structures of residue arithmetic units and applications where using the RNS is advantageous. Then, the main aims and purposes of this dissertation are stated in Chapter 3. Chapter 4 is dedicated to present the dissertation results including the proposed RNS components, proposed RNS-based applications, comparisons between RNS and binary-based applications, and the cases when RNS should be used. Moreover, some widely accepted concepts are proven wrong. Finally, the conclusions, outcomes and the final remarks of this dissertation are illustrated in Chapter 5.

### 2 State of the art

This chapter presents a summary of the fundamental principles of the RNS; RNS's components, their basics and the most commonly used designs. The most recent work and researches are also presented in this chapter. Each component in the RNS will be separately discussed, in order to provide a brief overview and state the recent achievements in its field.

The interest in RNS arithmetic has started since 1950's [1], [2]. The first hardware based on the RNS was built in 1967. The work in this field continued and many improvements in all areas of the RNS have arisen, in order to enhance its features, resolve its related problems and find suitable applications that benefit from RNS's features. Most of the early designs of RNS were based on read-only memories (ROM). However, the great advance in VLSI (very large scale integration) technology paved the way for new approaches in designing RNS systems.

New trends to design non-ROM based RNS have appeared. Subsequently, much work has been devoted for special moduli sets. Excellent results in terms of computational speed have been achieved in 2000 [2].

The most important issues that must be taking into account when designing an RNS system are, a proper moduli set selection, forward conversion, residue arithmetic units and reverse conversion. A brief of each of these issues and its recent achievements are separately discussed in the following sections.

#### 2.1 Moduli set selection

Choosing a proper modulo set is an essential issue for building an efficient RNS with a sufficient dynamic range (DR). The number, form and value of the moduli affect the dynamic range, timing performance and hardware complexity of an RNS-based application [3].

The moduli set in the RNS can be either arbitrary or special. In principal, special moduli sets were suggested in order to simplify the implementation of arithmetic operations. This invariably means that arithmetic on residue digits should not deviate too far from conventional arithmetic, which is just arithmetic modulo a power of two [1]. On the other hand, arithmetic circuits based on arbitrary moduli sets are much more complex and time consuming. These sets are utilized in cases when using special moduli sets imposes some constraints.

The most famous moduli set is  $\{2^n - 1, 2^n, 2^n + 1\}$  [4]. This set has been known as a means of simplifying the calculations necessary to implement the reverse converter (RC). However, this set has modulo  $(2^n + 1)$  channel that represents the bottleneck of the system. Its arithmetic circuits suffer from the longest delay among all three channels.

In general, arithmetic circuits modulo  $(2^{k} - 1)$  are more efficient than those modulo  $(2^{k} + 1)$ , therefore, it is better to reduce the number of moduli of the form  $(2^{k} + 1)$  [5]. Thus, in order to simplify the complexity caused by modulo  $(2^{n} + 1)$  in the set  $\{2^{n} - 1, 2^{n}, 2^{n} + 1\}$  [4], new moduli sets  $\{2^{n-1} - 1, 2^{n} - 1, 2^{n}\}$  [6] and  $\{2^{n} - 1, 2^{n}, 2^{n+1} - 1\}$  [7], that substitute this modulo with another of the form  $(2^{k} - 1)$ , have been suggested. These three sets have a 3*n*-bit DR, which is sufficient for applications that require medium DRs (less than 22 bits).

However, many DSP applications require larger DRs, therefore, new moduli sets  $\{2^n - 1, 2^n, 2^{2n+1} - 1\}$  [8] and  $\{2^n - 1, 2^n + 1, 2^{2n} + 1\}$  [9] that provide 4n-bit DR and  $\{2^n, 2^{2n} - 1, 2^{2n} + 1\}$  [10] that provides 5n-bit DR, have been suggested. Although the DR is larger, the delay of the RAUs based on these sets has considerably increased, due to utilizing moduli with greater magnitudes. In order to eliminate this drawback and maintain the large DR, sets of four and five moduli have been suggested, such as  $\{2^n - 1, 2^n, 2^n + 1, 2^{n+1} - 1\}$  [11]-I,  $\{2^n - 1, 2^n, 2^n + 1, 2^{n+1} + 1\}$  [11]-II,  $\{2^n - 1, 2^n, 2^n + 1, 2^{2n} + 1\}$  [12],  $\{2^n - 1, 2^n, 2^n + 1, 2^{2n+1} - 1\}$  [13]-I,  $\{2^n - 1, 2^n, 2^n + 1, 2^{2n} - 2, 2^{2n+1} - 3\}$  [15],  $\{2^n - 1, 2^n, 2^n + 1, 2^{2n} - 2^{2n+1} - 1\}$  [13]-II,  $\{2^n - 1, 2^n, 2^n + 1, 2^{2n-1} - 1, 2^{2n}, 2^n + 1, 2^{2n-1} - 1\}$  [13]-II,  $\{2^n - 1, 2^n, 2^n + 1, 2^{2n-1} - 1, 2^{2n}, 2^{2n+1} - 1\}$  [16],  $\{2^n, 2^{n/2} - 1, 2^{n/2} + 1, 2^n + 1, 2^{2n-1} - 1\}$  [17],  $\{2^{n/2} - 1, 2^{n/2} + 1, 2^n + 1, 2^{2n+1} - 1\}$  [18],  $\{2^n + 1, 2^n - 1, 2^{2n}, 2^{2n+1} - 1\}$  [19] and  $\{2^{2n+1}, 2^{2n} + 1, 2^n + 1, 2^n - 1\}$  [20]. Each of these sets has its own advantages and disadvantages. Some of them offer higher DRs than others, while others have more parallelism. Some of them concentrated on designing efficient RCs, while others on efficient RAUs.

Tab. 2.1 illustrates the most recently published moduli sets, including the dynamic ranges they provide and possible n values that can be used in these sets.

| Number of moduli            | Modulo set                                            | Dynamic range  | <i>n</i> odd/even |

|-----------------------------|-------------------------------------------------------|----------------|-------------------|

|                             | $\{2^{n}-1, 2^{n}, 2^{n}+1\}$ [4]                     | 3n             | any               |

|                             | $\{2^{n-1}-1, 2^n-1, 2^n\}$ [6]                       | 3 <i>n</i> – 1 | any               |

| <b>T</b> hurston 1 19 and 1 | $\{2^{n}-1, 2^{n}, 2^{n+1}-1\}$ [7]                   | 3 <i>n</i> + 1 | any               |

| Three moduli sets           | $\{2^n - 1, 2^n, 2^{2n+1} - 1\}$ [8]                  | 4 <i>n</i> + 1 | any               |

|                             | $\{2^{n} - 1, 2^{n} + 1, 2^{2n} + 1\}$ [9]            | 4 <i>n</i>     | any               |

|                             | $\{2^{n}, 2^{2n} - 1, 2^{2n} + 1\}$ [10]              | 5 <i>n</i>     | even              |

| Four moduli sets            | $\{2^{n} - 1, 2^{n}, 2^{n} + 1, 2^{n+1} - 1\}$ [11]-l | 4 <i>n</i> + 1 | even              |

Tab. 2.1: The most recently published moduli sets

|                     | $\{2^{n} - 1, 2^{n}, 2^{n} + 1, 2^{n+1} + 1\}$ [11]-II                                        | 4 <i>n</i> + 1 | odd  |

|---------------------|-----------------------------------------------------------------------------------------------|----------------|------|

|                     | $\{2^{n/2} - 1, 2^{n/2} + 1, 2^n + 1, 2^{2n+1} - 1\}$ [18]                                    | 4 <i>n</i> + 1 | even |

|                     | $\{2^{n}-1, 2^{n}, 2^{n}+1, 2^{2n}+1\}$ [12]                                                  | 5 <i>n</i>     | any  |

|                     | $\{2^{n} - 1, 2^{n}, 2^{n} + 1, 2^{2n+1} - 1\}$ [13]-l                                        | 5 <i>n</i> + 1 | any  |

|                     | $\{2^{n} - 1, 2^{2n}, 2^{n} + 1, 2^{2n} + 1\}$ [13]-II                                        | 6 <i>n</i>     | any  |

|                     | $\{2^{n} - 1, 2^{n} + 1, 2^{2n} - 2, 2^{2n+1} - 3\}$ [15]                                     | 6 <i>n</i> + 1 | any  |

|                     | $\{2^{n} + 1, 2^{n} - 1, 2^{2n}, 2^{2n+1} - 1\}$ [19]                                         | 6 <i>n</i> + 1 | any  |

|                     | $\{2^{2^{n+1}}, 2^{2^n} + 1, 2^n + 1, 2^n - 1\}$ [20]                                         | 6 <i>n</i> + 1 | any  |

|                     | $\{2^{n}, 2^{n/2} - 1, 2^{n/2} + 1, 2^{n} + 1, 2^{2n-1} - 1\}$ [17]                           | 5 <i>n</i> – 1 | even |

| Five moduli<br>sets | { $2^{n} - 1, 2^{n}, 2^{n} + 1, 2^{n} - 2^{(n+1)/2} + 1,$<br>$2^{n} + 2^{(n+1)/2} + 1$ } [14] | 5 <i>n</i>     | odd  |

|                     | $\{2^{n} - 1, 2^{n}, 2^{n} + 1, 2^{n-1} - 1, 2^{n+1} + 1\}$ [16]                              | 5 <i>n</i>     | even |

#### 2.2 RNS Converters

Every RNS system involves forward and reverse converters that convert weighted numbers into their equivalent RNS representation and vice versa, respectively.

The structures of these converters can be memory-based, conventional-based or mix of both. The choice is actually determined by the dynamic range required for the application being designed. For applications with small dynamic ranges, such as digital image processing where the range of pixel values is [0,255], the memory-based converters are the most efficient. Contrary, for applications with large dynamic ranges (greater than 22 bits), such as cryptography and some FIR filters, the combinational structure of the converters is preferred. The next two sections illustrate the converters based on the combinational structure.

#### 2.2.1 Binary to residue converters

The structure of the binary to residue converter (forward converter) is rather simple. Hence, little work was devoted to this component [21].

In order to illustrate the forward conversion process, forward conversion equations corresponding to the special moduli set  $\{2^n - 1, 2^n, 2^n + 1\}$  will be stated [1], [2]. Actually, by modifying *k*, these equations can be applied with any modulo of the form  $(2^k \pm 1)$  within the sets presented in Tab. 2.1.

Assuming *X* is a 3*n*-bit integer. *X* can be written as follows,

$$X = (b_{3n-1} \ b_{3n-2} \dots b_n \ b_{n-1} \dots b_0)_2 = B_1 2^{2n} + B_2 2^n + B_3$$

(2.1)

where,  $b_{3n-1} \dots b_0$  are the binary digits (bits) of *X*.  $B_1$ ,  $B_2$ ,  $B_3$  are blocks, each of them contains *n* bits.

**Fig. 2.1:** RNS forward converter for the moduli set  $\{2^n - 1, 2^n, 2^n + 1\}$  [1]

The RNS representation of *X* according to the moduli set  $\{2^n - 1, 2^n, 2^n + 1\}$ ,

$$\langle x_1 \rangle_{2^n - 1} = \langle X \rangle_{2^n - 1} = \langle B_1 2^{2n} + B_2 2^n + B_3 \rangle_{2^n - 1} = \langle B_1 + B_2 + B_3 \rangle_{2^n - 1}$$

(2.2)

$$\langle x_2 \rangle_{2^n} = \langle X \rangle_{2^n} = \langle B_1 2^{2^n} + B_2 2^n + B_3 \rangle_{2^n} = \langle B_3 \rangle_{2^n}$$

(2.3)

$$\langle x_3 \rangle_{2^{n+1}} = \langle X \rangle_{2^{n+1}} = \langle B_1 2^{2n} + B_2 2^n + B_3 \rangle_{2^{n+1}} = \langle B_1 - B_2 + B_3 \rangle_{2^{n+1}}$$

(2.4)

Equations (2.2), (2.3) and (2.4) are extracted based on the following,

$$\left\langle 2^{n} \right\rangle_{2^{n}-1} = \left\langle 2^{n} - 1 + 1 \right\rangle_{2^{n}-1} = \left\langle 1 \right\rangle_{2^{n}-1}$$

$$\left\langle 2^{n} \right\rangle_{2^{n}} = \left\langle 0 \right\rangle_{2^{n}}$$

$$\left\langle 2^{n} \right\rangle_{2^{n}+1} = \left\langle 2^{n} - 1 + 1 \right\rangle_{2^{n}-1} = \left\langle -1 \right\rangle_{2^{n}+1}$$

$$(2.5)$$

According to equations (2.2), (2.3) and (2.4), the general structure of the forward converter for the moduli set  $\{2^n - 1, 2^n, 2^n + 1\}$  is shown in Fig. 2.1 [1],

#### 2.2.2 Residue to binary converters

Unlike forward converters, residue to binary converters (reverse converters) gained much more interest due to their complexity. This component is considered the most time consuming component in the whole RNS system. It is also used for performing difficult RNS operations (division, scaling, comparison, overflow and sign detection). Researchers continuously try to reduce the delay of the reverse converters, due to the reason that having a slow reverse converter may counteract the speed gain of the residue arithmetic unit, hence, ruining the whole advantages of using the RNS.

Reverse conversion algorithms are based on the Chinese remainder theorem (CRT), mixed-radix conversion (MRC) and new Chinese remainder theorems (new CRTs). Every algorithm has its own advantages and disadvantages. The decision to use any of them is based on the used moduli set, the application being designed and the design's requirements (time, area, power). All reverse conversion methods depend on computing multiplicative inverses. The multiplicative inverses  $x^{-1}$  of residue *x* relative to modulo *m* is defined as follows,

$$\langle x \times x^{-1} \rangle_m = 1$$

;  $0 \le x, x^{-1} < m$  (2.6)

It is clear that finding  $x^{-1}$  is not a simple task. However, using special moduli sets can make the computation of multiplicative inverses easier.

According to the CRT, a weighted number X can be calculated from its residues  $(x_1, x_2, ..., x_n)$  by the following equation [1], [2],

$$X = \left\langle \sum_{i=1}^{n} \left\langle x_{i} N_{i} \right\rangle_{m_{i}} M_{i} \right\rangle_{M}$$

(2.7)

where,  $M = m_1 \times m_2 \times \cdots \times m_n$ ,  $M_i = M / m_i$  and  $N_i = \langle M_i^{-1} \rangle_{m_i}$  is the multiplicative inverse of  $M_i$  relative to modulo  $m_i$ .

The CRT-based converter can be implemented in parallel. However, it needs a large modular adder, which can be very difficult for hardware implementation. Reverse converters based on the CRT were proposed in [4], [6], [7], [10] and [14].

By using the MRC, a residue number  $(x_1, x_2, ..., x_n)$  can be converted back into its weighted equivalent X by,

$$X = v_n \prod_{i=1}^{n-1} m_i + \dots + v_3 m_2 m_1 + v_2 m_1 + v_1$$

(2.8)

where,

$$v_1 = x_1 \tag{2.9}$$

$$v_2 = \left\langle (x_2 - v_1) \times \left\langle m_1^{-1} \right\rangle_{m_2} \right\rangle_{m_2}$$

(2.10)

$$v_{3} = \left\langle ((x_{3} - v_{1}) \times \left\langle m_{1}^{-1} \right\rangle_{m_{3}} - v_{2}) \times \left\langle m_{2}^{-1} \right\rangle_{m_{3}} \right\rangle_{m_{3}}$$

(2.11)

As illustrated in equation (2.8), the MRC does not need any special modular adder. However, it is a sequential algorithm, which makes it not suitable for systems with more than four moduli within the set [7], [8]. To overcome such a case (more than four moduli), a twolevel structure consisting of the MRC and one of the CRTs is proposed in [11], [16], [17].

The new CRT-I is a modification of the original CRT, where the size of the final modular adder is reduced by one modulo. Using this algorithm, a residue number  $(x_1, x_2, ..., x_n)$  can be converted back into its weighted equivalent *X* by,

$$X = x_1 + m_1 \times \left\langle k_1(x_2 - x_1) + k_2 m_2(x_3 - x_2) + \dots + k_{n-1} m_2 m_3 \cdots m_{n-1}(x_n - x_{n-1}) \right\rangle_{m_2 m_3 \cdots m_n}$$

(2.12)

where,

$$\langle k_1 \times m_1 \rangle_{m_2 m_3 \cdots m_n} = 1$$

(2.13)

$$\langle k_2 \times m_1 \times m_2 \rangle_{m_3 \cdots m_n} = 1$$

(2.14)

$$\left\langle k_{n-1} \times m_1 \times m_2 \times \cdots \times m_{n-1} \right\rangle_{m_n} = 1$$

(2.15)

As can be noticed in equation (2.12), the final modular adder is reduced by one modulo. This can bring a great benefit when the first modulo is of the  $2^k$  form, and the multiplication of the rest moduli is of the  $(2^k - 1)$  form. Such reverse converters are reported in [9], [12].

The new CRT-II even further reduces the size of the final modular adder. A residue number  $(x_1, x_2, ..., x_n)$  can be converted back into its weighted equivalent *X* by the new CRT-II by,

$$X = Z + m_1 m_2 \langle k_1 (Y - Z) \rangle_{m_3 m_4}$$

$$Z = x_1 + m_1 \langle k_2 (x_2 - x_1) \rangle_{m_2}$$

$$Y = x_3 + m_3 \langle k_3 (x_4 - x_3) \rangle_{m_4}$$

(2.16)

where,  $\langle k_1 m_1 m_2 \rangle_{m_3 m_4} = 1$ ,  $\langle k_2 m_1 \rangle_{m_2} = 1$ ,  $\langle k_3 m_3 \rangle_{m_4} = 1$

This algorithm is very efficient. It is used with sets that have four or more moduli. Reverse converters based on the new CRT-II are presented in [13], [15].

#### 2.3 Residue Arithmetic Units

The RNS contains a number of residue arithmetic units corresponding to the number of moduli. These RAUs are totally independent and perform arithmetic operations in parallel.

As aforementioned before, addition, subtraction and multiplication are easy operations in the RNS (RNS-friendly operations). On the other hand, division, scaling, comparison, overflow and sign detection are complex and preferred to be avoided as much as possible.

The RNS friendly operations are carried out by individually performing that operation on each residue corresponding to the moduli. Thus, no carry is propagated from one residue to another. This leads to parallel arithmetic operations, reduced carry propagation length in adders and smaller sizes of multipliers, hence, providing considerably reduced-delay and area applications.

$$X = (x_1, x_2, \dots, x_n) \quad , \quad Y = (y_1, y_2, \dots, y_n)$$

$$Z = X \circ Y = \left( \left\langle x_1 \circ y_1 \right\rangle_{m_1}, \left\langle x_2 \circ y_2 \right\rangle_{m_2}, \dots, \left\langle x_n \circ y_n \right\rangle_{m_n} \right) \quad ; \quad \circ = (+, -, \times)$$

$$Z = (z_1, z_2, \dots, z_n)$$

$$(2.17)$$

The structure of the RAU is based on one of the following three methods; a pure memory structure, a combinational structure or a mix of both [1], [2], [22]. The first approach is realized by using ROMs [23]. The main drawback of this approach is the exponential growth of the memory size for large moduli. Therefore, this approach is suitable only for small moduli. The second approach depends on pure combinational structure. This approach is suitable for large moduli [24]. A RAU based on the third approach, that uses both memory and combinational circuits, is presented in [25].

#### 2.3.1 Modular addition

Modular addition is a fundamental operation in the RNS. It is used in almost every part of the RNS (forward converter, reverse converter, modular multipliers, modular subtractors and modular adders themselves). Therefore, designing efficient modular adders has gained a wide interest. The primary equation for performing general modular addition, which was hardwarerealized in [22], is defined by,

$$\left\langle x+y\right\rangle_{m} = \begin{cases} x+y & ; \quad if \ 0 \le x+y < m \\ x+y-m & ; \quad if \ x+y \ge m \end{cases}$$

(2.18)

Assuming that the width of modulo m is n bits, the structure of the general modular adder is shown in Fig. 2.2 [22]. It consists of two n-bit adders, an OR gate and a multiplexer.

Fig. 2.2: The structure of general modulo adder [22]

As stated above, using special moduli sets can considerably simplify the realization of arithmetic circuits. Regarding the most famous moduli set  $\{2^n - 1, 2^n, 2^n + 1\}$ , three modular adders are specially designed corresponding to each modulo.

A modulo  $(2^n)$  adder can be simply realized using an *n*-bit binary adder, with ignored carry-out. A modulo  $(2^n - 1)$  adder, can also be simply realized using an *n*-bit binary adder with EAC (end around carry) [26].

However, modulo  $(2^n + 1)$  adder is considered to be more complex, due to the (n + 1)-bit operands and results. It represents the bottleneck of the system. Its arithmetic circuits suffer from the longest delay among all three channels. Therefore, many researchers have focused on this type of modular adders. Diminished-one number system has been used in [27], [28]. In this number system, (n + 1)-bit operands are represented using just *n* bits, which results in speeding-up the execution time. However, this speed-up is at the cost of more area consumption occupied by converters to/from the diminished-one representation and special treatment required for operands equal to zero [29]. A quite interest publication [26] has illustrated different structures of modular adders for both general and special moduli sets. In this publication, both standard binary and diminished-one representation for modulo  $(2^n + 1)$  adders have been used.

Much investigation and research was devoted in order to improve timing performance of modular adders. One of the suggested means is by utilizing faster binary adders, such as parallel prefix adders [28], [29] and [30].

In principal, the general structures of modular adders based on the moduli set  $\{2^n - 1, 2^n, 2^n + 1\}$  are illustrated in Fig. 2.3 [1], [26]. These structures have been utilized during the study on different moduli sets, which is presented in Section 4.1.

Fig. 2.3: General structures of modular adders based on the moduli set  $\{2^n - 1, 2^n, 2^n + 1\}$  [1], [26]

#### 2.3.2 Modular subtraction

RNS subtraction is an operation greatly used in many fields of DSP, such as, the mean error estimation, mean square error estimation and calculation of sum of absolute differences [1], [2]. Since modulo arithmetic is also frequently used in these types of applications, efficient modulo subtraction circuits are welcome. However, modular subtraction can be considered as a special case of modular addition, where an additive inverse is used. It is defined as follows,

$$\left\langle \overline{y} \right\rangle_{m} = \left\langle -y \right\rangle_{m} = \left\langle m - y \right\rangle_{m} \implies \left\langle x - y \right\rangle_{m} = \left\langle x + \overline{y} \right\rangle_{m}$$

(2.19)

Assuming the width of modulo m is n bits and according to equation (2.19), a general modulo subtractor can be designed using an n-bit subtractor followed by a general modulo m adder. The structure of this subtractor is illustrated in Fig. 2.4 [1], [2].

Very little work was dedicated for studying and designing modular subtractors. According to Property 1, a modulo  $(2^n - 1)$  subtractor can be simply realized using modulo  $(2^n - 1)$  adder and a few inverters.

Property 1: The residue of a negative residue number (-x) in modulo  $(2^n - 1)$  is the one's complement of *x*, where  $0 \le x < 2^n - 1$ .

Therefore, most studies were dedicated for designing efficient modulo  $(2^n + 1)$  subtractors, such as [31], [32]. The authors of [31] presented novel architectures of modulo  $(2^n + 1)$  subtractors, which are efficient in terms of delay and area using both normal and diminished-one number representation. Moreover, zero handling was also taken into account and a special unit that treats the operands equal to zero was designed.

Fig. 2.4: The structure of general modular subtractor [1], [2]

#### 2.3.3 Modular multiplication

Modular multiplication is a very important operation in the RNS. It is used in many applications such as FIR (finite impulse response) filters, Fourier transforms and digital image processing [1], [2]. The speed gain of modular multipliers is indeed the most attractive aspect for using RNS-based DSP applications.

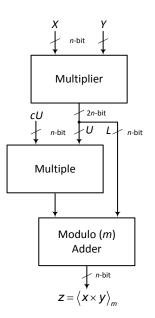

There are two general methods for performing modular multiplication [33]; the first method depends on multiplication then reduction with regard to modulo. This method requires a large space to store the product of the multiplication in order to perform the reduction process thereafter [33]. The basic structure of the modular multiplier based on this method consists of a binary multiplier followed by a reduction unit. This reduction unit can be further simplified in case of using the special moduli sets. This approach has been utilized in [34], [35]. An example of this method is shown in Fig. 2.5. The structure of this multiplier is based on the product-partitioning approach presented in [1].

Fig. 2.5: The structure of general modulo multiplier [1]

The second approach is based on interleaving multiplication and reduction. Many publications used this approach. A modular multiplier based on the Montgomery reduction algorithm was presented in [36]. In this structure, the reduction is performed at each iteration step of the multiplication process. Montgomery reduction algorithm is efficient for very large dynamic ranges; where the width of modulo is several hundred bits. Another efficient hardware implementation method for multiplying integers – Wallace tree – was used in RNS multipliers for both moduli  $(2^n - 1, 2^n + 1)$  [37], [38]. Two RNS multipliers for moduli  $(2^n - 1, 2^n + 1)$  based on modified Booth were published in [39], [40]. According to the authors, these modular multipliers offer fast and completely regular structures, because the modified Booth algorithm. An RNS multiplier that depends only on binary adders has been published in [41]. This multiplier is an improved design of [42], whose architecture is almost exclusively composed of full and half adders.

# 2.3.4 Complex operations in the RNS (overflow detection, sign detection and residue comparison)

As aforementioned before operations as division, overflow detection, sign detection and magnitude comparison are problematic and very complex in the RNS. In some cases, some of these operations are essential and cannot be avoided. Hence, a number of methods for solving these problems have been suggested. A survey of the methods for overflow detection, sign detection and magnitude comparison is briefly presented below.

In principle, the general way to detect overflow in the RNS is via comparing the result of addition with one of the addends. Suppose two integers x, y. These two integers are being added modulo m. If  $x \ge 0$  and y < m [1], [2],

$$Overflow = \begin{cases} 1 & ; & if \langle x + y \rangle_m < x \\ 0 & ; & otherwise \end{cases}$$

(2.20)

One of the fastest and most efficient ways to detect overflow in the RNS is via parity checking [2], [43], [44]. It indicates whether an integer is even or odd. However, this technique can only be used with odd dynamic ranges. Suppose two integers x and y have the same parity,

$$Overflow = \begin{cases} 1 & ; & if \langle x + y \rangle_m \text{ is odd} \\ 0 & ; & otherwise \end{cases}$$

(2.21)

Contrary, if *x* and *y* have different parity,

$$Overflow = \begin{cases} 1 & ; & if \langle x + y \rangle_m \text{ is even} \\ 0 & ; & otherwise \end{cases}$$

(2.22)

The parity checking technique is one of the best and fastest proposed methods to detect overflow in the RNS. It depends on look-up tables (LUTs) or on an extra modulo (a redundant modulo). However, this technique can only be used with moduli sets that have just odd members, i.e. odd dynamic range, which is not suitable for many moduli sets that uses  $2^n$  as one of its moduli, especially the most famous moduli set  $\{2^n - 1, 2^n, 2^n + 1\}$ . RNSs with even dynamic ranges have more attractive features than those with odd ones. Due to the reason, that using  $2^n$  modulo greatly simplifies and reduces the delay and complexity of the residue arithmetic operations and the residue-to-binary conversion. Thus, overflow detection in the RNS with even dynamic range is a very important issue.

On the other hand, according to equation (1.5) for signed RNS, the general way for sign detection in the RNS is via comparing the numbers, after reverse converting them back to the weighted form, with half of the dynamic range [1], [2].

Concerning magnitude comparison in the RNS, many comparators based on residue to binary converters were proposed. In principal, the straightforward way to compare two residue numbers in the RNS is to reverse convert them into weighted representation and then carry out a conventional comparison [1]. However, this method is costly; therefore, many approaches were suggested in order to perform comparison on the residue numbers [45], [48].

One of the first suggested approaches is based on a diagonal function that is defined as the sum of suitable quotients of the number named as SUM of Quotients Technique (SQT) [45]. This approach uses an extra modulo that is inserted in the used set of moduli. Another residue comparator, based on the new CRT-II, was suggested in [46]. Contrary to the previous comparator, this one does not use any extra modulo and provides smaller modulo operation. One of the simplest ways to perform residue comparison is based on the new CRT-I [4]. This approach utilizes two parallel binary comparators of 2n bits and n bits. A residue comparison algorithm based on the CRT for general moduli sets was suggested in [47]. In this paper, an efficient ROM-free residue comparator for  $\{2^n - 1, 2^n, 2^n + 1\}$  was also presented. According to the authors, this comparator is faster and reduces the hardware close to the half of the one based on the new CRT-I [4]. In [48], [49], efficient methods based on the parity checking technique were proposed. However, these methods can only be used with odd moduli sets. Thus, they cannot be used in an RNS based on  $\{2^n - 1, 2^n, 2^n + 1\}$ .

#### 2.4 RNS Applications

Due to the carry-free, residue independence and parallelism features of the RNS, it has been intensively used in many fields, such as digital signal processing, digital filtering, digital communications, cryptography, error detection and correction [1], [2]. Moreover, new trends to use the RNS in low-power design have also arisen. In principal, this system is of great benefit in areas where addition, subtraction and multiplication are dominant and division, comparison, overflow and sign detection are minor. Hence, the RNS has become a tough candidate for high-performance, fault tolerant and secure DSP applications.

One of the main fields for RNS-based applications is finite impulse response (FIR) filters [50]-[55]. In [50], the authors explore the design workspace of FIR filters with respect to structure, characteristics and number of taps. According to the authors, the proposed RNS-based filter operates at the same throughput as binary filters and has smaller area and power consumption, when the number of taps is larger than 16. In [51], a FIR filer was implemented using the RNS based on any number of moduli of the form  $\{2^n - 1, 2^n, 2^n + 1\}$ . As reported in this paper, the proposed filter provides a significant overall area-delay product gain ranged from 35% to 60% for a 16-tap filter with dynamic range from 20 to 40 bits. A very interesting and detailed FIR filter performance analysis between RNS and binary is presented in [52]. According to this study, the RNS-based FIR filter is more than 3 times faster and consumes only about 60% of the area of binary-based FIR, when the number of taps is larger than 32.

Furthermore, a number of attempts to design RNS-based infinite impulse response (IIR) filters have been also arisen [56], [57]. However, the results were not impressive as in FIR filters.

Trends to use the RNS for reducing power consumption have also appeared [50], [53]-[55]. In principal, the power dissipation is reduced due to the parallelism feature in the RNS. Since the filtering process is divided into a number of smaller word-length filters that operate in parallel, hence, these smaller computation units require lower supply voltage for specific frequency. One of the most efficient low-power RNS-based FIR filters is presented in [54]. This filter showed static power dissipation reduction of 50% and total power reduction of 40% compared to the binary filters. However, the dynamic range in this filter was limited to 20 bits only and the reduced power consumption was achieved for more than 15 taps.

Digital image processing is another field for benefiting of the RNS's features. Many researches were dedicated for exploiting the RNS features for enhancing digital image processing applications [58]-[62]. One of the first papers that suggested using the RNS in image processing are [58], [59]. However, the main concentration of these papers was on the security aspect rather than benefiting from the parallelism feature of the RNS. An RNS based application for filtering digital images was presented in [60]. The filtering is done in both spatial and frequency domains. Since pixel values have the range [0, 255], the authors suggested using the moduli set {5, 7, 8} as it provides a dynamic range [0, 279], which they considered to be enough for image filtering applications. However, during my study, I have found out that this is not true. An example that clarifies this confusion is presented in Section 4.7.2. In [61], [62], similar structures for edge detection and spatial filtering were also introduced.

In addition, error detection and correction applications greatly benefit from the RNS's features [63], [64]. Due to the carry-free and the lack of weighted significance of residue digits properties, an error in a digit does not propagate, hence, does not affect other digits. One of the suggested methods for detecting and correcting errors is via the redundant RNS (RRNs) [63]. This system uses redundant moduli, thus, errors can be precisely detected and corrected. In this system, the dynamic range is divided into two intervals; the legitimate range and illegitimate range. A single-digit error is detected if the binary result after reverse conversion belongs to the illegitimate range. In order to detect a single-digit error, a single redundant modulo is sufficient. On the other hand, in order to detect and correct a single-digit error detection and correction has been proposed. Contrary to [63], the proposed technique is based on dividing the legitimate range into two subsets; legitimate subset and illegitimate subset. Moreover, architecture of a FIR filter with error detection and correction capabilities has been also presented in that paper.

The RNS has also been used in communication for many purposes, such as parallel transmitting a set of orthogonal signals [65] and direct sequence spread spectrum [66]. Furthermore, cryptography is another area where RNS can be efficiently used. The major usage of the RNS is with RSA (Rivest, Shamir and Adleman) algorithm [67].

## 3 Aims of Dissertation

The main objective of this thesis is, *designing*, *simulation and FPGA implementation of RNS based building blocks for applications in the field of DSP (binary-to-residue converter, residue-to-binary converter, residue adder and residue multiplier).*

Since the RNS results in carry free arithmetic operations and supports high-speed concurrent computations, it will be useful to use RNS-based building blocks for DSP applications.

Therefore, the main objective of this thesis is improving these building blocks by developing new algorithms and improving existing ones. Hence, the aims of this thesis can be categorized as follows,

**Studying different moduli sets**, analyzing the relation between moduli number and the dynamic range it provides, and evaluating the most efficient ones for different applications with different dynamic range requirements.

**Improving and designing novel RNS converters** including both forward and reverse converters. However, the main focus will be concentrated on the reverse converters, since they are the most time and hardware consuming components in the RNS. Comparing ROM-based structures with combinational ones and analyzing the most suitable converters for different applications based on FPGA implementation.

**Improving and designing novel structures of residue arithmetic units** including modular adders, modular subtractors and modular multipliers with respect to different moduli sets.

**Suggesting solutions to simplify RNS difficult operations** needed in some DSP applications; such as comparison, overflow and sign detection.

**Comparing RNS-based applications with binary-based ones** and analyzing the cases when using the RNS will be the most efficient.

**Verifying the functionality and efficiency of the proposed designs** and comparing them against other published ones based on FPGA implementation.

### **4** Dissertation Results

This part of the thesis is devoted for presenting the proposed work, findings and results of the doctoral dissertation. In addition to the proposed designs, comparisons of known structures with their analyzing and evaluations are also presented in this Chapter.

Before beginning, aspects that have been taken into account during my research are presented below.

Blocks within the proposed designs have been described using VHDL. ROMs and RAMs have been designed using Xilinx core generator v. 13.4. The proposed designs were simulated using Xilinx ModelSim tool and implemented on different FPGA boards. The maximum frequencies and power consumptions were calculated using Xilinx Timing Analyzer and XPower Analyzer tools v. 13.4. The hardware consumptions are the ones shown in the post place and route reports in Xilinx ISE v. 13.4. The design main goal and strategy was mostly set to "balanced". The individual cases, when other strategies were adopted, are specifically mentioned.

Most of the designs were implemented on FPGA boards. However, for the sake of a fair comparison, the unit gate model was sometimes adopted [75], [76], [81] and [82]. Thus, the considerations that have been taken into account concerning the unit gate model are illustrated in the appendix in Tab. 6.1.

#### 4.1 The most efficient moduli set for each dynamic range

In this section, a study on the effect of the moduli number in a moduli set on the overall speed of the RNS is presented. Choosing a proper moduli set greatly affects the performance of the whole system. The widely known issue is that as the number of moduli increases the speed of the residue arithmetic units increases, whereas the residue-to-binary converters become slower and more complex. It is a double-edged sword, since the greater this number is, the faster residue arithmetic units are and more complex and difficult reverse converters to design. Thus, I carried out a detailed study on different moduli sets with different moduli numbers and different dynamic ranges, and compared timing performance of systems based on them in order to determine the moduli number effect on the overall RNS timing performance and find out the most efficient set for each dynamic range. Timing performance of the reverse converters and residue arithmetic units based on three precise DRs, (12 bits (medium DR), 24 bits (large DR) and 60 bits (very large DR)) is compared, and the most efficient and inefficient set for each DR is evaluated. For the sake of a fair comparison, the unit gate model is adopted. Furthermore, I have used same basic blocks among all designs (e.g. adders and multipliers).